| LTR                                                                                                                                                   |                                                                                              |                                                         |                                                                  |                                                                        |                                                 |                                                                                |                                                             | F                                            | REVISI                        | ONS                                         |                            |                                             |                                                |                                                           |                                           |                                          |                                                     |                              |                     |               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------|-------------------------------|---------------------------------------------|----------------------------|---------------------------------------------|------------------------------------------------|-----------------------------------------------------------|-------------------------------------------|------------------------------------------|-----------------------------------------------------|------------------------------|---------------------|---------------|

|                                                                                                                                                       |                                                                                              |                                                         |                                                                  |                                                                        | Γ                                               | DESCR                                                                          | IPTIO                                                       | N                                            |                               |                                             |                            |                                             | C                                              | DATE (                                                    | YR-MO-D                                   | A)                                       |                                                     | APPR                         | OVED                |               |

| A                                                                                                                                                     | to ta<br>pulse<br>max<br>limit                                                               | ble I: (<br>e width<br>limit fre                        | Dutput<br>, PW <sub>IR</sub><br>om (t <sub>cy</sub> ,<br>05.5 to | o refere<br>low vo<br>$_{Q}$ , char<br>$_{c}$ + 320<br>o 95.5.<br>out. | ltage, o<br>nged ur<br>00) to                   | change<br>hit from<br>(t <sub>cvc</sub> + 4                                    | d l <sub>o∟</sub> fr<br>i ns to<br>i0000)                   | om -1.0<br>t <sub>cyc</sub> ; coi<br>; delay | 6 mA to<br>nversio<br>time, t | o 1.6 m<br>on time,<br><sub>ASED</sub> , ch | A; inte<br>chang<br>nangeo | errupt<br>ged                               |                                                | 92-1                                                      | 2-04                                      |                                          | M                                                   | onica L                      | Poelk               | ing           |

| В                                                                                                                                                     | Upda<br>char                                                                                 | ate boil                                                | lerplate<br>roughc                                               | e to the<br>out                                                        | requir<br>TVN                                   | ements                                                                         | s of MI                                                     | L-PRF-                                       | -38535                        | . Edito                                     | rial                       |                                             |                                                | 02-0                                                      | )2-15                                     |                                          | Т                                                   | homas                        | M. He               | SS            |

| С                                                                                                                                                     | Upda                                                                                         | ate boil                                                | lerplate                                                         | e to cur                                                               | rent M                                          | IL-PRF                                                                         | -3853                                                       | 5 requi                                      | rement                        | is C                                        | FS                         |                                             |                                                | 08-0                                                      | 01-09                                     |                                          | Т                                                   | homas                        | M. He               | SS            |

|                                                                                                                                                       |                                                                                              |                                                         |                                                                  |                                                                        |                                                 |                                                                                |                                                             |                                              |                               |                                             |                            |                                             |                                                |                                                           |                                           |                                          |                                                     |                              |                     |               |

|                                                                                                                                                       |                                                                                              |                                                         |                                                                  | 1                                                                      | I                                               | I                                                                              |                                                             |                                              | I                             | I                                           |                            | I                                           | I                                              | 1                                                         | 1                                         |                                          |                                                     | 1                            | 1                   |               |

| REV                                                                                                                                                   |                                                                                              |                                                         |                                                                  |                                                                        |                                                 |                                                                                |                                                             |                                              |                               |                                             |                            |                                             |                                                |                                                           |                                           |                                          |                                                     |                              |                     |               |

| SHEET                                                                                                                                                 |                                                                                              |                                                         |                                                                  |                                                                        |                                                 |                                                                                |                                                             |                                              |                               |                                             |                            |                                             |                                                |                                                           |                                           |                                          |                                                     |                              |                     |               |

| SHEET<br>REV                                                                                                                                          | C 15                                                                                         | C 16                                                    | C 17                                                             | C 18                                                                   | C 19                                            | C 20                                                                           | C 21                                                        | C 22                                         | C 23                          | C 24                                        | C 25                       | C 26                                        | C 27                                           | C 28                                                      | C 29                                      | C 30                                     | C 31                                                | C 32                         | C 33                | C 34          |

| SHEET                                                                                                                                                 | 15                                                                                           | C<br>16                                                 | C<br>17                                                          | C<br>18<br>RE\                                                         | 19                                              | C<br>20                                                                        | C<br>21<br>C                                                | C<br>22<br>C                                 | C<br>23<br>C                  | C<br>24<br>C                                | C<br>25<br>C               | C<br>26<br>C                                | C<br>27<br>C                                   | C<br>28<br>C                                              | C<br>29<br>C                              | C<br>30<br>C                             | C<br>31<br>C                                        | C<br>32<br>C                 | C<br>33<br>C        | C<br>34<br>C  |

| SHEET<br>REV<br>SHEET                                                                                                                                 | 15                                                                                           |                                                         | -                                                                | 18                                                                     | 19<br>/                                         |                                                                                | 21                                                          | 22                                           | 23                            | 24                                          | 25                         | 26                                          | 27                                             | 28                                                        | 29                                        | 30                                       | 31                                                  | 32                           | 33                  | 34            |

| SHEET<br>REV<br>SHEET<br>REV STATUS                                                                                                                   | 15                                                                                           |                                                         | -                                                                | 18<br>RE\<br>SHE                                                       | 19<br>/                                         | 20<br>D BY                                                                     | 21<br>C                                                     | 22<br>C                                      | 23<br>C                       | 24<br>C                                     | 25<br>C<br>5               | 26<br>C<br>6<br>EFEN                        | 27<br>C<br>7<br>SE S                           | 28<br>C<br>8<br>UPPL                                      | 29<br>C<br>9<br>Y CE                      | 30<br>C<br>10<br>NTER                    | 31<br>C<br>11                                       | 32<br>C<br>12                | 33<br>C<br>13       | 34<br>C       |

| SHEET<br>REV<br>SHEET<br>REV STATUS<br>OF SHEETS<br>PMIC N/A<br>STA                                                                                   | 15<br>S<br>NDA                                                                               | 16<br>RD                                                | 17                                                               | 18<br>RE\<br>SHE<br>PRE                                                | 19<br>/<br>ET                                   | 20<br>D BY<br>Tim F<br>BY                                                      | 21<br>C<br>1                                                | 22<br>C                                      | 23<br>C                       | 24<br>C                                     | 25<br>C<br>5               | 26<br>C<br>6<br>EFEN                        | 27<br>C<br>7<br>SE S<br>OLUM                   | 28<br>C<br>8<br>UPPL                                      | 29<br>C<br>9<br>Y CE<br>OHIO              | 30<br>C<br>10<br>NTER                    | 31<br>C<br>11<br>218-39                             | 32<br>C<br>12                | 33<br>C<br>13       | 34<br>C       |

| SHEET<br>REV<br>SHEET<br>REV STATUS<br>OF SHEETS<br>PMIC N/A                                                                                          |                                                                                              | 16<br>RD<br>CUIT<br>IG                                  | 17                                                               | 18<br>RE\<br>SHE<br>PRE<br>CHE                                         | 19<br>/<br>EET<br>PAREI                         | 20<br>D BY<br>Tim H<br>BY<br>Tim H                                             | 21<br>C<br>1<br>I. Noh                                      | 22<br>C<br>2                                 | 23<br>C                       | 24<br>C<br>4                                | 25<br>C<br>5<br>D          | 26<br>C<br>6<br>EFEN<br>C(                  | 27<br>C<br>7<br>SE SI<br>DLUM<br>http          | 28<br>C<br>8<br>UPPL<br>IBUS,<br>p://ww                   | 29<br>C<br>9<br>.Y CE<br>, OHIC<br>, W.ds | 30<br>C<br>10<br>NTER<br>D 432<br>cc.dla | 31<br>C<br>11<br>218-39<br>a.mil                    | 32<br>C<br>12<br>UMBI<br>990 | 33<br>C<br>13<br>US | 34<br>C<br>14 |

| SHEET<br>REV<br>SHEET<br>REV STATUS<br>OF SHEETS<br>PMIC N/A<br>PMIC N/A<br>STA<br>MICRO<br>DRAWI<br>FOR L                                            | 15<br>S<br>NDA<br>DCIR<br>AWIN<br>NG IS A<br>JSE BY<br>RTMEN                                 | 16<br>RD<br>CUIT<br>IG<br>AVAILA<br>ALL<br>VTS          | BLE                                                              | 18<br>RE\<br>SHE<br>PRE<br>CHE                                         | 19<br>/<br>EET<br>PAREI<br>CKED<br>ROVE         | 20<br>D BY<br>Tim H<br>BY<br>Tim H<br>D BY<br>liam K.                          | 21<br>C<br>1<br>I. Noh<br>I. Noh                            | 22<br>C<br>2                                 | 23<br>C                       | 24<br>C<br>4                                | 25<br>C<br>5<br>D          | 26<br>C<br>6<br>EFEN<br>C(                  | 27<br>C<br>7<br>SE SI<br>DLUM<br>http          | 28<br>C<br>8<br>UPPL<br>IBUS,<br>p://ww                   | 29<br>C<br>9<br>.Y CE<br>, OHIC<br>, W.ds | 30<br>C<br>10<br>NTER<br>D 432<br>cc.dla | 31<br>C<br>11<br>C<br>C<br>218-39<br>a.mil          | 32<br>C<br>12<br>UMBI<br>990 | 33<br>C<br>13<br>US | 34<br>C<br>14 |

| SHEET<br>REV<br>SHEET<br>REV STATUS<br>OF SHEETS<br>PMIC N/A<br>PMIC N/A<br>STA<br>MICRO<br>DRAWI<br>FOR U                                            | 15<br><b>NDA</b><br><b>DCIR</b><br><b>AWIN</b><br>NG IS <i>P</i><br>JSE BY<br>RTMEN<br>NCIES | 16<br>RD<br>CUIT<br>IG<br>AVAILA<br>ALL<br>NTS<br>OF TH | BLE<br>E                                                         | 18<br>RE\<br>SHE<br>PRE<br>CHE<br>APP<br>DRA                           | 19<br>/<br>EET<br>PAREI<br>CKED<br>ROVEI<br>Wil | 20<br>D BY<br>Tim H<br>BY<br>Tim H<br>D BY<br>liam K.                          | 21<br>C<br>1<br>I. Noh<br>I. Noh<br>. Heckr<br>OVAL<br>0-11 | 22<br>C<br>2                                 | 23<br>C                       | 24<br>C<br>4<br>MIC<br>MIC<br>SIZE          | 25<br>C<br>5<br>D          | 26<br>C<br>6<br>EFEN<br>CO<br>IRCUI         | 27<br>C<br>7<br>SE SI<br>DLUW<br>http<br>ROLUE | 28<br>C<br>8<br>UPPL<br>IBUS,<br>p://ww<br>GITAL<br>ER, M | 29<br>C<br>9<br>.Y CE<br>, OHIC<br>, W.ds | 30<br>C<br>10<br>NTER<br>D 432<br>cc.dla | 31<br>C<br>11<br>218-39<br>a.mil<br>EED (<br>C SILI | 32<br>C<br>12<br>UMBI<br>990 | 33<br>C<br>13<br>US | 34<br>C<br>14 |

| SHEET<br>REV<br>SHEET<br>REV STATUS<br>OF SHEETS<br>PMIC N/A<br>PMIC N/A<br>STA<br>MICRO<br>DRA<br>THIS DRAWI<br>FOR U<br>DEPA<br>AND AGE<br>DEPARTME | 15<br><b>NDA</b><br><b>DCIR</b><br><b>AWIN</b><br>NG IS <i>P</i><br>JSE BY<br>RTMEN<br>NCIES | 16<br>RD<br>CUIT<br>IG<br>ALL<br>NTS<br>OF TH<br>DEFEN  | BLE<br>E                                                         | 18<br>RE\<br>SHE<br>PRE<br>CHE<br>APP<br>DRA                           | 19<br>/<br>EET<br>PAREI<br>CKED<br>ROVEI<br>Wil | 20<br>D BY<br>Tim H<br>BY<br>Tim H<br>D BY<br>liam K.<br>APPR<br>90-1<br>LEVEL | 21<br>C<br>1<br>I. Noh<br>I. Noh<br>. Heckr<br>OVAL<br>0-11 | 22<br>C<br>2                                 | 23<br>C                       | 24<br>C<br>4<br>MIC<br>MIC                  | 25<br>C<br>5<br>D          | 26<br>C<br>6<br>EFEN<br>CC<br>IRCUI<br>ONTF | 27<br>C<br>7<br>SE SI<br>DLUM<br>http          | 28<br>C<br>8<br>UPPL<br>IBUS,<br>p://ww<br>GITAL<br>ER, M | 29<br>C<br>9<br>Y CE<br>, OHIC<br>/w.ds   | 30<br>C<br>10<br>NTER<br>D 432<br>cc.dla | 31<br>C<br>11<br>218-39<br>a.mil<br>EED (<br>C SILI | 32<br>C<br>12<br>UMBI<br>990 | 33<br>C<br>13<br>US | 34<br>C<br>14 |

#### 1. SCOPE

1.1 <u>Scope</u>. This drawing describes device requirements for MIL-STD-883 compliant, non-JAN class level B microcircuits in accordance with MIL-PRF-38535, appendix A.

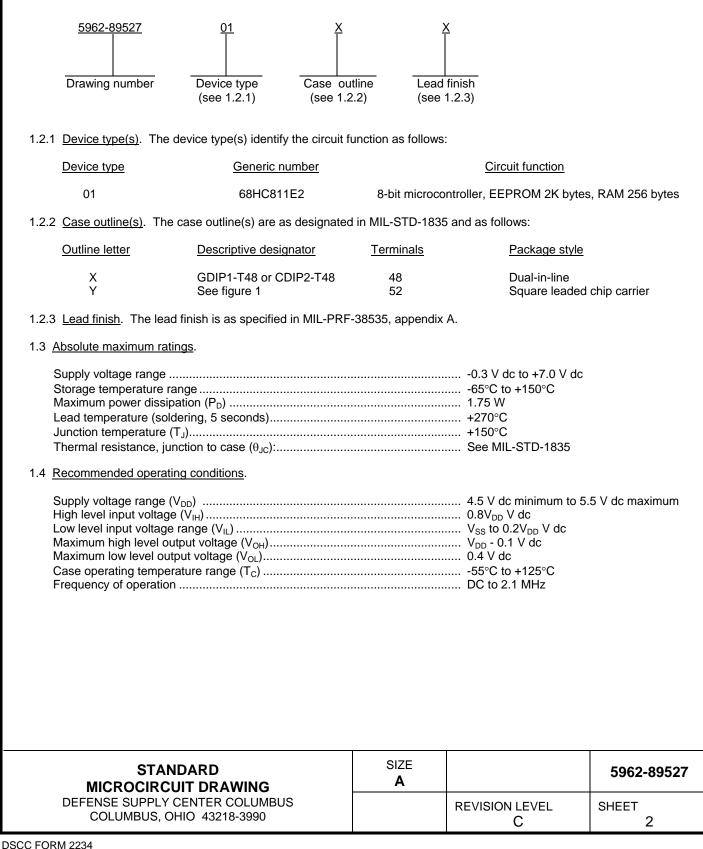

1.2 Part or Identifying Number (PIN). The complete PIN is as shown in the following example:

## 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbooks</u>. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

#### DEPARTMENT OF DEFENSE SPECIFICATION

MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for.

DEPARTMENT OF DEFENSE STANDARDS

| MIL-STD-883  | - | Test Method Standard Microcircuits.                    |

|--------------|---|--------------------------------------------------------|

| MIL-STD-1835 | - | Interface Standard Electronic Component Case Outlines. |

DEPARTMENT OF DEFENSE HANDBOOKS

| MIL-HDBK-103 | - | List o | of S | tar | ndard | Mic | rc | ociro | cuit | Drawings. |  |

|--------------|---|--------|------|-----|-------|-----|----|-------|------|-----------|--|

|              |   |        |      |     |       |     |    |       |      |           |  |

MIL-HDBK-780 - Standard Microcircuit Drawings.

(Copies of these documents are available online at <u>http://assist.daps.dla.mil/quicksearch/</u> or <u>http://assist.daps.dla.mil</u> or from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

## 3. REQUIREMENTS

3.1 <u>Item requirements</u>. The individual item requirements shall be in accordance with MIL-PRF-38535, appendix A for non-JAN class level B devices and as specified herein. Product built to this drawing that is produced by a Qualified Manufacturer Listing (QML) certified and qualified manufacturer or a manufacturer who has been granted transitional certification to MIL-PRF-38535 may be processed as QML product in accordance with the manufacturers approved program plan and qualifying activity approval in accordance with MIL-PRF-38535. This QML flow as documented in the Quality Management (QM) plan may make modifications to the requirements herein. These modifications shall not affect form, fit, or function of the device. These modifications shall not affect the PIN as described herein. A "Q" or "QML" certification mark in accordance with MIL-PRF-38535 is required to identify when the QML flow option is used.

3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535, appendix A and herein.

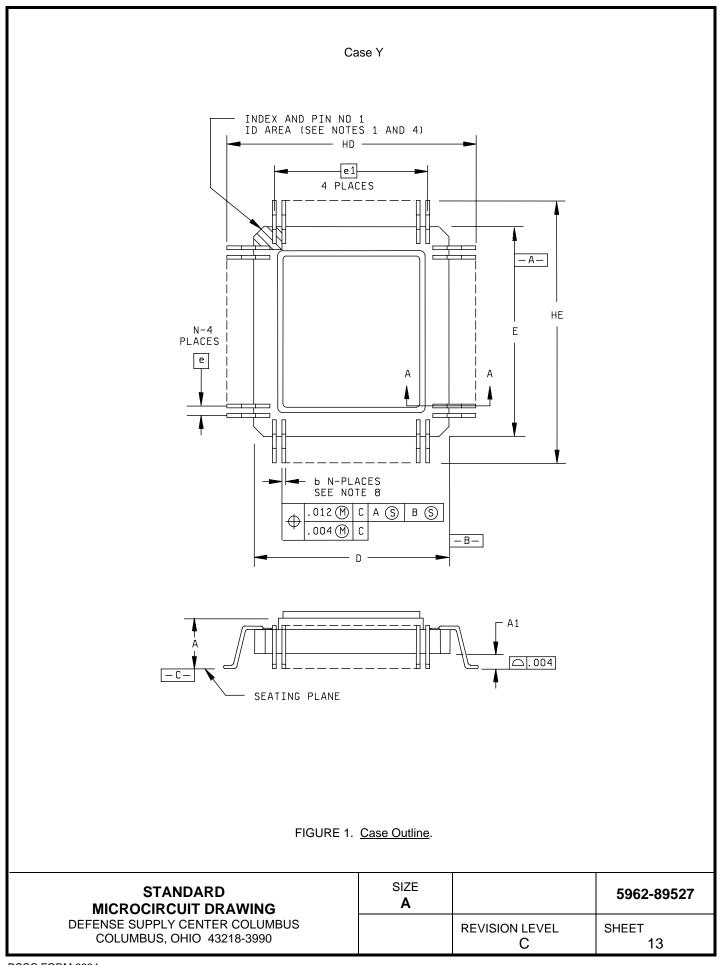

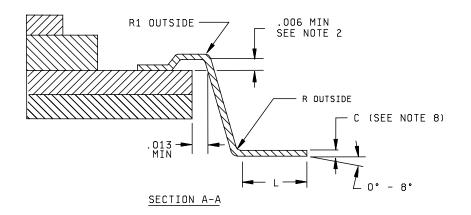

3.2.1 <u>Case outlines</u>. The case outlines shall be in accordance with 1.2.2 herein and on figure 1.

3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 2.

3.2.3 Block diagram. The block diagram shall be as specified on figure 3.

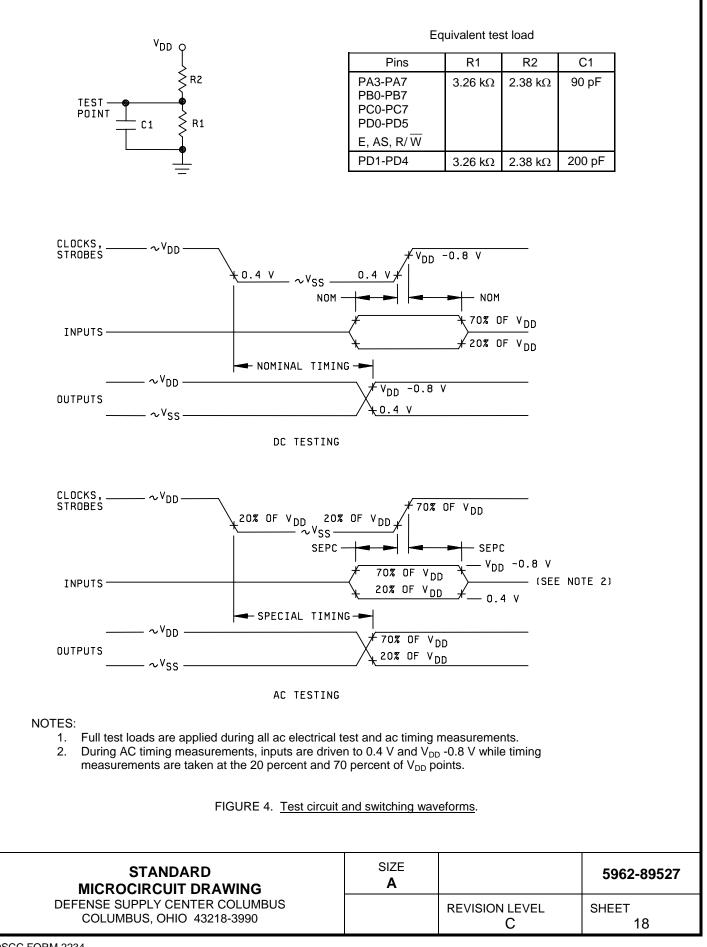

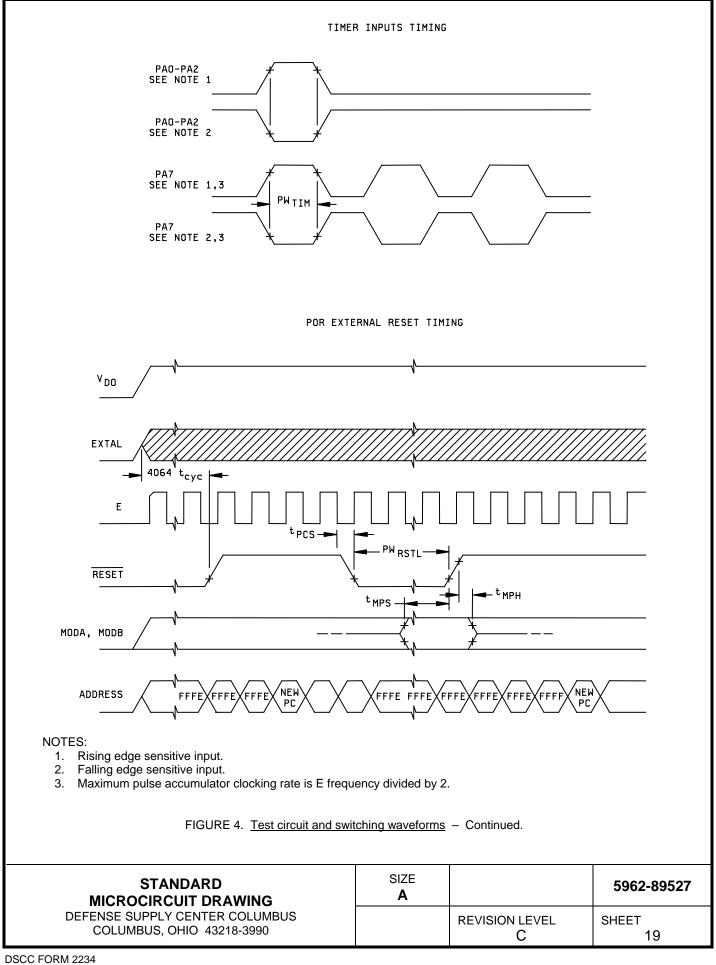

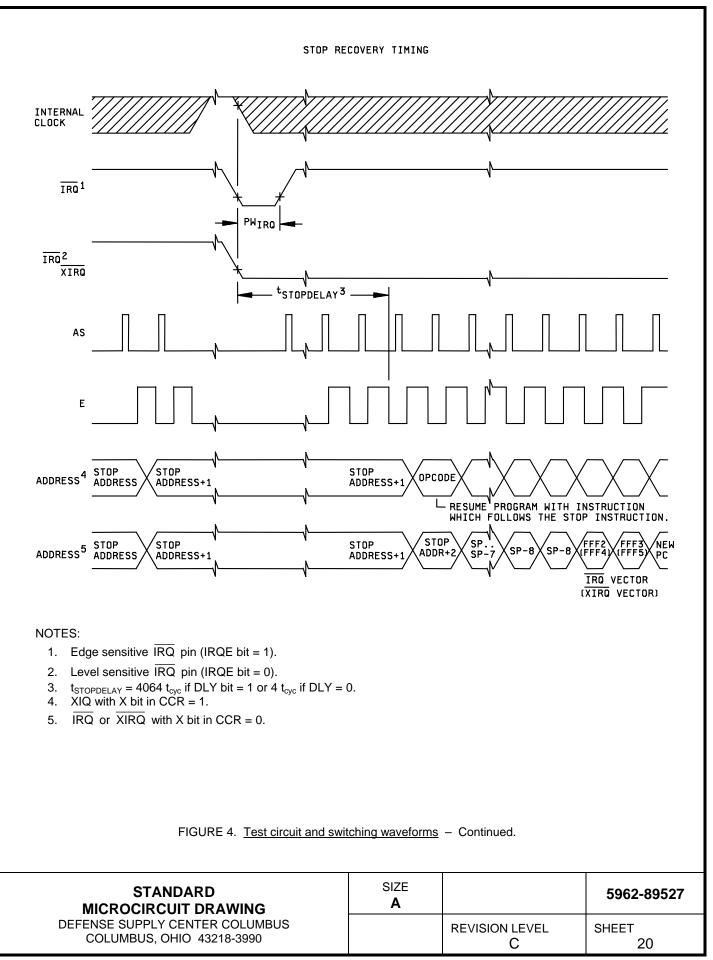

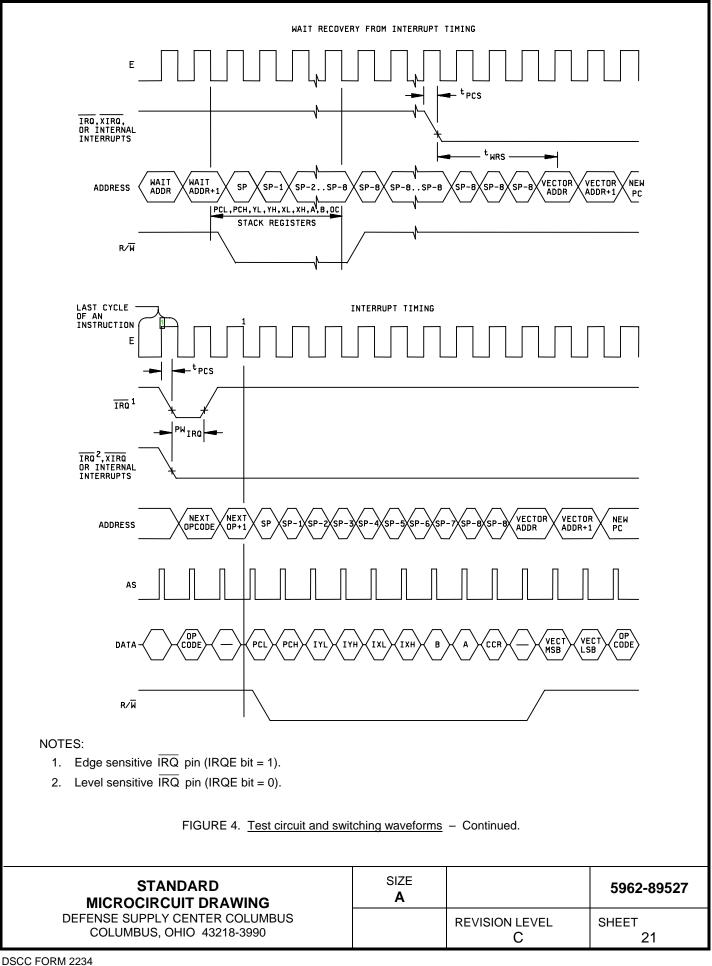

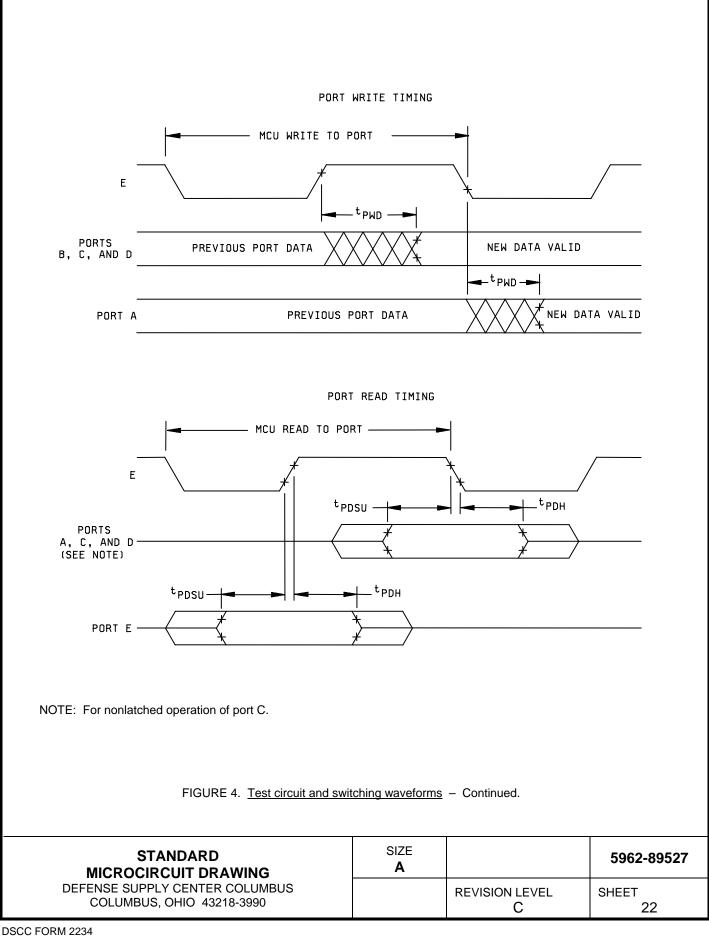

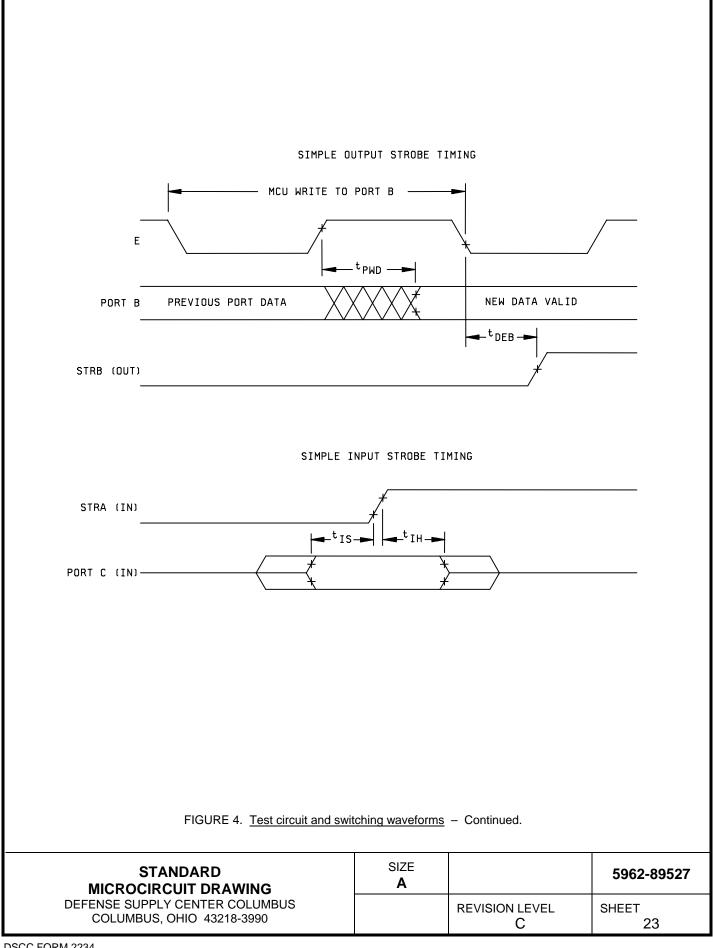

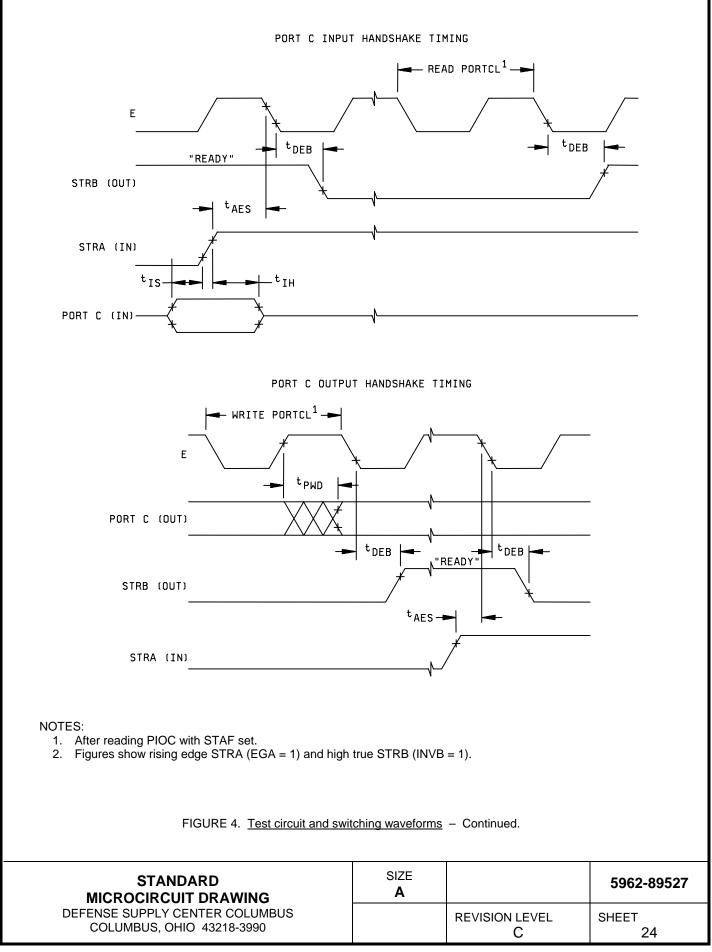

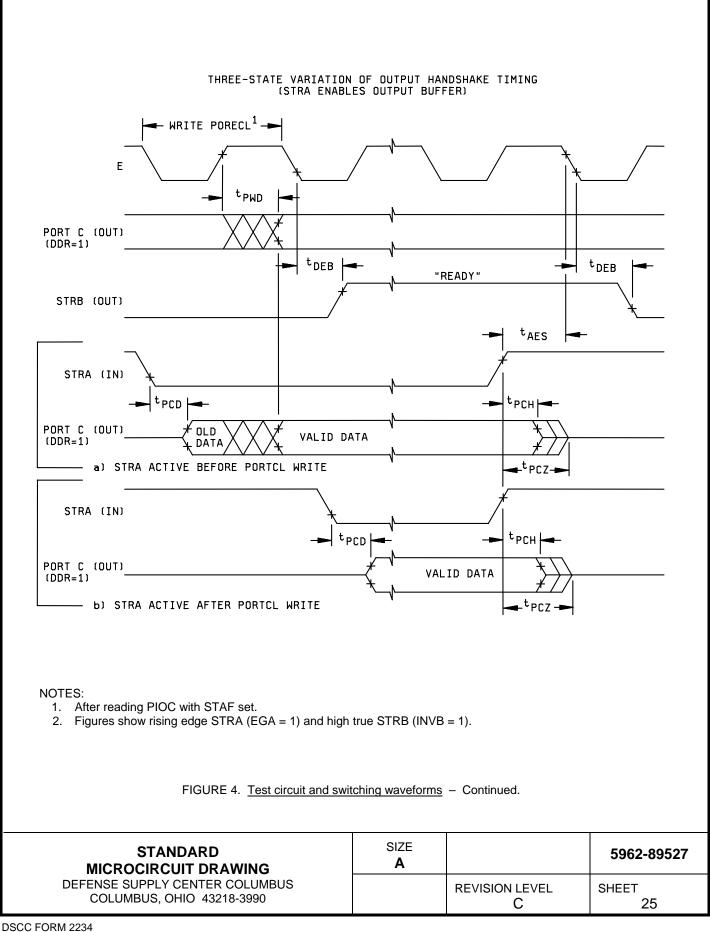

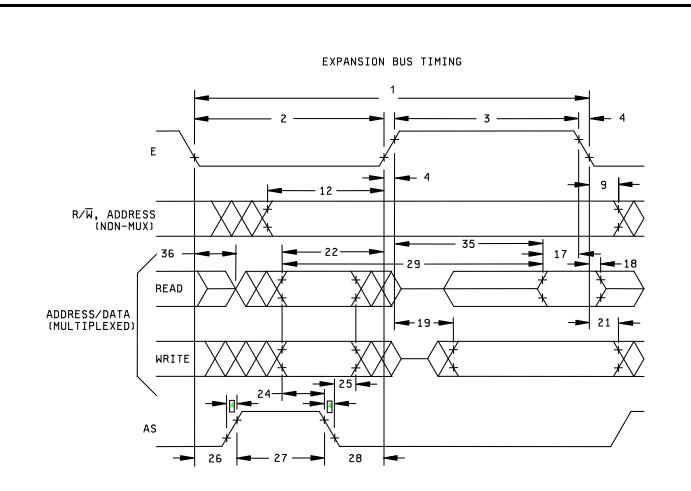

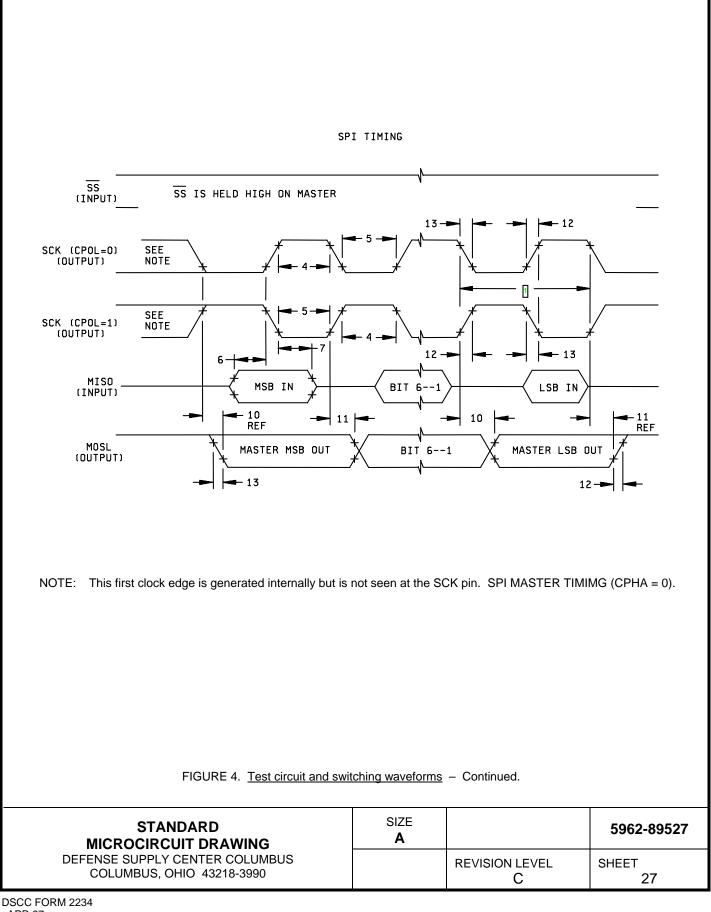

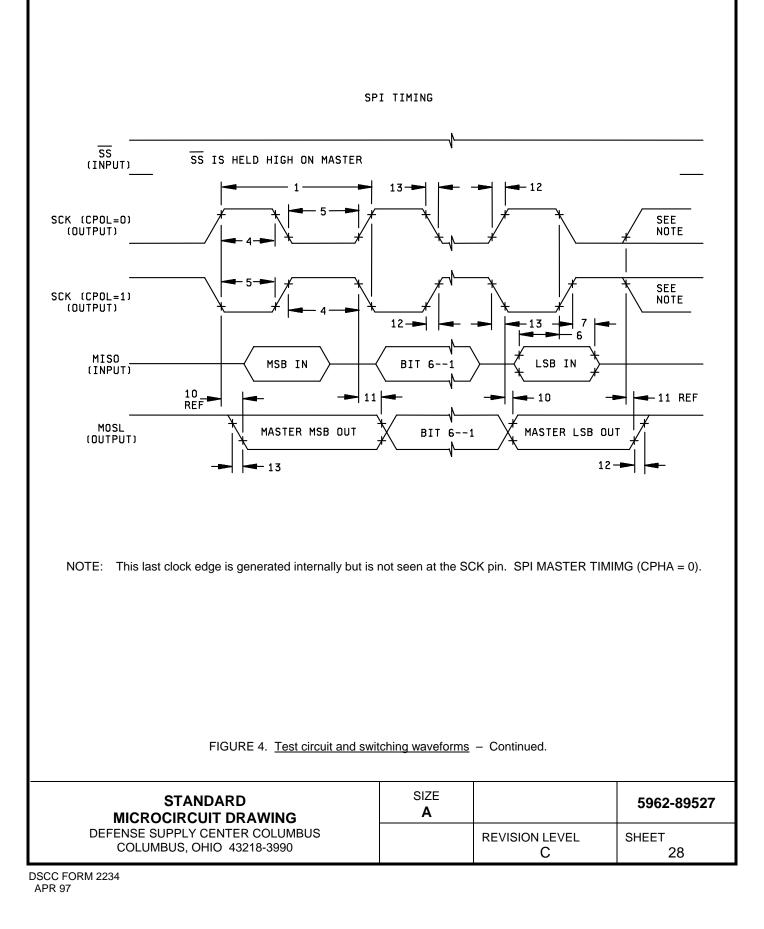

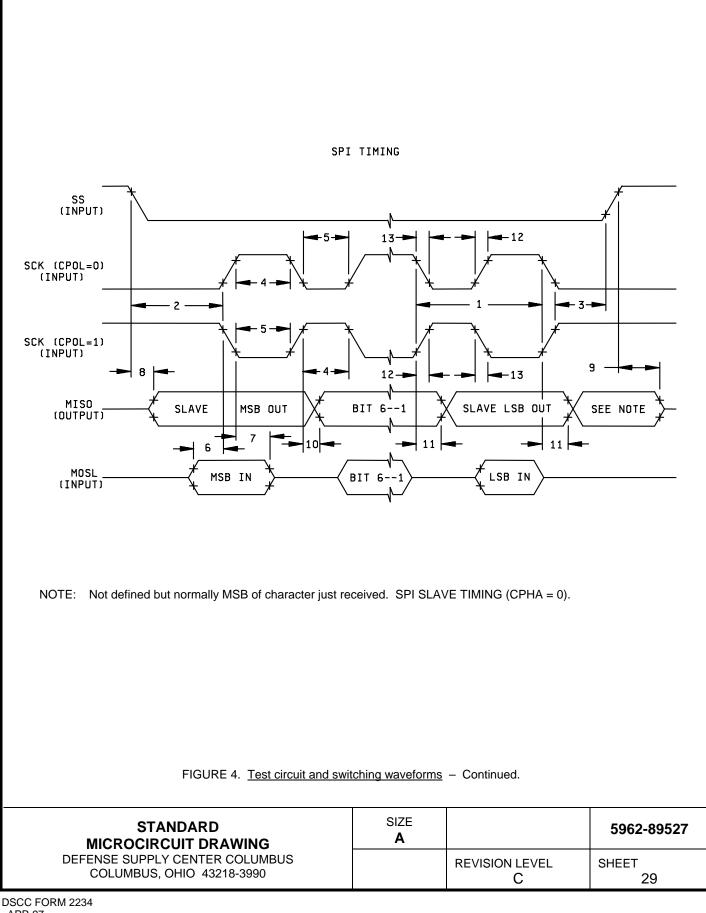

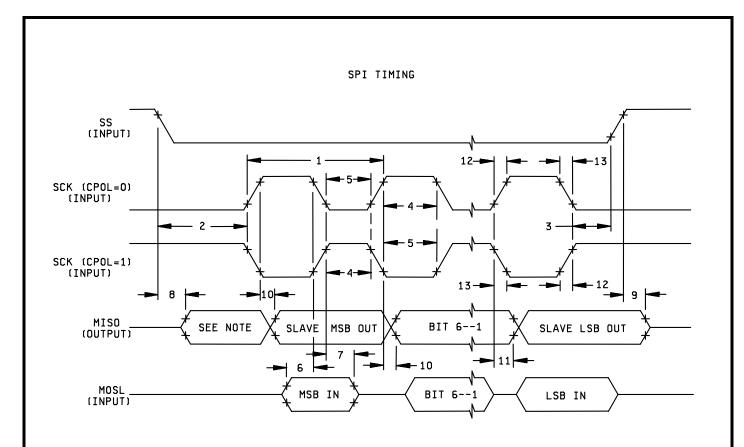

3.2.4 <u>Test circuit and switching waveforms</u>. The test circuit and switching waveforms shall be as specified on figure 4.

3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and shall apply over the full case operating temperature range.

3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are described in table I.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-89527 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |                  | C              | 3          |

3.5 <u>Marking</u>. Marking shall be in accordance with MIL-PRF-38535, appendix A. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked. For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device.

3.5.1 <u>Certification/compliance mark</u>. A compliance indicator "C" shall be marked on all non-JAN devices built in compliance to MIL-PRF-38535, appendix A. The compliance indicator "C" shall be replaced with a "Q" or "QML" certification mark in accordance with MIL-PRF-38535 to identify when the QML flow option is used.

3.6 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-HDBK-103 (see 6.7 herein). The certificate of compliance submitted to DSCC-VA prior to listing as an approved source of supply shall affirm that the manufacturer's product meets the requirements of MIL-PRF-38535, appendix A and the requirements herein.

3.7 <u>Certificate of conformance</u>. A certificate of conformance as required in MIL-PRF-38535, appendix A shall be provided with each lot of microcircuits delivered to this drawing.

3.8 Notification of change. Notification of change to DSCC-VA shall be required for any change that affects this drawing.

3.9 <u>Verification and review</u>. DSCC, DSCC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

3.10 <u>Processing EEPROMS</u>. All testing requirements and quality assurance provisions herein shall be satisfied by the manufacturer prior to delivery.

3.10.1 <u>Erasure of EEPROM</u>. When specified, devices shall be erased in accordance with the procedures and characteristics specified in 4.4.

3.10.2 <u>Programmability of EEPROM</u>. When specified, devices shall be programmed to the specified pattern using the procedures and characteristics specified in 4.5.

3.10.3 <u>Verification of erasure or programmability of EEPROM</u>. When specified, devices shall be verified as either programmed to the specified pattern or erased. As a minimum, verification shall consist of performing a functional test (subgroup 7) to verify that all bits are in the proper state. Any bit that does not verify to be in the proper state shall constitute a device failure, and shall be removed from the lot.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-89527 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |                  | C              | 4          |

|                                                                                           | TABLE                                                      | I. <u>Electric</u> | cal performance character                                                                                                                               | istics.              |                      |                 |          |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|-----------------|----------|

|                                                                                           | Test                                                       | Symbol             | $\begin{array}{c} \text{Conditions} \\ \text{+4.5 V} \leq \text{V}_{\text{DD}} \leq \text{+5.5 V} \\ \text{V}_{\text{SS}} = 0 \text{ V dc} \end{array}$ | Group A<br>subgroups |                      | nits            | Unit     |

|                                                                                           |                                                            |                    | $-55^{\circ}C \le T_C \le +125^{\circ}C$                                                                                                                |                      | Min                  | Max             |          |

| Output high voltage<br>RESET , XTAL, a                                                    |                                                            | V <sub>OH</sub>    | $I_{OH} = -0.8 \text{ mA}$<br>$V_{DD} = 4.5 \text{ V} \underline{1}/$                                                                                   | 1, 2, 3              | V <sub>DD</sub> -0.8 |                 | V        |

| Output low voltage;                                                                       | all outputs except XTAL                                    | V <sub>OL</sub>    | I <sub>OL</sub> = 1.6 mA<br>V <sub>DD</sub> = 4.5 V                                                                                                     | 1, 2, 3              |                      | 0.4             | V        |

| Input high voltage                                                                        | All inputs except<br>RESET                                 | V <sub>IH</sub>    | V <sub>DD</sub> = 4.5 V                                                                                                                                 | 1, 2, 3              | 0.7V <sub>DD</sub>   | V <sub>DD</sub> | V        |

|                                                                                           | RESET                                                      |                    |                                                                                                                                                         |                      | $0.8V_{DD}$          | V <sub>DD</sub> |          |

| Input low voltage; a                                                                      | II inputs                                                  | V <sub>IL</sub>    | V <sub>DD</sub> = 4.5 V                                                                                                                                 | 1, 2, 3              | V <sub>SS</sub>      | $0.2V_{DD}$     | V        |

| I/O port, three-state leakage,<br>PA3, PA7, PC0-PC7, PD0-PD5, AS/STRA,<br>MODA/LIR, RESET |                                                            | I <sub>oz</sub>    | $V_{DD} = 5.5 V$ $V_{IN} = V_{IH} \text{ or } V_{IL}$                                                                                                   | 1, 2, 3              |                      | ±10             | μΑ       |

| Input current                                                                             |                                                            |                    | $V_{DD} = 5.5 V$<br>$V_{IN} = V_{DD} \text{ or } V_{SS}$                                                                                                | 1, 2, 3              |                      | ±1              | μA       |

|                                                                                           | MODB/V <sub>stby</sub>                                     |                    | $\underline{2}$                                                                                                                                         |                      |                      | ±10             |          |

| RAM standby voltage powerdown                                                             |                                                            | V <sub>SB</sub>    |                                                                                                                                                         | 1, 2, 3              | 4.0                  | V <sub>DD</sub> | V        |

| RAM standby curre                                                                         | RAM standby current powerdown                              |                    |                                                                                                                                                         | 1, 2, 3              |                      | 20              | μΑ       |

| Total supply current                                                                      | RUN:                                                       | I <sub>DD</sub>    | $V_{DD} = 5.5 V$<br>Single chip                                                                                                                         | 1, 2, 3              |                      | 20              | mA       |

| <u>3</u> /                                                                                |                                                            |                    | $V_{DD} = 5.5 V$<br>Expanded multiplexed                                                                                                                |                      |                      | 30              |          |

|                                                                                           | WAIT:<br>All peripheral functions                          | WI <sub>DD</sub>   | $V_{DD} = 5.5 V$<br>Single chip                                                                                                                         | 1, 2, 3              |                      | 10              | mA       |

|                                                                                           | shut down                                                  |                    | $V_{DD} = 5.5 V$<br>Expanded multiplexed                                                                                                                |                      |                      | 15              |          |

|                                                                                           | STOP:<br>No clocks                                         | SI <sub>DD</sub>   | $V_{DD} = 5.5 V$<br>Single chip                                                                                                                         | 1, 2, 3              |                      | 300             | μA       |

| Input capacitance                                                                         | PA0-PA2, PE0-PE7,<br>EXTAL, IRQ , XIRQ                     | C <sub>IN</sub>    | $V_{IN} = 0 V$<br>$f_{IN} = 1 MHz$<br>See 4.3.1b                                                                                                        | 4                    |                      | 8               | pF       |

|                                                                                           | PA7, PA3, PC0-PC7,<br>PD0-PD5, AS/STRA,<br>MODA/LIR, RESET |                    |                                                                                                                                                         |                      |                      | 14              |          |

| Functional test                                                                           |                                                            |                    | V <sub>DD</sub> = 4.5 V, 5.5 V                                                                                                                          | 7, 8                 |                      |                 |          |

| See footnotes at er                                                                       | d of table.                                                | 1                  | 1                                                                                                                                                       |                      | 1                    | 1               | <u> </u> |

| місе                                                                                      | STANDARD<br>ROCIRCUIT DRAWING                              | 2                  | SIZE<br>A                                                                                                                                               |                      |                      | 5962-8          | 39527    |

| DEFENSE                                                                                   | SUPPLY CENTER COLUM<br>JMBUS, OHIO 43218-3990              | <b>IBUS</b>        |                                                                                                                                                         | REVISION LEVE<br>C   | iL                   | SHEET<br>5      |          |

| SCC FORM 2234                                                                             |                                                            |                    |                                                                                                                                                         |                      | 1                    |                 |          |

|                               | Test                               | Symbol             | $\begin{array}{c} \text{Condit} \\ \text{+4.5 V} \leq \text{V}_{\text{D}} \end{array}$ | <sub>D</sub> ≤ <b>+</b> 5.5 V | Group A<br>subgroups | Lim    | nits | Unit             |

|-------------------------------|------------------------------------|--------------------|----------------------------------------------------------------------------------------|-------------------------------|----------------------|--------|------|------------------|

|                               |                                    |                    | $\label{eq:VSS} \begin{array}{l} V_{SS} = 0 \\ -55^{\circ}C \leq T_{C} \end{array}$    |                               |                      | Min    | Max  |                  |

|                               |                                    | Ċ                  | Control timing                                                                         |                               |                      |        |      | •                |

| Frequency of operati          | on                                 | f <sub>o</sub>     | V <sub>DD</sub> = 4.5 V                                                                | 1.0 MHz                       | 9, 10, 11            | 0      | 1.0  | MHz              |

|                               |                                    |                    | See figure 4.                                                                          | 2.1 MHz                       |                      | 0      | 2.1  |                  |

| E clock period                |                                    | t <sub>cyc</sub>   |                                                                                        | 1.0 MHz                       | 9, 10, 11            | 1000.0 |      | ns               |

|                               |                                    |                    |                                                                                        | 2.1 MHz                       |                      | 476.0  |      |                  |

| Crystal frequency             |                                    | f <sub>XTAL</sub>  |                                                                                        | 1.0 MHz                       | 9, 10, 11            |        | 4.0  | MHz              |

|                               |                                    |                    |                                                                                        | 2.1 MHz                       |                      |        | 8.4  |                  |

| External oscillator frequency |                                    | f <sub>OEX</sub>   |                                                                                        | 1.0 MHz                       | 9, 10, 11            | 0      | 4.0  | MHz              |

|                               |                                    |                    |                                                                                        | 2.1 MHz                       |                      | 0      | 8.4  |                  |

| Processor control setup       |                                    | t <sub>PCS</sub>   |                                                                                        | 1.0 MHz                       | 9, 10, 11            | 200.0  |      | ns               |

|                               |                                    |                    |                                                                                        | 2.1 MHz                       |                      | 69.0   |      |                  |

| Reset input pulse             | To guarantee external              | PW <sub>RSTL</sub> |                                                                                        | 1.0 MHz                       | 9, 10, 11            | 8.0    |      | t <sub>cyc</sub> |

| width                         | reset vector <u>4</u> /            |                    |                                                                                        | 2.1 MHz                       |                      | 8.0    |      |                  |

|                               | Minimum input time                 |                    |                                                                                        | 1.0 MHz                       | 9, 10, 11            | 1.0    |      |                  |

|                               | may be preempted by internal reset |                    |                                                                                        | 2.1 MHz                       |                      | 1.0    |      |                  |

| Mode programming              | setup time                         | t <sub>MPS</sub>   |                                                                                        | 1.0 MHz                       | 9, 10, 11            | 2.0    |      | t <sub>cyc</sub> |

|                               |                                    |                    |                                                                                        | 2.1 MHz                       |                      | 2.0    |      |                  |

| Mode programming I            | nold time                          | t <sub>MPH</sub>   |                                                                                        | 1.0 MHz                       | 9, 10, 11            | 0.0    |      | ns               |

|                               |                                    |                    |                                                                                        | 2.1 MHz                       |                      | 0.0    |      |                  |

| Interrupt pulse width         | IRQ edge sensitive                 | PWIRQ              |                                                                                        | 1.0 MHz                       | 9, 10, 11            | 2.0    |      | t <sub>cyc</sub> |

| mode                          | 0                                  |                    |                                                                                        | 2.1 MHz                       | -                    | 2.0    |      |                  |

| Wait recovery startur         | o time                             | t <sub>WRS</sub>   |                                                                                        | 1.0 MHz                       | 9, 10, 11            |        | 4.0  | t <sub>cyc</sub> |

|                               |                                    |                    |                                                                                        | 2.1 MHz                       | ]                    |        | 4.0  |                  |

| Timer pulse width inp         | out capture, pulse                 | PW <sub>TIM</sub>  | ]                                                                                      | 1.0 MHz                       | 9, 10, 11            | 1020.0 |      | ns               |

| accumulator input             |                                    |                    |                                                                                        | 2.1 MHz                       |                      | 496.0  |      | 1                |

otrical - 1-~ . . .

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-89527 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |                  | C              | 6          |

|                                                                                     | Test                         | Symbol            | Condi                                                                              |                               | Group A   | Lim    | nits  | Unit |

|-------------------------------------------------------------------------------------|------------------------------|-------------------|------------------------------------------------------------------------------------|-------------------------------|-----------|--------|-------|------|

|                                                                                     |                              |                   | +4.5 V $\leq$ V <sub>D</sub><br>V <sub>SS</sub> = 0<br>-55°C $\leq$ T <sub>C</sub> | V dc                          | subgroups | Min    | Max   |      |

|                                                                                     |                              | Periphe           | eral port timing                                                                   | <u>5</u> /                    |           |        |       |      |

| Frequency of operati                                                                | on (E clock frequency)       | f <sub>o</sub>    | V <sub>DD</sub> = 4.5 V                                                            | 1.0 MHz                       | 9, 10, 11 | 1.0    | 1.0   | MHz  |

|                                                                                     |                              |                   | See figure 4                                                                       | 2.1 MHz                       |           | 2.1    | 2.1   |      |

| E clock period                                                                      |                              | t <sub>cyc</sub>  |                                                                                    | 1.0 MHz                       | 9, 10, 11 | 1000.0 |       | ns   |

|                                                                                     |                              |                   |                                                                                    | 2.1 MHz                       |           | 476.0  |       |      |

| Peripheral data setur                                                               |                              | t <sub>PDSU</sub> |                                                                                    | 1.0 MHz                       | 9, 10, 11 | 100.0  |       | ns   |

| ports A, C, D, and E                                                                | Ξ                            |                   |                                                                                    | 2.1 MHz                       |           | 100.0  |       |      |

| Peripheral data hold                                                                |                              | t <sub>PDH</sub>  |                                                                                    | 1.0 MHz                       | 9, 10, 11 | 50.0   |       | ns   |

| ports A, C, D, and E                                                                | Ξ                            |                   |                                                                                    | 2.1 MHz                       |           | 50.0   |       |      |

| Delay time,<br>peripheral data<br>write MCU write to port A<br>MCU write to port B, |                              | t <sub>PWD</sub>  | 1                                                                                  | 1.0 MHz                       | 9, 10, 11 |        | 175.0 | ns   |

|                                                                                     |                              |                   |                                                                                    | 2.1 MHz                       | z         |        | 175.0 |      |

|                                                                                     |                              |                   |                                                                                    | 1.0 MHz                       | 9, 10, 11 |        | 340.0 |      |

| C, and D                                                                            |                              |                   |                                                                                    | 2.1 MHz                       | -         |        | 209.0 |      |

| Input data setup time                                                               | e (port C)                   | t <sub>IS</sub>   |                                                                                    | 1.0 MHz                       | 9, 10, 11 | 60.0   |       | ns   |

|                                                                                     |                              |                   |                                                                                    | 2.1 MHz                       | -         | 60.0   |       |      |

| Input data hold time                                                                | (port C)                     | t <sub>IH</sub>   |                                                                                    | 1.0 MHz                       | 9, 10, 11 | 100.0  |       | ns   |

|                                                                                     |                              |                   |                                                                                    | 2.1 MHz                       | -         | 100.0  |       |      |

| Delay time, E fall to S                                                             | STRB                         | t <sub>DEB</sub>  |                                                                                    | 1.0 MHz                       | 9, 10, 11 |        | 350.0 | ns   |

|                                                                                     |                              |                   |                                                                                    | 2.1 MHz                       | -         |        | 219.0 |      |

| Setup time, STRA as                                                                 | sserted to E fall <u>6</u> / | t <sub>AES</sub>  |                                                                                    | 1.0 MHz                       | 9, 10, 11 | 0.0    |       | ns   |

|                                                                                     |                              |                   |                                                                                    | 2.1 MHz                       |           | 0.0    |       |      |

| Delay time, STRA as                                                                 | serted to port C,            | t <sub>PCD</sub>  |                                                                                    | 1.0 MHz<br>2.1 MHz<br>1.0 MHz | 9, 10, 11 |        | 100.0 | ns   |

| data output valid                                                                   |                              |                   |                                                                                    |                               | -         |        | 100.0 |      |

| Hold time, STRA neg                                                                 | gated to port C data         | t <sub>PCH</sub>  |                                                                                    |                               | 9, 10, 11 | 10.0   |       | ns   |

|                                                                                     |                              |                   |                                                                                    | 2.1 MHz                       |           | 10.0   |       |      |

| Three-state hold time                                                               | 9                            | t <sub>PCZ</sub>  |                                                                                    | 1.0 MHz                       | 9, 10, 11 |        | 150.0 | ns   |

|                                                                                     |                              |                   |                                                                                    | 2.1 MHz                       |           |        | 150.0 |      |

REVISION LEVEL

SHEET

7

DSCC FORM 2234 APR 97

DEFENSE SUPPLY CENTER COLUMBUS

COLUMBUS, OHIO 43218-3990

|                                                                                                              | TA                                    | ABLE I. <u>El</u> | ectrical performar                                                             | nce characteristics                                                     | - Continued.         |                      |                            |                  |

|--------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------|----------------------|----------------------------|------------------|

| Te                                                                                                           | est                                   | Symbol            | +4.5 V ≤                                                                       | Display="block">Display="block" block">Display= 0 block<br>$S = 0 V dc$ | Group A<br>subgroups | Lir                  | nits                       | Unit             |

|                                                                                                              |                                       |                   | -55°C ≤                                                                        | ≤ T <sub>C</sub> ≤ +125°C<br>≤ E ≤ 2.1 MHz                              |                      | Min                  | Max                        |                  |

|                                                                                                              |                                       |                   | A/D co                                                                         | nverter                                                                 |                      |                      |                            |                  |

| Resolution                                                                                                   |                                       | RES               | Number of bits r                                                               | esolved by the A/D                                                      | 4, 5, 6              | 8                    |                            | Bits             |

| Non-linearity                                                                                                |                                       | NLI               | Maximum deviat<br>A/D transfer cha                                             | tion from the ideal a<br>racteristics                                   | ind 4, 5, 6          |                      | ±1/2                       | LSB              |

| Zero error                                                                                                   |                                       | ZER               |                                                                                | veen the output of an<br>ual A/D for zero inp                           |                      |                      | ±1/2                       | LSB              |

| Full-scale error                                                                                             |                                       | FSE               |                                                                                | een the output of an ual A/D for full-scale                             |                      |                      | ±1/2                       | LSB              |

| Total unadjusted                                                                                             | error                                 | TUE               | Maximum sum of error, and full-so                                              | 4, 5, 6                                                                 |                      | ±1/2                 | LSB                        |                  |

| Quantization error                                                                                           | r                                     | QTE               | Uncertainty due resolution                                                     | to converter                                                            | 4, 5, 6              |                      | ±1/2                       | LSB              |

| Absolute accuracy                                                                                            | Absolute accuracy                     |                   | Difference betwee<br>voltage and the<br>equivalent of the<br>all error sources |                                                                         |                      | ±1                   | LSB                        |                  |

| Conversion range                                                                                             | 1                                     | COR               | Analog input vol                                                               | 4, 5, 6                                                                 | $V_{RL}$             | $V_{RH}$             | V                          |                  |

| Maximum analog                                                                                               | reference voltage                     | $V_{RH}$          | <u>7</u> /                                                                     | 4, 5, 6                                                                 | V <sub>RL</sub>      | V <sub>DD</sub> +0.1 | V                          |                  |

| Minimum analog r                                                                                             | eference voltage                      | $V_{RL}$          | <u>7</u> /                                                                     | 4, 5, 6                                                                 | V <sub>SS</sub> -0.1 | $V_{RH}$             | V                          |                  |

| $\begin{array}{c} \mbox{Minimum difference} \\ \mbox{V}_{\rm RH} \mbox{ and } \mbox{V}_{\rm RL} \end{array}$ | ce between                            | $\Delta V_R$      | <u>7</u> /                                                                     | 4, 5, 6                                                                 | 3                    |                      | V                          |                  |

| Conversion time                                                                                              | E clock                               | CONT              | Total time to per                                                              |                                                                         | 4, 5, 6              |                      | 32 <u>8</u> /              | t <sub>cyc</sub> |

|                                                                                                              | Internal RC<br>oscillator <u>8</u> /  |                   | analog-to-digital                                                              | conversion                                                              |                      |                      | t <sub>cyc</sub><br>+40000 | ns               |

| Monotonicity                                                                                                 |                                       | MON               |                                                                                | Ilt never decreases<br>in input voltage and<br>codes <u>9</u> /         | 4, 5, 6<br>d         |                      |                            |                  |

| Zero input reading                                                                                           | 9                                     | ZIR               | Conversion resu                                                                | It when $V_{IN} = V_{RL}$                                               | 4, 5, 6              | 00                   |                            | Hex              |

| Full scale reading                                                                                           |                                       | FSR               | Conversion resu                                                                | It when $V_{IN} = V_{RH}$                                               | 4, 5, 6              |                      | FF                         | Hex              |

| Sample                                                                                                       | E clock <u>10</u> /                   | SAT               | • •                                                                            | quisition sampling                                                      | 4, 5, 6              | 12                   |                            | t <sub>cyc</sub> |

| acquisition<br>time                                                                                          | Internal RC<br>oscillator <u>11</u> / |                   | time                                                                           |                                                                         |                      |                      | 12                         | μS               |

| Input leakage                                                                                                | PE0-PE7                               | I <sub>IN</sub>   | Input leakage or                                                               | n A/D pins                                                              | 9, 10, 11            |                      | 400                        | nA               |

|                                                                                                              | V <sub>RL</sub> , V <sub>RH</sub>     | 1                 |                                                                                |                                                                         |                      |                      | 1.0                        | μA               |

| See footnotes at                                                                                             | end of table.                         |                   |                                                                                |                                                                         |                      |                      |                            |                  |

| міс                                                                                                          | STANDAR<br>ROCIRCUIT D                |                   | G                                                                              | SIZE<br>A                                                               |                      |                      | 5962-8                     | 39527            |

| DEFENS                                                                                                       | E SUPPLY CENT<br>LUMBUS, OHIO         | ER COLUI          | MBUS                                                                           |                                                                         | REVISION LEVE<br>C   | EL                   | SHEET<br>8                 | }                |

| Test                                 | Symbol           |                         | nditions $V_{DD} \le +5.5 \text{ V}$          | Group A<br>subgroups | Lin    | nits   | Unit  |

|--------------------------------------|------------------|-------------------------|-----------------------------------------------|----------------------|--------|--------|-------|

|                                      |                  | V <sub>SS</sub>         | +0.5 v<br>= 0 V dc<br>T <sub>C</sub> ≤ +125°C | bubgroups            | Min    | Max    |       |

|                                      |                  | Expansion I             | ous timing                                    |                      |        |        |       |

| Frequency of operation (E clock      | f <sub>o</sub>   | V <sub>DD</sub> = 4.5 V | 1.0 MH                                        | z 9, 10, 11          | 1.0    | 1.0    | MHz   |

| frequency)                           |                  | See figure 4            | 2.1 MH                                        | Z                    | 2.1    | 2.1    |       |

| Cycle time                           | t <sub>cyc</sub> |                         | 1.0 MH                                        | z 9, 10, 11          | 1000.0 |        | ns    |

|                                      |                  |                         | 2.1 MH                                        | z                    | 476.0  |        |       |

| Pulse width, E low                   | PW <sub>EL</sub> |                         | 1.0 MH                                        | z 9, 10, 11          | 477.0  |        | ns    |

|                                      |                  |                         | 2.1 MH                                        | z                    | 215.0  |        |       |

| Pulse width, E high                  | PW <sub>EH</sub> |                         | 1.0 MHz                                       | z 9, 10, 11          | 472.0  |        | ns    |

|                                      |                  |                         | 2.1 MH                                        | z                    | 210.0  |        |       |

| E and AS rise time                   | t <sub>r</sub>   |                         | 1.0 MH                                        | z 9, 10, 11          |        | 20.0   | ns    |

|                                      |                  |                         | 2.1 MH                                        | z                    |        | 20.0   |       |

| E and AS fall time                   | t <sub>f</sub>   |                         | 1.0 MH                                        | z 9, 10, 11          |        | 20.0   | ns    |

|                                      |                  |                         | 2.1 MH                                        | z                    |        | 20.0   |       |

| Address hold time                    | t <sub>AH</sub>  |                         | 1.0 MH                                        | z 9, 10, 11          | 95.5   |        | ns    |

|                                      |                  |                         | 2.1 MH                                        | z                    | 30.0   |        |       |

| Non-muxed address valid time         | t <sub>AV</sub>  |                         | 1.0 MH                                        | z 9, 10, 11          | 281.5  |        | ns    |

| to E rise <u>8</u> /                 |                  |                         | 2.1 MH                                        | z                    | 85.0   |        |       |

| Read data setup time                 | t <sub>DSR</sub> |                         | 1.0 MH                                        | z 9, 10, 11          | 30.0   |        | ns    |

|                                      |                  |                         | 2.1 MH                                        | z                    | 30.0   |        |       |

| Read data hold time                  | t <sub>DHR</sub> |                         | 1.0 MH                                        | z 9, 10, 11          | 10.0   | 145.5  | ns    |

|                                      |                  |                         | 2.1 MH                                        | z                    | 10.0   | 80.0   |       |

| Write data delay time 8a/            | t <sub>DDW</sub> |                         | 1.0 MH                                        | z 9, 10, 11          |        | 190.5  | ns    |

|                                      |                  |                         | 2.1 MH                                        | z                    |        | 125.0  |       |

| Write data hold time <u>8a/</u>      | t <sub>DHW</sub> |                         | 1.0 MH                                        | z 9, 10, 11          | 95.5   |        | ns    |

|                                      |                  |                         | 2.1 MH                                        | z                    | 30.0   |        |       |

| Muxed address valid time to          | t <sub>AVM</sub> |                         | 1.0 MH                                        | z 9, 10, 11          | 271.5  |        | ns    |

| E rise <u>8b</u> /                   |                  |                         | 2.1 MH                                        | z                    | 75.0   |        |       |

| Muxed address valid time to          | t <sub>ASL</sub> |                         | 1.0 MHz                                       | z 9, 10, 11          | 151.0  |        | ns    |

| AS fall                              |                  |                         | 2.1 MH                                        | z                    | 20.0   |        |       |

| Muxed address hold time <u>8b</u> /  | t <sub>AHL</sub> |                         | 1.0 MH                                        | z 9, 10, 11          | 95.5   |        | ns    |

|                                      |                  |                         | 2.1 MH                                        | z                    | 30.0   |        |       |

| See footnotes at end of table.       |                  |                         |                                               |                      |        |        |       |

| STANDA<br>MICROCIRCUIT               |                  | G                       | SIZE<br>A                                     |                      |        | 5962-8 | 89527 |

| DEFENSE SUPPLY CEN<br>COLUMBUS, OHIO | TER COLUI        | MBUS                    |                                               | REVISION LEVE<br>C   | iL     | SHEET  | )     |

| Test                        |                                    | Symbol                        | Condi<br>+4.5 V ≤ V <sub>E</sub>            | <sub>DD</sub> ≤ <b>+</b> 5.5 V | Group A<br>subgroups | Lin         | nits   | Unit             |

|-----------------------------|------------------------------------|-------------------------------|---------------------------------------------|--------------------------------|----------------------|-------------|--------|------------------|

|                             |                                    |                               | $V_{SS}$ = 0<br>-55°C $\leq$ T <sub>C</sub> |                                |                      | Min         | Max    |                  |

|                             |                                    |                               | Expansion bus timing                        | g - Continued                  |                      |             | 1      |                  |

| Delay time, E to AS rise    | e <u>8b</u> /                      | t <sub>ASD</sub>              | $V_{DD} = 4.5 V$                            | 1.0 MHz                        | 9, 10, 11            | 115.5       |        | ns               |

|                             |                                    |                               | See figure 4                                | 2.1 MHz                        |                      | 50.0        |        |                  |

| Pulse width, AS high        |                                    | $PW_{ASH}$                    |                                             | 1.0 MHz                        | 9, 10, 11            | 221.0       |        | ns               |

|                             |                                    |                               |                                             | 2.1 MHz                        |                      | 90.0        |        |                  |

| Delay time, AS to E rise    | e <u>8b</u> /                      | t <sub>ASED</sub>             |                                             | 1.0 MHz                        | 9, 10, 11            | 95.5        |        | ns               |

|                             |                                    |                               |                                             | 2.1 MHz                        |                      | 40.0        |        |                  |

| MPU address access ti       | me <u>8b</u> /                     | t <sub>ACCA</sub>             |                                             | 1.0 MHz                        | 9, 10, 11            | 733.5       |        | ns               |

|                             |                                    |                               |                                             | 2.1 MHz                        |                      | 275.0       |        |                  |

| MPU access time             |                                    | t <sub>ACCE</sub>             |                                             | 1.0 MHz                        | 9, 10, 11            |             | 442.0  | ns               |

|                             |                                    |                               |                                             | 2.1 MHz                        |                      |             | 180.0  |                  |