|                                                                                   | REVISIONS                          |              |                                 |                             |                 |      |                     |              |                |               |               |               |                |              |     |                    |           |                    |    |    |

|-----------------------------------------------------------------------------------|------------------------------------|--------------|---------------------------------|-----------------------------|-----------------|------|---------------------|--------------|----------------|---------------|---------------|---------------|----------------|--------------|-----|--------------------|-----------|--------------------|----|----|

| LTR                                                                               |                                    | DESCRIPTION  |                                 |                             |                 |      |                     |              |                | D             | ATE (         | YR-MO         | -DA)           |              | APP | ROVE               | D         |                    |    |    |

| A                                                                                 | Add                                | d dev        | vices 03, 04. Editorial changes |                             |                 |      |                     |              |                |               |               | 94-03-23      |                |              | Мо  | Monica L. Poelking |           |                    |    |    |

| В                                                                                 | Add                                | dev<br>cough | rices<br>nout                   | s 05,                       | 06,             | 07,  | 08.                 | Ed           | litor          | ial           | chan          | ges           | 96-            | -03-2        | 28  |                    | Мо        | Monica L. Poelking |    |    |

| С                                                                                 |                                    | dev<br>lerp  |                                 | types 09 and 10. Update 96- |                 |      |                     |              |                |               |               | 10-2          | 28             |              | Мо  | Monica L. Poelking |           | lking              |    |    |

|                                                                                   |                                    |              |                                 |                             |                 |      |                     |              |                |               |               |               |                |              |     |                    |           |                    |    |    |

| REV                                                                               |                                    |              |                                 |                             |                 |      |                     |              |                |               |               |               | :              |              |     |                    |           |                    |    |    |

| SHEET                                                                             |                                    |              |                                 |                             |                 |      |                     |              |                |               |               |               |                |              |     |                    |           |                    |    |    |

| REV                                                                               | С                                  | С            | С                               | С                           | С               | С    | С                   | С            | С              | С             | С             | С             | С              | С            | С   | С                  | С         |                    |    |    |

| SHEET                                                                             | 15                                 | 16           | 17                              | 18                          | 19              | 20   | 21                  | 22           | 23             | 24            | 25            | 26            | 27             | 28           | 29  | 30                 | 31        |                    |    |    |

| REV STATUS<br>OF SHEETS                                                           | 3                                  |              |                                 | RE                          |                 |      | С                   | С            | С              | С             | С             | С             | С              | С            | С   | С                  | С         | С                  | С  | С  |

|                                                                                   |                                    |              |                                 | SHE                         | ET              |      | 1                   | 2            | 3              | 4             | 5             | 6             | 7              | 8            | 9   | 10                 | 11        | 12                 | 13 | 14 |

| PMIC N/A                                                                          |                                    | <u>-</u>     |                                 |                             | PAREI<br>omas N |      | 3                   |              |                |               |               | EFEN          |                |              |     | ITER (             |           |                    |    |    |

| MICRO                                                                             | STANDARD CHECKED BY Thomas M. Hess |              |                                 |                             |                 |      |                     |              |                |               |               |               |                |              |     |                    |           |                    |    |    |

| DRAWING  THIS DRAWING IS AVAILABLE FOR USE BY ALL  APPROVED BY Monica L. Poelking |                                    |              |                                 |                             |                 | INTI | ROCI<br>EGRA<br>CON | RCUI<br>TION | T, DIC<br>MICE | GITAL<br>ROPF | ., CM<br>ROCE | OS, 3<br>SSOF | 2-BIT<br>R, MO | HIGH<br>NOLI | HIC |                    |           |                    |    |    |

| DEPAR<br>AND AGEN<br>DEPARTMEN                                                    | CIES (                             | OF THE       |                                 | DRA                         | WING A          |      | OVAL E<br>2-26      | ATE          |                | SIZE          | _             |               | E COD          |              |     |                    | 62-       | 931                | 05 |    |

| AMSC N                                                                            | N/A                                |              |                                 | REVI                        | ISION I         |      |                     |              |                |               | 1             | 6             | 726            | გ            |     |                    | ~ <b></b> |                    |    |    |

|                                                                                   | C SHEET 1                          |              |                                 |                             |                 |      |                     |              | 1              | •             | OF            | 3             | 1              |              |     |                    |           |                    |    |    |

- 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents three product assurance class levels consisting of space application (device classe Q), high reliability (device classes M and Q), and non traditional performance environment (device class N). A choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of Radiation Hardness Assurance (RHA) levels are reflected in the PIN. For device class N, the user is cautioned to assure that the device is appropriate for the application environment.

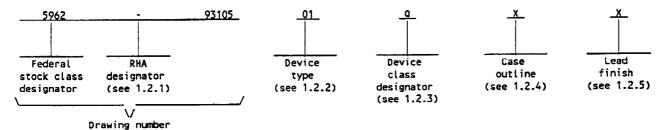

- 1.2 PIN. The PIN is as shown in the following example:

- 1.2.1 <u>RHA designator</u>. Device classes N, Q and V RHA marked devices meet the MIL-PRF-38535 specified RHA levels and are marked with the appropriate RHA designator. Device class M RHA marked devices meet the MIL-PRF-38535, appendix A specified RHA levels and are marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 Device type(s). The device type(s) identify the circuit function as follows:

| Device type | Generic number | Circuit function                       |  |  |  |  |  |

|-------------|----------------|----------------------------------------|--|--|--|--|--|

| 01          | 80486DX-25     | 32 Bit High Integration Microprocessor |  |  |  |  |  |

| 02          | 80486DX-33     | 32 Bit High Integration Microprocessor |  |  |  |  |  |

| 03 1/       | 80486DX2-50    | 32 Bit High Integration Microprocessor |  |  |  |  |  |

| 04 1/       | 80486DX2-66    | 32 Bit High Integration Microprocessor |  |  |  |  |  |

| 05 1/       | 80486DX-25     | 32 Bit High Integration Microprocessor |  |  |  |  |  |

| 06 1/       | 80486DX-33     | 32 Bit High Integration Microprocessor |  |  |  |  |  |

| 07 1/       | 80486DX2-50    | 32 Bit High Integration Microprocessor |  |  |  |  |  |

| 08 1/       | 80486DX2-66    | 32 Bit High Integration Microprocessor |  |  |  |  |  |

| 09 1/       | 80486DX2-50    | 32 Bit High Integration Microprocessor |  |  |  |  |  |

| 10 1/       | 80486DX2-66    | 32 Bit High Integration Microprocessor |  |  |  |  |  |

1.2.3 <u>Device class designator</u>. The device class designator is a single letter identifying the product assurance level as follows:

| Device class | Device requirements documentation                                                                                                                         |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| М            | Vendor self-certification to the requirements for MIL-STD-883 compliant, non-JAN class level B microcircuits in accordance with MIL-PRF-38535, appendix A |

| N            | Certification and qualification to MIL-PRF-38535 with nontraditional performance environment $2/$                                                         |

| Q or V       | Certification and qualification to MIL-PRF-38535                                                                                                          |

1.2.4 <u>Case outline(s)</u>. The case outline(s) are as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style            |

|----------------|------------------------|------------------|--------------------------|

| X              | CMGA9-P168             | 168              | Ceramic, pin grid array  |

| Y              | See Figure 1           | 196              | Leaded chip carrier with |

1.2.5 <u>Lead finish</u>. The lead finish is as specified in MIL-PRF-38535 for device classes Q and V or MIL-PRF-38535, appendix A for device class M.

Device types 03 and 04 provide testability features compatible with the IEEE Standard Test Access Port and Boundry Scan Architecture (IEEE Standard 1149.1). Device type 05, 06, 07, 08, 09 and 10 are JTAG compatible and have the system management enhancement (SL).

2/ Any device outside the traditional performance environment; e.g., an operating temperature rangefor device types 01-08 -55°C to +125°C and device types 09 and 10 -40°C to +110°C and which requires hermetic packaging.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-93105     |

|-------------------------------------------------------------|------------------|---------------------|----------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>C | SHEET <b>2</b> |

### 1.3 Absolute maximum ratings. 2/ -65°C to +150°C Supply voltage with respect to ground range . . . . . . -0.5V dc to +6.5V dc Voltage on any pin with respect to ground range . . . . . -0.5V dc to +5.5V dc Maximum power dissipation (PD) 3.675 W 4.725 W 4.988 W 6.3 W Lead temperature (soldering, 10 seconds) . . . . . . . . 300°C Thermal resistance, junction-to-case ( $\theta_{JC}$ ): 1.5°C/W Maximum junction temperature (T<sub>j</sub>) Devices 01,02,05,06: Case X (T<sub>J</sub>) = 132.1°C; Case Y (T<sub>J</sub>) = 136.8°C Devices 03,04,07,08: Case X (T<sub>J</sub>) = 134.5°C; Case Y (T<sub>J</sub>) = 140.8°C Devices 09 and 10: Case X (T<sub>J</sub>) = 119°C; Case Y (T<sub>J</sub>) = 125.8°C 1.4 Recommended operating conditions. 4.75 V dc & Vcc & 5.25 V dc 1.5 Digital logic testing for device classes Q and V. Fault coverage measurement of manufacturing logic tests (MIL-STD-883, test method 5012) . . . . . . . 98.5 percent 2. APPLICABLE DOCUMENTS 2.1 Government specification, standards, and handbooks. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those listed in the issue of the Department of Defense Index of Specifications and Standards (DoDISS) and supplement thereto, cited in the solicitation. **SPECIFICATION** MILITARY MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for. STANDARDS MILITARY MIL-STD-883 - Test Methods and Procedures for Microelectronics. MIL-STD-973 - Configuration Management. MIL-STD-1835 - Microcircuit Case Outlines. **HANDBOOKS** MILITARY MIL-HDBK-103 - List of Standard Microcircuit Drawings (SMD's). MIL-HDBK-780 - Standard Microcircuit Drawings. (Unless otherwise indicated, copies of the specification, standards, and handbooks are available from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.) 2.2 Non Government publications. The following document(s) for a part of this document to the extent specified herein. Unless otherwise specified, the issues of the documents which are DOD adopted are those listed in the issue of the DODISS cited in the solicitation. Unless otherwise specified, the issues of documents not listed in the DODISS are the issues of the documents cited in the solicitation. 2/ Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability. SIZE **STANDARD** 5962-93105 Α MICROCIRCUIT DRAWING **DEFENSE SUPPLY CENTER COLUMBUS REVISION LEVEL** SHEET COLUMBUS, OHIO 43216-5000 С 3

INSTITUTE OF ELECTRICAL AND ELECTRONICS ENGINEERS (IEEE)

IEEE Standard 1149.1 - IEEE Standard Test Access Port and Boundary Scan Architecture.

(Applications for copies should be addressed to the Institute of Electrical and Electronics Engineers, 445 Hoes Lane, Piscataway, NJ 08854-4150.)

(Non-Government standards and other publications are normally available from the organizations that prepare or distribute the documents. These documents may also be available in or through libraries or other informational sevices.)

2.3 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

#### 3. REQUIREMENTS

- 3.1 Item requirements. The individual item requirements for device classes Q and V shall be in accordance with MIL-PRF-38535 and as specified herein or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein. The individual item requirements for device class M shall be in accordance with MIL-PRF-38535, appendix A for non-JAN class level B devices and as specified herein.

- 3.2 <u>Design. construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535 and herein for device classes N,Q and V or MIL-PRF-38535, appendix A and herein for device class M.

- 3.2.1 Case outline(s). The case outline(s) shall be in accordance with 1.2.4 herein and figure 1.

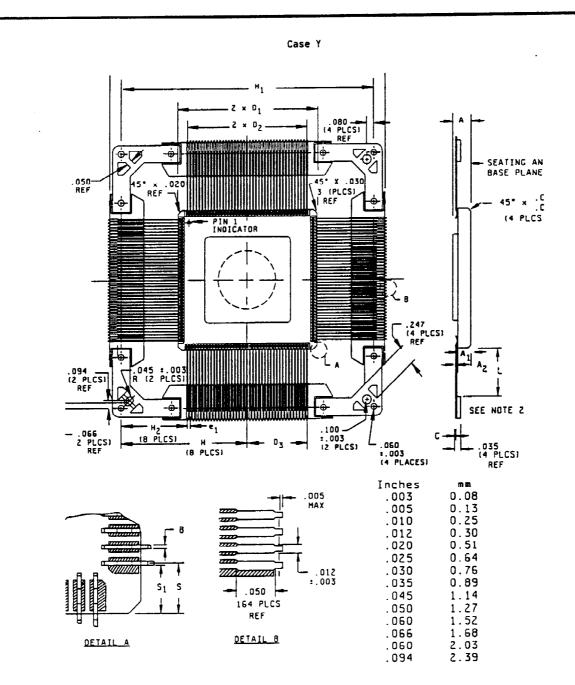

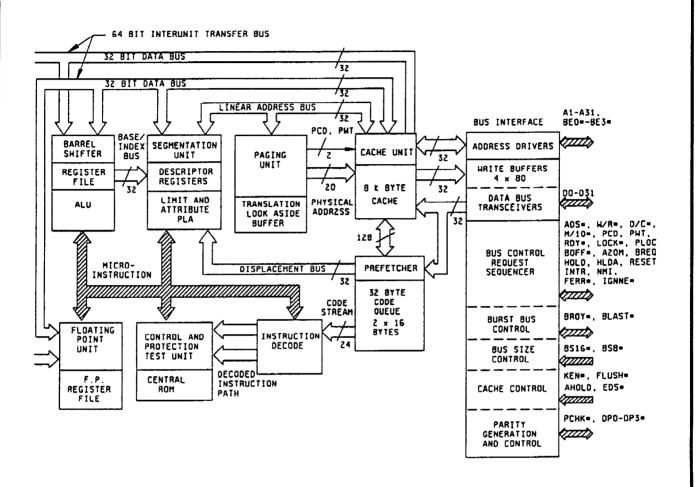

- 3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 2.

- 3.2.3 Block diagram. The block diagram shall be as specified on figure 3.

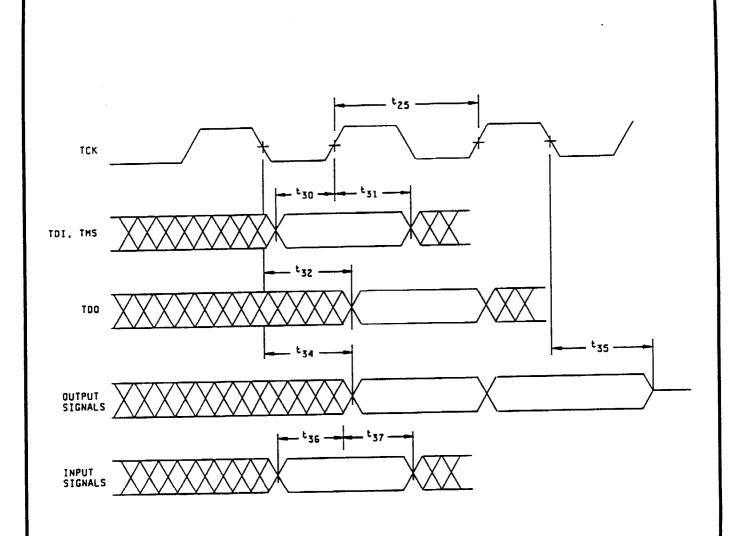

- 3.2.4 <u>Boundary Scan Instruction Codes</u>. For device 03 10 the boundary scan instruction codes shall be as specified on figure 4.

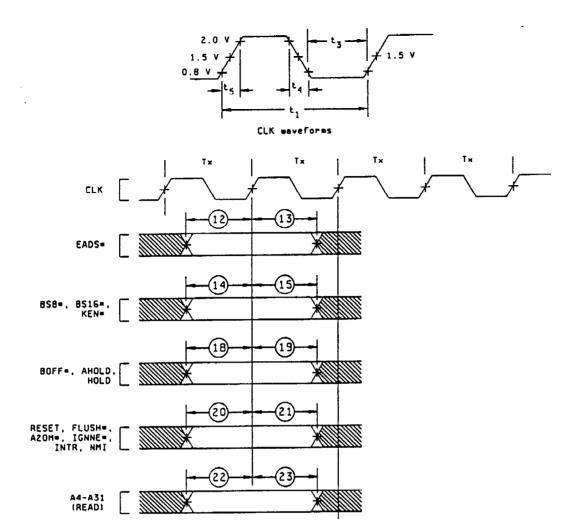

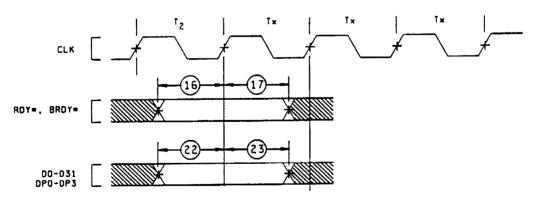

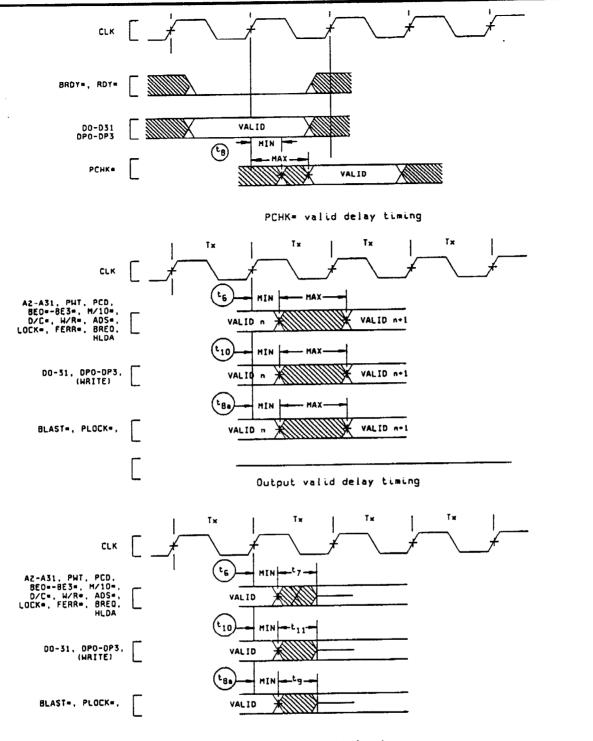

- 3.2.5 <u>Timing waveforms</u>. The timing waveforms shall be as specified on figure 5.

- 3.2.6 Radiation exposure circuit. The radiation exposure circuit shall be as specified when available.

- 3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are defined in table I.

- 3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked as listed in MIL-HDBK-103. For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device. For RHA product using this option, the RHA designator shall still be marked. Marking for device classes N,Q and V shall be in accordance with MIL-PRF-38535. Marking for device class M shall be in accordance with MIL-PRF-38535, appendix A.

- 3.5.1 <u>Certification/compliance mark</u>. The certification mark for device classes N,Q and V shall be a "QML" or "Q" as required in MIL-PRF-38535. The compliance mark for device class M shall be a "C" as required in MIL-PRF-38535, appendix A.

- 3.6 <u>Certificate of compliance</u>. For device classes N, Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.6.1 herein). For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-HDBK-103 (see 6.6.2 herein). The certificate of compliance submitted to DSCC-VA prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device classes N,Q and V, the requirements of MIL-PRF-38535 and herein or for device class M, the requirements of MIL-PRF-38535, appendix A and herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device classes N, Q and V in MIL-PRF-38535 or for device class M in MIL-PRF-38535, appendix A shall be provided with each lot of microcircuits delivered to this drawing.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-93105 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | C              | 4          |

| Test                    | Symbol          | Conditions 1/                                                | Group A subgroups | Device<br>type         | L                  | Unit                 |            |

|-------------------------|-----------------|--------------------------------------------------------------|-------------------|------------------------|--------------------|----------------------|------------|

|                         |                 | 4.75 V < V <sub>CC</sub> < 5.25 V unless otherwise specified | dus, cop.         |                        | Min                | Max                  | <br>       |

| Input low voltage       | v <sub>IL</sub> | Frequency = 8 MHz 2/3/                                       | 1,2,3             | ALL                    | -0.3<br><u>4</u> / | 0.8                  | v          |

| Input high voltage      | v <sub>IH</sub> | Frequency = 8 MHz 2/3/                                       | 1,2,3             | All                    | 2.0                | V <sub>CC</sub> +0.3 | v          |

| Output low voltage 3/5/ | VOL             | I <sub>OL</sub> = 4.0 mA                                     | 1,2,3             | 01,03,<br>05,07,<br>09 |                    | 0.45                 | ٧          |

|                         | 1               | I <sub>OL</sub> = 5.0 mA                                     |                   | 02,04,<br>06,08,<br>10 |                    |                      | İ          |

| Output high voltage 5/  | VOH             | I <sub>OH</sub> = -1.0 mA                                    | 1,2,3             | 01,03,<br>05,07        | 2.4                |                      | ٧          |

|                         |                 | I <sub>OH</sub> = -0.9 mA                                    |                   | 02,04,<br>06,08,<br>10 |                    |                      |            |

| Input leakage current   | ILI             | $V_{ m IN}$ = GND and $V_{ m CC}$                            | 1,2,3             | ALL                    | -15                | +15                  | μA         |

| Input leakage current   | 114             | v <sub>IN</sub> = 2.4 v <u>6</u> /                           | 1,2,3             | ALL                    |                    | 200                  | μΑ         |

| Input leakage current   | 1 <sub>IL</sub> | v <sub>IN</sub> = 0.45 v Z/                                  | 1,2,3             | ALL                    |                    | -400                 | μ <b>Α</b> |

| Output leakage current  | ILO             | V <sub>IN</sub> = GND and V <sub>CC</sub>                    | 1,2,3             | All                    | -15                | +15                  | μ <b>A</b> |

| Supply current          | <sup>I</sup> cc | VCC = VCC MAX                                                | 1,2,3             | 01.05<br>02.06         |                    | 700                  | mA         |

|                         |                 |                                                              |                   | 03,07<br>09            |                    | 950                  |            |

|                         |                 |                                                              |                   | 04,08                  |                    | 1200                 |            |

| CLK input capacitance   | CCLK            | Frequency = 1 MHz                                            | 4                 | 01,02,<br>05,07,<br>09 |                    | 20                   | pF         |

| •                       |                 | See 4.4.1.c                                                  | İ                 | 03,04,<br>06,08,<br>10 |                    | 15                   | •          |

|                         |                 |                                                              | ,                 | 01,02,<br>05,07,       |                    | 20                   | _F         |

| Input capacitance       | CIN             | Frequency = 1 MHz<br>See 4.4.1.c                             | 4                 | 09<br>03,04,<br>06,08, |                    | 13                   | pF         |

See footnotes at end of table.

STANDARD

MICROCIRCUIT DRAWING

DEFENSE SUPPLY CENTER COLUMBUS

COLUMBUS, OHIO 43216-5000

SIZE

A

5962-93105

REVISION LEVEL

C

5

| Test                                                                           | Symbol         | Conditions 1/<br>4.75 V < V <sub>CC</sub> < 5.25 V<br>unless otherwise specified | Group A<br>subgroups | Device<br>type                          | Limits  |                      | Unit     |

|--------------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------|----------------------|-----------------------------------------|---------|----------------------|----------|

|                                                                                |                |                                                                                  |                      |                                         | Min     | Max                  |          |

| Input/output capacitance                                                       | co             | Frequency = 1 MHz<br>See 4.4.1.c                                                 | 4                    | 01,02,<br>05,07,09<br>03,04,            |         | 20                   | pF       |

| Functional test                                                                |                | See 4.4.1.b                                                                      | 7.8                  | 06.08.10<br>ALL                         |         | 17                   |          |

| System clock period 8/                                                         | t <sub>1</sub> | See figure 5                                                                     | 9,10,11              | 01,03,05,07<br>09                       | 40      | 125                  | ns       |

|                                                                                |                |                                                                                  |                      | 02,04,06,08                             | 30      | 125                  | ļ        |

| System clock high time                                                         | t <sub>2</sub> | at 2.0 V<br>See figure 5                                                         | 9,10,11              | 01,03,05,07                             | 14      |                      | ns       |

|                                                                                |                |                                                                                  | 1                    | 02,04,06,08<br>10                       | 11      |                      |          |

| System clock low time                                                          | t3             | at 0.8 V<br>See figure 5                                                         | 9,10,11              | 01,03,05,07<br>09<br>02,04,06,08        | 14      |                      | пs       |

|                                                                                |                |                                                                                  |                      | 10                                      | ''      |                      |          |

| System clock fall time 9/                                                      | t <sub>4</sub> | 2.0 V to 0.8 V<br>See figure 5                                                   | 9,10,11              | 01,03,05,07<br>09                       |         | 4                    | ns       |

|                                                                                |                |                                                                                  |                      | 02,04,06,08                             |         | 3                    | ļ        |

| System clock rise time 2/                                                      | t <sub>5</sub> | 0.8 V to 2.0 V<br>See figure 5                                                   | 9,10,11              | 01,03,05,07<br>09                       |         | 4                    | ns       |

|                                                                                |                |                                                                                  |                      | 02,04,06,08<br>10                       |         | 3                    |          |

| A2-A31,PWT,PCD,BEO-3#,M/IO#,<br>D/C#,W/R#,ADS#,LOCK#,<br>FERR#,BREQ,HLDA VALID | t <sub>6</sub> | See figure 5                                                                     | 9,10,11              | 01<br>02,<br>03,05,07,09                | 2 2 2 2 | 22<br>16<br>19<br>14 | ns       |

| DELAY                                                                          |                |                                                                                  |                      | 04,06,08,10                             | 2       | 14                   | <u> </u> |

| A2-A31,PWT,PCD,BEO-3#,M/IO#,<br>D/C#,W/R#,ADS#,LOCK#<br>FLOAT DELAY            | t7             | See figure 5                                                                     | 9,10,11              | 01<br>02,<br>03,05,07,09<br>04,06,08,10 |         | 30<br>20<br>28<br>20 | ns       |

| PCHK# VALID DELAY                                                              | ta             | See figure 5                                                                     | 9,10,11              | 01                                      | 2       | 27                   | ns       |

|                                                                                |                |                                                                                  |                      | 02,<br>03,05,07,09<br>04,06,08,10       | 2 2 2   | 22<br>24<br>14       |          |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-93105 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | C              | 6          |

|                                           | TABL              | E I. <u>Electrical pe</u>                                   | rformance ch     | naracteris           | tics.                                   |                  |                      |       |

|-------------------------------------------|-------------------|-------------------------------------------------------------|------------------|----------------------|-----------------------------------------|------------------|----------------------|-------|

| Test                                      | Symbol            | Condition<br>4.75 V s V <sub>CC</sub> s<br>unless otherwise | 5.25 V           | Group A<br>subgroups | Device<br>type                          |                  | Limits               | Uni   |

|                                           |                   |                                                             |                  |                      |                                         | Min              | Max                  |       |

| BLAST#, PLOCK# VALID DELAY                | <sup>t</sup> 8a   | See figure 5                                                |                  | 9,10,11              | 01<br>02,<br>03,05,07,09<br>04.06.08.10 | 2<br>2<br>2<br>2 | 27<br>20<br>24<br>14 | ns    |

| BLAST#, PLOCK# FLOAT DELAY                | tg                | See figure 5                                                |                  | 9,10,11              | 01<br>02,<br>03,05,07,09<br>04,06,08,10 |                  | 30<br>20<br>28<br>20 | ns    |

| DO-D31,DPO-3 WRITE DATA<br>VALID DELAY    | t <sub>10</sub>   | See figure 5                                                |                  | 9,10,11              | 01<br>02<br>03,05,07,09<br>04,06,08,10  | 2 2 2            | 22<br>18<br>20<br>14 | ns    |

| DO-D31,DPO-3 WRITE DATA<br>FLOAT DELAY 4/ | t11               | See figure 5                                                |                  | 9,10,11              | 01<br>02<br>03,05,07,09<br>04,06,08,10  |                  | 30<br>20<br>28<br>20 | ns    |

| EADS# SETUP TIME                          | t <sub>12</sub>   | See figure 5                                                |                  | 9,10,11              | 01,03,05,07<br>09<br>02,04,06,08<br>10  | 8<br>            |                      | ns    |

| EADS# SETUP TIME                          | t <sub>13</sub>   | See figure 5                                                |                  | 9,10,11              | ALL                                     | 3                |                      | ns    |

| KEN#,BS16#,BS8# SETUP TIME                | t <sub>14</sub>   | See figure 5                                                |                  | 9,10,11              | 01,03,05,07<br>09<br>02,04,06,08<br>10  | 8                |                      | ns    |

| KEN#,BS16#,BS8# HOLD TIME                 | t <sub>15</sub>   | See figure 5                                                |                  | 9,10,11              | All                                     | 3                |                      | ns    |

| RDY#,BRDY# SETUP TIME                     | t <sub>16</sub>   | See figure 5                                                |                  | 9,10,11              | 01,03,05,07<br>09<br>02,04,06,08        | 8 5              |                      | ns    |

| DY#,BRDY# HOLD TIME                       | t <sub>17</sub>   | See figure 5                                                |                  | 9,10,11              | ALL                                     | 3                |                      | ns    |

| OLD,AHOLD SETUP TIME                      | t <sub>18</sub> s | Gee figure 5                                                |                  | 9,10,11              | 01<br>02,04,06,08<br>10<br>03,05,07,09  | 10 6             |                      | ns    |

| see footnotes at end of table             |                   |                                                             |                  |                      | <u> </u>                                |                  |                      |       |

| STANI<br>MICROCIRCU                       | IT DRAWIN         |                                                             | SIZE<br><b>A</b> |                      |                                         |                  | 5962-                | 93105 |

| DEFENSE SUPPLY C<br>COLUMBUS, OF          |                   |                                                             |                  | REV                  | ISION LEVEL<br>C                        |                  | SHEET                | 7     |

| Test                                                | Symbol Conditions 1/ |                                                                 | Group A<br>subgroups | Device<br>type                         | Limits            |          | Uni |

|-----------------------------------------------------|----------------------|-----------------------------------------------------------------|----------------------|----------------------------------------|-------------------|----------|-----|

|                                                     |                      | 4.75 V ≤ V <sub>CC</sub> ≤ 5.25 V<br>unless otherwise specified |                      |                                        | Min               | Max      |     |

| BOFF# SETUP TIME                                    | <sup>t</sup> 18a     | See figure 5                                                    | 9,10,11              | 01<br>02<br>03,05,07,09<br>04,06,08,10 | 10<br>8<br>8<br>7 |          | ns  |

| HOLD,AHOLD,BOFF# HOLD TIME                          | t <sub>19</sub>      | See figure 5                                                    | 9,10,11              | All                                    | 3                 |          | ns  |

| RESET, FLUSH#, A20M#,NMI,<br>INTR,IGNNE# SETUP TIME | <sup>t</sup> 20      | See figure 5                                                    | 9,10,11              | 01<br>02<br>03,05,07,09<br>04,06,08,10 | 10<br>5<br>8<br>5 |          | nŝ  |

| RESET, FLUSH#, A20M#,NMI,<br>INTR,IGNNE# SETUP TIME | t <sub>21</sub>      | See figure 5                                                    | 9,10,11              | All                                    | 3                 |          | ns  |

| DO-D31,DPO-3,A4-A31 READ<br>SETUP TIME              | t <sub>22</sub>      | See figure 5                                                    | 9,10,11              | All                                    | 5                 |          | ns  |

| DO-D31,DPO-3,A4-A31 READ<br>HOLD TIME               | t <sub>23</sub>      | See figure 5                                                    | 9,10,11              | All                                    | 3                 |          | ns  |

| TCK frequency                                       | t <sub>24</sub>      | See figure 6<br>1X clock                                        | 9,10,11              | ALL                                    |                   | 8        | MHz |

| TCK period                                          | t <sub>25</sub>      | See figure 6                                                    | 9,10,11              | ALL                                    | 125               |          | ns  |

| TCK high time                                       | t <sub>26</sub>      | See figure 6<br>V <sub>IN</sub> = 2.0 V                         | 9,10,11              | 01 - 02<br>03 - 10                     | 10<br>40          |          | ns  |

| TCK low time                                        | t <sub>27</sub>      | See figure 6<br>V <sub>IN</sub> = 0.8 V                         | 9,10,11              | 01 - 02<br>03 - 10                     | 10<br>40          |          | ns  |

| TCK rise time                                       | t <sub>28</sub>      | See figure 6<br>2.0 V to 0.8 V                                  | 9,10,11              | 01 - 02<br>03 - 10                     |                   | 4<br>8   | ns  |

| TCK fall tiem                                       | t <sub>29</sub>      | See figure 6<br>0.8 V to 2.0 V                                  | 9,10,11              | 01 - 02<br>03 - 10                     |                   | 4<br>8   | ns  |

| TDI, TMS setu time                                  | t <sub>30</sub>      | See figure 6                                                    | 9,10,11              | All                                    | 8                 |          | ns  |

| TDI, TMS hold time                                  | t <sub>31</sub>      | See figure 6                                                    | 9,10,11              | 01 - 02<br>03 - 10                     | 7<br>10           |          | ns  |

| TDO valid delay                                     | t <sub>32</sub>      | See figure 6                                                    | 9,10,11              | 01 - 02<br>03 - 10                     | 2 2               | 25<br>30 | ns  |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-93105 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | C              | 8          |

| Test                                  | Symbol          | Conditions 1/                                                   | Group A subgroups | Device<br>type     |      | Uni      |    |

|---------------------------------------|-----------------|-----------------------------------------------------------------|-------------------|--------------------|------|----------|----|

|                                       |                 | 4.75 V < V <sub>CC</sub> < 5.25 V<br>unless otherwise specified |                   | -                  | Min  | Max      |    |

| TDO float delay                       | t <sub>33</sub> | See figure 6                                                    | 9,10,11           | All                |      | 36       | ns |

| All outputs (non-test) valid delay    | t <sub>34</sub> | See figure 6                                                    | 9,10,11           | 01 - 02<br>03 - 10 | 2 2  | 25<br>30 | ns |

| All outputs (non-test)<br>float delay | t <sub>35</sub> | See figure 6                                                    | 9,10,11           | All                |      | 36       | ns |

| All inputs (non-test) setup time      | t <sub>36</sub> | See figure 6                                                    | 9,10,11           | ALL                | 8    |          | ns |

| All inputs (non-test) hold time       | t <sub>37</sub> | See figure 6                                                    | 9,10,11           | 01 - 02<br>03 - 10 | 7 10 |          | ns |

- 1/ All testing to be performed using worst-case test conditions unless otherwise specified. The # sign indicates an active low signal. Temperature range shall be as follows: device types 01-08, case temperature -55°C to +125°C, device types 09-10, case temperature -40°C to +110°C.

- Frequency stated is system frequency, not internal CPU frequency.

- Test pins (TCK, TDI, TCO, TMS) are exceptions. These pins are tested and guaranteed to the following limits:  $v_{IL} = 0$  v,  $v_{IH} = 3$  v,  $v_{OL} = v_{OH} = 1.5$  v,  $I_{OL} = I_{OH} = 0$  mA.

- 4/ Guaranteed by design characterization but not tested.

- Actual value tested may vary due to test hardware limitations, however, specified value is guaranteed.

- Parameter is for input pins with internal pulldown resistors. Parameter is for input pins with internal pullup resistors.

- 8/ Frequencies specified are system interface frequencies. Internal CPU frequency for device type 03, 07 is 50 MHz and for device types 04, 08 is 66 MHz.

- 2/ Parameter is not tested due to test hardware limitations, however, specified value is guaranteed.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                |

|-------------------------------------------------------------|------------------|----------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL |

5962-93105

9

SHEET

#### NOTES:

- 1. Dimensions are in inches.

- 2. Metric equivalents are given for general information only.

FIGURE 1. Case outline.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-93105 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | C              | 10         |

Case Y

|                |             | Millimeters |           | Inches |       |           |  |  |

|----------------|-------------|-------------|-----------|--------|-------|-----------|--|--|

| Symbol         | Min         | Max         | Notes     | Min    | Max   | Notes     |  |  |

| A              | 2.23        | 2.92        | Solid lid | 0.088  | 0.115 | Solid lic |  |  |

| A <sub>1</sub> | 1.96        | 2.39        |           | 0.077  | 0.094 |           |  |  |

| В              | 0.20        | 0.25        |           | 0.008  | 0.010 |           |  |  |

| С              | 0.10        | 0.20        |           | 0.004  | 0.008 |           |  |  |

| D              | 63.50       | 64.01       |           | 2.500  | 2.520 |           |  |  |

| D <sub>1</sub> | 33.65       | 34.16       |           | 1.325  | 1.345 |           |  |  |

| D <sub>2</sub> | 30.48 Basic |             |           | 1.200  | Basic |           |  |  |

| e <sub>1</sub> | 0.58        | 0.69        |           | 0.023  | 0.027 |           |  |  |

| н              | 29.21       | Basic       |           | 1.150  | Basic |           |  |  |

| H <sub>1</sub> | 58.42       | Basic       |           | 2.30   | Basic |           |  |  |

| H <sub>2</sub> | 19.05       | Basic       |           | 0.750  | Basic |           |  |  |

| Ļ              | 9.27        | 10.03       |           | 0.365  | 0.395 |           |  |  |

| N              | 19          | 96          |           | 19     | 96    |           |  |  |

| s              | 1.270       | 2.03        | Reference | 0.050  | 0.080 | Reference |  |  |

| s <sub>1</sub> | 1.14        | 1.93        | Reference | 0.045  | 0.076 | Reference |  |  |

FIGURE 1. Case outline - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-93105 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | C              | 11         |

#### Device types 01 and 02

Case X

17 7 9 11 12 13 14 15 16 Z 3 5 8 10 v<sub>ss</sub> ٧ss ۷<sub>SS</sub> ٧ss AD5= VSS A6 A4 A27 ASB AZ3 NC A14 A12 v<sub>ss</sub> v<sub>\$\$</sub> A10 S 0 Ο 0 0 0 0 0 О 0 Q 0 0 0 0 0 О 0 AZS VCC VCC AS BLAST NC vcc vcc vcc VCC A11 A8 VSS A18 V<sub>CC</sub> A15 A28 0 0 0 0 ٥ 0 0 0 0 0 0 0 0 V<sub>SS</sub> A17 A19 A21 A24 A22 A20 A16 A13 A9 A5 A7 AZ BREG PLOCK\* PCHK\* A31 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 vcc vss HLDA 00 PS4 0A30 0 0 0 О 0 О LOCK- M/10- H/R-DΖ 01 DPO 0 0 0 0 0 0 D/C= V<sub>CC</sub> v<sub>ss</sub> ٧ss Vcc 04 0 0 0 0 0 0 PHT VCC  $v_{ss}$ ۷ss 97 06 0 0 0 0 0 0 BEO- VCC VSS vcc **Y**SS 014 0 0 0 0 0 0 BE2= BE1= PCD V<sub>CC</sub> D5 016 BOTTOM VIEW 0 0 0 0 0 0 BRDY= V<sub>CC</sub> V<sub>SS</sub> ٧ss 03 OPZ 0 0 0 0 0 v<sub>¢¢</sub> vcc vss  $\mathsf{v}_{\mathsf{s}\mathsf{s}}$ NC 012 G 0 0 0 ٥ 0 Ò KEN= ROY= BE3= DP1 08 015 0 0 0 0 0 О v<sub>ss</sub>  $\mathsf{v}_{\mathsf{SS}}$ HOLD VCC v<sub>CC</sub> 010 0 0 Ε O 0 0 0 AZOM= BS8= BOFF= 09 013 017 0 0 0 0 0 0 NC FERR# FLUSH#RESET BS16# CLK VCC VCC 027 026 028 030 NC NC NC 011 018 0 0 0 С 0 0 0 0 0 Ö o 0 О O 0 0 0 0 019 021 vss. ۷ss ۷ss 025 V<sub>CC</sub> 031 v<sub>CC</sub> МÇ VCC NC NC NC NM I NC EADS= 0 0 O 0 0 О 0 0 0 0 0 0 О 0 0 0 0 NC IGNNE" INTR AHOLD V<sub>SS</sub> 029 v<sub>SS</sub> v<sub>ss</sub> DZO DZZ NC D23 DP3 DZ4 NC NÇ NC 0 0 0 0 0 0 0 0 0 0 0 0 0 6 8 9 10 11 12 13 14 15 16 17

Note:

The # sign denotes an active low pin.

Figure 2. <u>Terminal connections</u>.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-93105 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | RÉVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | C              | 12         |

## Device types D3 and D4

Case X

| • | 1                    | Z                    | 3                    | 4               | 5               | 6               | 7                    | 8                    | 9                    | 10              | 11                   | 12              | 13      | 14              | 15         | 16                | 17                   |

|---|----------------------|----------------------|----------------------|-----------------|-----------------|-----------------|----------------------|----------------------|----------------------|-----------------|----------------------|-----------------|---------|-----------------|------------|-------------------|----------------------|

|   | A27                  | AZS                  | AZ3                  | NÇ              | A14             | v <sub>ss</sub> | A1Z                  | v <sub>ss</sub>      | ٧ss                  | v <sub>ss</sub> | v <sub>ss</sub>      | v <sub>ss</sub> | A10     | ٧,,             | A6         | A4                | ADS=                 |

| S | O<br>858             | O<br>A25             | v <sub>cc</sub>      | o<br>Vss        | 0               | ν <sub>cc</sub> | O<br>A15             | ν <sub>CC</sub><br>Ο | v <sub>cc</sub>      | ν <sub>CC</sub> | ν <sub>CC</sub>      | 0<br>A11        | O<br>88 | V <sub>CC</sub> | 0          | O<br>BLAST        | O NC                 |

| R | O<br>A31             | o<br>v <sub>ss</sub> | O<br>A17             | 0               | O<br>421        | 0               | O<br>35A             | O<br>AZ0             | 0                    | O<br>A13        | O<br>89              | O<br>A5         | O<br>A7 | 0               | 0          | O                 | 0                    |

| 0 | 0                    | O<br>A29             | O<br>A30             | 0               | 0               | 0               | 0                    | 0                    | 0                    | 0               | 0                    | 0               | 0       | ō               | O          | V <sub>CC</sub>   | o<br>v <sub>ss</sub> |

| P | 0                    | O<br>91              | O<br>DPO             |                 |                 |                 |                      |                      |                      |                 |                      |                 |         | L               | O<br>.8CK= | O<br>H/10:        | 0                    |

| N | o<br>V <sub>SS</sub> | ٥<br>٧               | O<br>04              |                 |                 |                 |                      |                      |                      |                 |                      |                 |         |                 | 0/C        | . v <sub>cc</sub> | v <sub>55</sub>      |

| н | o<br>V <sub>SS</sub> | 0                    | O<br>07              |                 |                 |                 |                      |                      |                      |                 |                      |                 |         |                 | O<br>Phit  | ٥<br>٧            | o<br>v <sub>ss</sub> |

| L | o<br>v <sub>ss</sub> | o<br>v <sub>cc</sub> | O<br>014             |                 |                 |                 |                      |                      |                      |                 |                      |                 |         |                 | O<br>860:  | 0                 | o<br>v <sub>ss</sub> |

| K | o<br>V <sub>CC</sub> | 05                   | O<br>016             |                 |                 |                 |                      |                      |                      |                 |                      |                 |         |                 | O<br>BEZ=  | 0<br>8E1=         | 0                    |

| J | o<br>v <sub>ss</sub> | O<br>03              | 0<br>0P2             |                 |                 |                 |                      |                      |                      |                 |                      |                 |         |                 | O<br>Broy= | v <sub>cc</sub>   | v <sub>ss</sub>      |

| H | v <sub>S</sub> S     | о<br>У <sub>СС</sub> | 0<br>012             |                 |                 |                 |                      |                      |                      |                 |                      |                 |         |                 | NC<br>NC   | ν <sub>CC</sub>   | v <sub>ss</sub>      |

| G | O<br>OP1             | 08                   | O<br>015             |                 |                 |                 |                      |                      |                      |                 |                      |                 |         |                 | O<br>KEN=  | O ROY=            | 0                    |

| F | o<br>v <sub>ss</sub> | о<br><sup>v</sup> cc | O<br>010             |                 |                 |                 |                      |                      |                      |                 |                      |                 |         |                 | HOLD       | 0                 | v <sub>ss</sub>      |

| E | 0                    | O<br>D13             | O<br>B17             |                 |                 |                 |                      |                      |                      |                 |                      |                 |         | ,               | O<br>420H= | O<br>858=         | 0<br>50FF=           |

| D | 0                    | O<br>018             | O<br>CLK             | v <sub>cc</sub> | v <sub>cc</sub> | 027             | DZ6                  | 028                  | 030                  | NC              | NC                   | NÇ              | NC      | FERR=           | O<br>FLUSH | O<br>HE RESE      | O<br>T 8516#         |

| C | 019                  | 0                    | o<br>v <sub>ss</sub> | vss             | v <sub>ss</sub> | 0               | o<br>VCC             | O<br>031             | V <sub>CC</sub>      | O<br>NC         | o<br>V <sub>CC</sub> | O<br>NC         | O       | O<br>THS        | O<br>NMI   | O<br>100          | O<br>EADS=           |

| 8 | 0 020                | O<br>DZZ             | O                    | 0               | 0               | O<br>D24        | o<br>V <sub>SS</sub> | O<br>029             | o<br>v <sub>ss</sub> | O<br>NC         | o<br>v <sub>ss</sub> | O<br>NC         | O<br>NC | O<br>101        | O          | O<br>= INTR       | O<br>AHOLD           |

| A | 0                    | 0                    | 0                    | 0               | 0               | 0               | ō                    | ō                    | ő                    | ō               | o                    | ō               | ō       | 0               | 0          | 0                 | 0                    |

|   | 1                    | 2                    | 3                    | 4               | 5               | 6               | 7                    | 8                    | 9                    | 10              | 11                   | 12              | 13      | 14              | 15         | 16                | 17                   |

FIGURE 2. <u>Ierminal connections</u>. - Continued

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-93105 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | C              | 13         |

Device types 05, 06, 07, 08, 09 and 10

Case X

| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                       |         |                   |                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------|-----------------|

| S                                                                                                                                                                                                           | A6      | A4                | ADS=            |

| A31 V <sub>SS</sub> A17 A19 A21 A24 A22 A20 A16 A13 A9 A5 A7 A2  O O O O O O O O O O O O O O O  DO A29 A30  O D2 D1 DP0  L O O O O  V <sub>SS</sub> V <sub>CC</sub> D4 O O O O  V <sub>SS</sub> D6 D7 O O O | 0       | O<br>LAST=        | O<br>NE         |

| O O O O O O O O O O O O O O O O O O O                                                                                                                                                                       | 0       | O                 | O PCHK=         |

| O O O O DZ D1 DPO L O O O O V <sub>SS</sub> V <sub>CC</sub> D4 O O O V <sub>SS</sub> D6 D7 O O O                                                                                                            | 0       | 0                 | 0               |

| DZ D1 OPO L O O O V <sub>SS</sub> V <sub>CC</sub> D4 O O O V <sub>SS</sub> D6 D7 O O O                                                                                                                      |         |                   | v <sub>ss</sub> |

| O O O  V <sub>SS</sub> V <sub>CC</sub> D4  O O O  V <sub>SS</sub> D6 D7  O O O                                                                                                                              | 0       | 0                 | 0               |

| V <sub>SS</sub> V <sub>CC</sub> D4 O O O V <sub>SS</sub> D6 D7 O O O                                                                                                                                        | .OCK= M | <del>1</del> /10= | W/R=            |

| 0 0 0 0 V <sub>SS</sub> 06 07 0 0                                                                                                                                                                           | 0       | 0                 | 0               |

| V <sub>SS</sub> D6 D7                                                                                                                                                                                       | D/C+    | v <sub>CC</sub>   | v <sub>ss</sub> |

| 0 0 0                                                                                                                                                                                                       | 0       | 0                 | 0               |

| 0 0 0                                                                                                                                                                                                       |         |                   | v <sub>ss</sub> |

|                                                                                                                                                                                                             | 0       | Ö                 | ő               |

|                                                                                                                                                                                                             | 8E0=    |                   | v <sub>ss</sub> |

| 0 0 0                                                                                                                                                                                                       | 0       | 0                 | 0               |

| 1                                                                                                                                                                                                           |         | BE1=              | PCD             |

|                                                                                                                                                                                                             | 0       | 0                 | 0               |

| 1                                                                                                                                                                                                           |         |                   | vss             |

| 1 33 55 5.4                                                                                                                                                                                                 |         |                   |                 |

|                                                                                                                                                                                                             | 0       | 0<br>V            | 0               |

| 11 12                                                                                                                                                                                                       | TPCLK=  |                   | V <sub>SS</sub> |

| 0 0 0                                                                                                                                                                                                       | 0       | 0                 | 0               |

| DP1 D8 D15                                                                                                                                                                                                  | KEN- !  |                   | BE3=            |

| 0 0 0                                                                                                                                                                                                       | 0       | 0                 | 0               |

| Y <sub>SS</sub> Y <sub>CC</sub> D10                                                                                                                                                                         | HOLD '  | <b>V</b> CC       | v <sub>SS</sub> |

| 0 0 0                                                                                                                                                                                                       | 0       | 0                 | 0               |

| D9 D13 D17 A                                                                                                                                                                                                | -MOSA   | 8S8 <b>=</b>      | BOFF=           |

| 0 0 0                                                                                                                                                                                                       | 0       | 0                 | 0               |

| D11 D18 CLK VCC VCC D27 D26 D28 D30 SRESET NC SMIACT= NC FERR=                                                                                                                                              | FLUSH#  |                   | T 8516=         |

| 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                   | 0       | 0                 | 0               |

| DIS DEL VSS VSS VSS DES VCC DEL VCC SMI - VCC NC NC THS                                                                                                                                                     |         | TDO               | EADS=           |

|                                                                                                                                                                                                             | 0       | 0                 | 0               |

|                                                                                                                                                                                                             |         |                   | ŀ               |

| 33 525 33                                                                                                                                                                                                   | IGNNE = |                   | 1               |

|                                                                                                                                                                                                             | 0       | 0                 | °               |

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14                                                                                                                                                                            |         |                   | ļ               |

Figure 2. <u>Terminal connections</u> - Continued

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-93105 |

|----------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |           | C              | 14         |

| Case<br>outlines   |                    |                    |                    |                    | -                  | Y                  |                    |                    |                    |                    |                    |

|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| Device<br>types    |                    | <del></del>        |                    |                    |                    | 01 and 02          | 2                  |                    |                    |                    |                    |

| Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol |

| 1                  | D21                | 34                 | N/C                | 67                 | W/R#               | 100                | BLAST#             | 133                | VSS                | 166                | Vss                |

| 2                  | D22                | 35                 | v <sub>ss</sub>    | 68                 | v <sub>ss</sub>    | 101                | ADS#               | 134                | N/C                | 167                | 05                 |

| 3                  | D23                | 36                 | N/C                | 69                 | HLDA               | 102                | A2                 | 135                | v <sub>cc</sub>    | 168                | Vcc                |

| 4                  | DP3                | 37                 | Vcc                | 70                 | Vcc                | 103                | A3                 | 136                | N/C                | 169                | D6                 |

| 5                  | D24                | 38                 | N/C                | 71                 | CLK                | 104                | A4                 | 137                | v <sub>ss</sub>    | 170                | V <sub>SS</sub>    |

| 6                  | D25                | 39                 | VSS                | 72                 | Vss                | 105                | v <sub>ss</sub>    | 138                | A18                | 171                | D7                 |

| 7                  | v <sub>ss</sub>    | 40                 | N/C                | 73                 | V <sub>SS</sub>    | 106                | A5                 | 139                | Vcc                | 172                | Vcc                |

| 8                  | D26                | 41                 | v <sub>cc</sub>    | 74                 | v <sub>cc</sub>    | 107                | Vcc                | 140                | A19                | 173                | DP1                |

| 9                  | v <sub>cc</sub>    | 42                 | N/C                | 75                 | v <sub>cc</sub>    | 108                | N/C                | 141                | vss                | 174                | VSS                |

| 10                 | D27                | 43                 | v <sub>ss</sub>    | 76                 | Vss                | 109                | V <sub>SS</sub>    | 142                | A20                | 175                | D8                 |

| 11                 | VSS                | 44                 | N/C                | 77                 | N/C                | 110                | A6                 | 143                | A21                | 176                | V <sub>CC</sub>    |

| 12                 | D28                | 45                 | N/C                | 78                 | v <sub>cc</sub>    | 111                | Vcc                | 144                | A22                | 177                | 09                 |

| 13                 | v <sub>cc</sub>    | 46                 | IMN                | 79                 | N/C                | 112                | Α7                 | 145                | A23                | 178                | vss                |

| 14                 | D29                | 47                 | INTR               | 80                 | v <sub>ss</sub>    | 113                | v <sub>ss</sub>    | 146                | A24                | 179                | D10                |

| 15                 | V <sub>SS</sub>    | 48                 | FLUSH#             | 81                 | AHOLD              | 114                | A8                 | 147                | A25                | 180                | v <sub>cc</sub>    |

| 16                 | D30                | 49                 | RESET              | 82                 | vcc                | 115                | v <sub>cc</sub>    | 148                | A26                | 181                | D11                |

| 17                 | v <sub>cc</sub>    | 50                 | A20M#              | 83                 | HOLD               | 116                | A9                 | 149                | A27                | 182                | Vss                |

| 18                 | D31                | 51                 | EADS#              | 84                 | V <sub>SS</sub>    | 117                | v <sub>ss</sub>    | 150                | A28                | 183                | D12                |

| 19                 | ٧ss                | 52                 | PCD                | 85                 | KEN#               | 118                | A10                | 151                | A29                | 184                | v <sub>cc</sub>    |

| 20                 | IGNNE#             | 53                 | PWT                | 86                 | v <sub>cc</sub>    | 119                | v <sub>cc</sub>    | 152                | A30                | 185                | 013                |

| 21                 | v <sub>cc</sub>    | 54                 | D/C#               | 87                 | RDY#               | 120                | A11                | 153                | A31                | 186                | ٧ <sub>SS</sub>    |

| 22                 | N/C                | 55                 | M/IO#              | 88                 | V <sub>SS</sub>    | 121                | V <sub>SS</sub>    | 154                | v <sub>ss</sub>    | 187                | D14                |

| 23                 | ٧ <sub>SS</sub>    | 56                 | v <sub>ss</sub>    | 89                 | N/C                | 122                | A12                | 155                | DP0                | 188                | Vcc                |

| 24                 | N/C                | 57                 | BE3#               | 90                 | v <sub>cc</sub>    | 123                | v <sub>cc</sub>    | 156                | v <sub>cc</sub>    | 189                | D15                |

| 25                 | v <sub>cc</sub>    | 58                 | v <sub>cc</sub>    | 91                 | BS8#               | 124                | A13                | 157                | DO                 | 190                | ٧ <sub>SS</sub>    |

| 26                 | FERR#              | 59                 | BE2#               | 92                 | V <sub>SS</sub>    | 125                | ٧ <sub>SS</sub>    | 158                | v <sub>ss</sub>    | 191                | DP2                |

| 27                 | v <sub>ss</sub>    | 60                 | ٧ <sub>SS</sub>    | 93                 | BS16#              | 126                | A14                | 159                | D1                 | 192                | D16                |

| 28                 | N/C                | 61                 | BE1#               | 94                 | BOFF#              | 127                | v <sub>cc</sub>    | 160                | v <sub>cc</sub>    | 193                | D17                |

| 29                 | v <sub>CC</sub>    | 62                 | v <sub>cc</sub>    | 95                 | 8RDY#              | 128                | A15                | 161                | 02                 | 194                | D18                |

| 30                 | N/C                | 63                 | BEO                | 96                 | PCHK#              | 129                | ٧ <sub>SS</sub>    | 162                | v <sub>ss</sub>    | 195                | D19                |

| 31                 | v <sub>ss</sub>    | 64                 | ٧ss                | 97                 | N/C                | 130                | A16                | 163                | 03                 | 196                | D20                |

| 32                 | N/C                | 65                 | BREQ               | 98                 | LOCK#              | 131                | vcc                | 164                | vcc                |                    |                    |

| 33                 | VCC                | 66                 | VCC                | 99                 | PLOCK#             | 132                | A17                | 165                | D4                 |                    |                    |

FIGURE 2. <u>Terminal connections</u> - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-93105 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | C              | 15         |

| Case<br>outlines   | Y                  |                    |                    |                    |                    |                    |                    |                    |                    |                    |                    |

|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| Device<br>types    |                    |                    |                    |                    |                    | 03 and 04          | •                  |                    |                    |                    |                    |

| Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol | Terminat<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol |

| 1                  | D21                | 34                 | N/C                | 67                 | W/R#               | 100                | BLAST#             | 133                | V <sub>SS</sub>    | 166                | V <sub>SS</sub>    |

| 2                  | D22                | 35                 | vss                | 68                 | v <sub>ss</sub>    | 101                | ADS#               | 134                | TDI                | 167                | 05                 |

| 3                  | D23                | 36                 | N/C                | 69                 | HLDA               | 102                | A2                 | 135                | Vcc                | 168                | vcc                |

| 4                  | DP3                | 37                 | v <sub>cc</sub>    | 70                 | Vcc                | 103                | A3                 | 136                | TMS                | 169                | D6                 |

| 5                  | D24                | 38                 | N/C                | 71                 | CLK                | 104                | A4                 | 137                | v <sub>ss</sub>    | 170                | Vss                |

| 6                  | D25                | 39                 | ٧ <sub>SS</sub>    | 72                 | V <sub>SS</sub>    | 105                | ٧ss                | 138                | A18                | 171                | 07                 |

| 7                  | VSS                | 40                 | N/C                | 73                 | v <sub>ss</sub>    | 106                | A5                 | 139                | v <sub>cc</sub>    | 172                | vcc                |