# PRELIMINARY DATASHEET

### CGY2139AUH/C2

8-12 GHz 41dBm Power Amplifier

#### **DESCRIPTION**

The CGY2139AUH/C2 is a high performance dual line-up 3 stages GaAs Power Amplifier MMIC designed to operate in the X band.

The CGY2139AUH/C2 has an output power of 12 W at the 1dB compression point and has a small signal gain of 25 dB. It can be used in X-band Radars, Telecommunication and Instrumentation applications.

The MMIC uses gold bonding pads and backside metallization and is fully protected with Silicon Nitride passivation to obtain the highest level of reliability.

The MMIC power dissipation is limited by the die thermal resistance, it has been designed to work in pulse mode, The CGY2139AUH/C2 can be operated at a duty cycle as high as 50%. Drain switch mode is the preferred control mode.

Cascading CGY2139PUH/C1 or CGY2139MUH/C1 with CGY2139AUH/C2 can form a 40dB gain 12W X-band pulse mode amplifier chain.

#### **APPLICATIONS**

- Radar

- Telecommunications

- Instrumentation

Website: www.ommic.com

#### **FEATURES**

Operating Range : 8 GHz to 12 GHz

Output P<sub>sat</sub>: 41.2 dBmOutput P<sub>1dB</sub>: 41 dBm

▶ Gain: 25 dB

▶ 50 Ohms input and output matched

▶ Input Return Loss : > 10 dB

Output Return Loss: > 10 dB

Power Supply: 4.2 A at VDD = 8.5 V

Die size = 4.5 x 4.1 x 0.1 mm

Device Availability (Q3 2013) :

o Tested, Inspected Known Good Die (KGD)

Connectorized evaluation solution

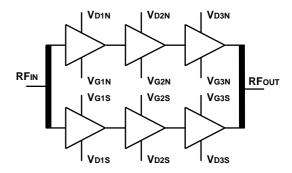

CGY2139AUH/C2 Power Amplifier Block Diagram

Fmail: information@ommic.com

**Revision**: 04/12/2013 **OMMIC**

2, Rue du Moulin – BP11 – 94 453 Limeil-Brévannes Cedex – France

2/15

#### **MAXIMUM VALUES**

| Symbol                                                                                                             | Parameter            | Conditions | MIN.  | MAX.  | UNIT |

|--------------------------------------------------------------------------------------------------------------------|----------------------|------------|-------|-------|------|

| V <sub>G1N</sub> , V <sub>G2N</sub> , V <sub>G3N</sub> ,<br>V <sub>G1S</sub> , V <sub>G2S</sub> , V <sub>G3S</sub> | Gate voltage         |            | - 2,5 | 0     | V    |

| V <sub>D1N</sub> , V <sub>D2N</sub> , V <sub>D3N</sub> , V <sub>D1S</sub> , V <sub>D2S</sub> , V <sub>D3S</sub>    | Drain voltage        |            | 0     | + 9   | V    |

| ID1N, ID1S                                                                                                         |                      |            |       | 200   |      |

| ID2N, ID2S                                                                                                         | Drain current        |            |       | 600   | mA   |

| Idan, Idas                                                                                                         |                      |            |       | 1800  |      |

| IGNN, s (all gates)                                                                                                | Gate Current         |            | - 10  | + 10  | mA   |

| P <sub>IN</sub>                                                                                                    | RF Input power       |            |       | + 23  | dBm  |

| Tamb                                                                                                               | Ambient temperature  |            | - 40  | + 85  | °C   |

| Tj                                                                                                                 | Junction temperature |            |       | + 150 | °C   |

| T <sub>stg</sub>                                                                                                   | Storage temperature  |            | - 55  | + 85  | °C   |

Operation of this device outside the parameter ranges given above may cause permanent damage

#### THERMAL CHARACTERISTICS

| Symbol        | Parameter                                                          |     | UNIT |

|---------------|--------------------------------------------------------------------|-----|------|

| Rth (j - amb) | Thermal resistance from junction to ambient (DC power at Tamb max) | TBD | °C/W |

#### **ELECTRICAL CHARACTERISTICS**

Conditions: T<sub>amb</sub> = + 25 ℃, I<sub>DQ3N</sub>, I<sub>DQ3S</sub> = 1400mA, I<sub>DQ2N</sub>, I<sub>DQ2S</sub> = 400mA, I<sub>DQ1N</sub>, I<sub>DQ1S</sub> = 125mA, 10% duty cycle

| Symbol                                                                                              | Parameter                              | Conditions         | MIN. | TYP. | MAX. | UNIT |

|-----------------------------------------------------------------------------------------------------|----------------------------------------|--------------------|------|------|------|------|

| RFin                                                                                                | Input frequency                        |                    | 8    |      | 12   | GHz  |

| Performances on Reference Board at f <sub>i</sub> = 10 GHz, Drain voltage 8.5V (gate voltage -0.7V) |                                        |                    |      |      |      |      |

| V <sub>D1N, 2N, 3N</sub><br>V <sub>D1S, 2S, 3S</sub>                                                | Drain Supply voltage                   |                    |      |      | 8.5  | V    |

| I <sub>DD</sub>                                                                                     | Total supply current @ Psat            | Drain voltage 8.5V |      | 4.3  | 5.0  | Α    |

| G                                                                                                   | Gain                                   |                    | 22   | 25   |      | dB   |

| NF                                                                                                  | Noise Figure                           |                    |      | TBD  |      | dB   |

| P1dB                                                                                                | 1dB compression point                  |                    |      | 41   |      | dBm  |

| Psat                                                                                                | Saturated power                        |                    |      | 41.2 |      | dBm  |

| PAE                                                                                                 | Power Added Efficiency                 |                    |      | 36   |      | %    |

| OIP3                                                                                                | Output third order intercept point     |                    |      | 50   |      | dBm  |

| IMD3                                                                                                | 2 Carriers 3 dB below P1dB             |                    |      | TBD  |      | dBc  |

| ISO <sub>rev</sub>                                                                                  | Reverse Isolation                      | RFOUT/RFIN         |      | TBD  |      | dB   |

| S <sub>11</sub>                                                                                     | Input reflection coefficient           | 50 Ohms            |      | -10  |      | dB   |

| S <sub>22</sub>                                                                                     | Output reflection coefficient          | 50 Ohms            |      | -10  |      | dB   |

| P <sub>OFF</sub>                                                                                    | Leakage when HPA off All gates = -2,5V | RFIN = + 20 dBm    |      | TBD  |      | dBm  |

<sup>(\*)</sup> Measurement reference planes are the INPUT and OUTPUT plans of the CGY2139AUH/C2 MMIC.

**Caution :** This device is a high performance RF component and can be damaged by inappropriate handling. Standard ESD precautions should be followed. OMMIC document "OM-CI-MV/ 001/ PG" contains more information on the precautions to take.

3/15

CGY2139AUH/C2 can only be measured on-wafer using a pulse measurement test-bench, this method assure a full polarization conditions and cold channel temperature, this method also remove the risk of reliability damages due to high temperature overstress inherent to on wafer measurements at full polarization and reflects the performances of the devices in good cooling conditions.

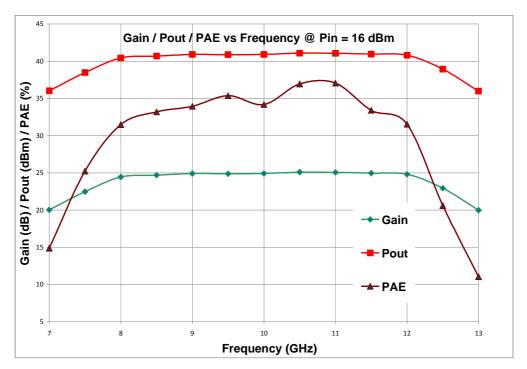

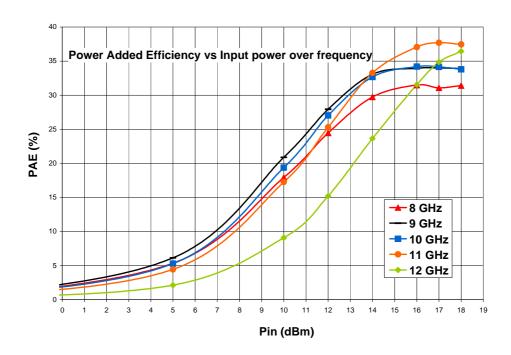

#### **OUTPUT POWER, GAIN AND PAE**

Conditions: On Carrier measurements with 50 Ohms probes

VD3N, VD3S = VD2N, VD2S = VD1N, VD1S = 8.5V, VG3N, VG3S = VG2N, VG2S = VG1N, VG1S = -0.7V, (IDQ3N + IDQ3S + IDQ2N + IDQ1S = 3800 mA, duty cycle 10%,  $T_{amb} = +25\%$

Gain, Pout and PAE vs frequency

Note: Input power at 16dBm is near P1dB compression point.

Website: www.ommic.com

4/15

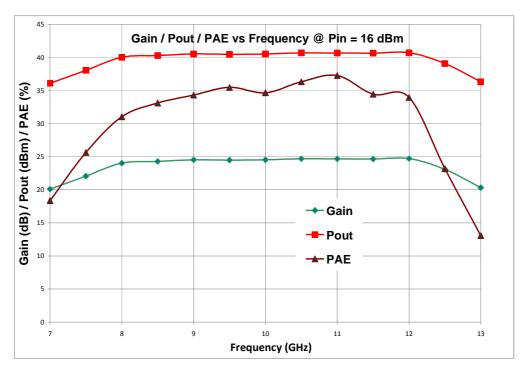

Conditions: On Carrier measurements with 50 Ohms probes

$V_{D3N}, V_{D3S} = V_{D2N}, V_{D2S} = V_{D1N}, V_{D1S} = 8.0V, V_{G3N}, V_{G3S} = V_{G2N}, V_{G2S} = V_{G1N}, V_{G1S} = -0.7V, (I_{DQ3N} + I_{DQ2S} + I_{DQ1N} + I_{DQ1S} = 3800 \text{ mA}, duty cycle 10\%, T_{amb} = +25\%$

Gain, Pout and PAE vs Frequency

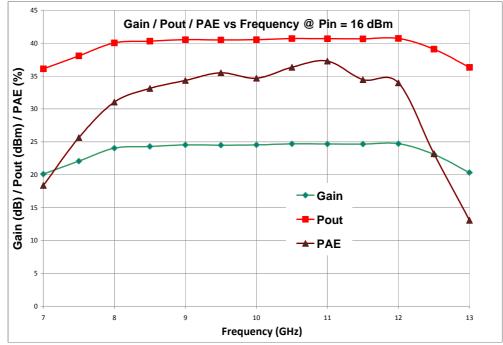

Conditions: On Carrier measurements with 50 Ohms probes

Website: www.ommic.com

$V_{D3N}, V_{D3S} = V_{D2N}, V_{D2S} = V_{D1N}, V_{D1S} = 7.5V, V_{G3N}, V_{G3S} = V_{G2N}, V_{G2S} = V_{G1N}, V_{G1S} = -0.7V, (I_{DQ3N} + I_{DQ2S} + I_{DQ2N} + I_{DQ1S} + I_$

Gain, Pout and PAE vs Frequency

5 / 15

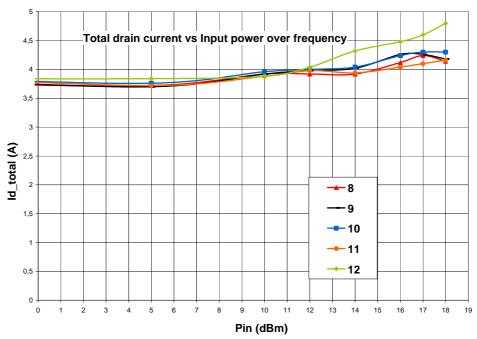

#### **CURRENT CONSUMPTION**

Conditions: On Carrier measurements with 50 Ohms probes

$V_{D3N}, V_{D3S} = V_{D2N}, V_{D2S} = V_{D1N}, V_{D1S} = 8.5V, V_{G3N}, V_{G3S} = V_{G2N}, V_{G2S} = V_{G1N}, V_{G1S} = -0.7V, (I_{DQ3N} + I_{DQ2N} + I_{DQ2N} + I_{DQ1S} + I_{DQ1N} + I_{DQ1S} = 3800 \text{ mA}, duty cycle 10\%, T_{amb} = +25\%$

#### Total current vs Input power over frequency

Conditions: On Carrier measurements with 50 Ohms probes

Website: www.ommic.com

$V_{D3N}, V_{D3S} = V_{D2N}, V_{D2S} = V_{D1N}, V_{D1S} = 8.5V, V_{G3N}, V_{G3S} = V_{G2N}, V_{G2S} = V_{G1N}, V_{G1S} = -0.7V, (I_{DQ3N} + I_{DQ2S} + I_{DQ2N} + I_{DQ1S} + I_$

Website: www.ommic.com

### Preliminary Datasheet CGY2139AUH/C2

6/15

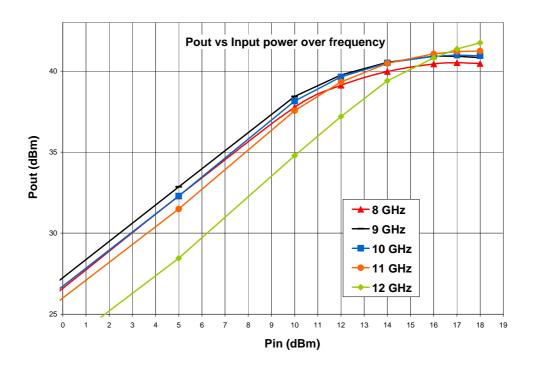

Conditions: On Carrier measurements with 50 Ohms probes

$V_{D3N}, V_{D3S} = V_{D2N}, V_{D2S} = V_{D1N}, V_{D1S} = 8.5V, V_{G3N}, V_{G3S} = V_{G2N}, V_{G2S} = V_{G1N}, V_{G1S} = -0.7V, (I_{DQ3N} + I_{DQ3S} + I_{DQ2N} + I_{DQ1S} + I_$

Pout vs Input power over frequency

7/15

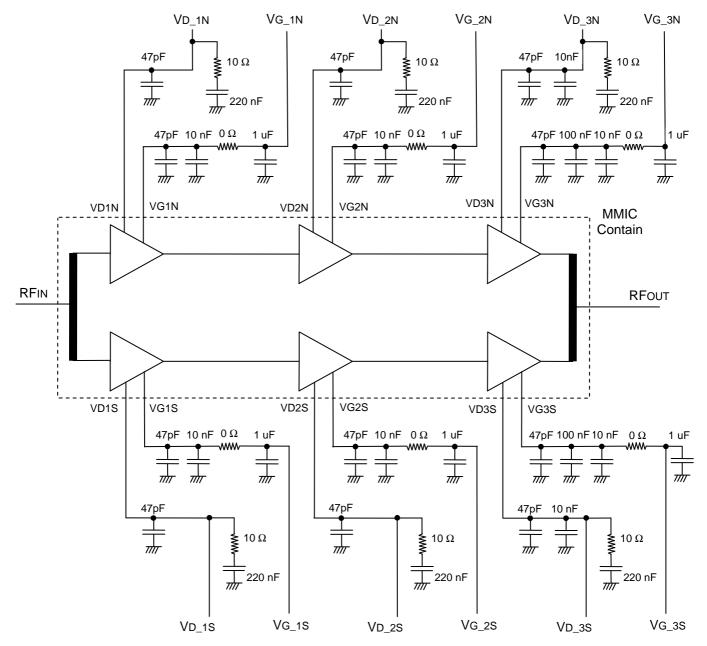

#### APPLICATION SCHEMATIC

Website: www.ommic.com

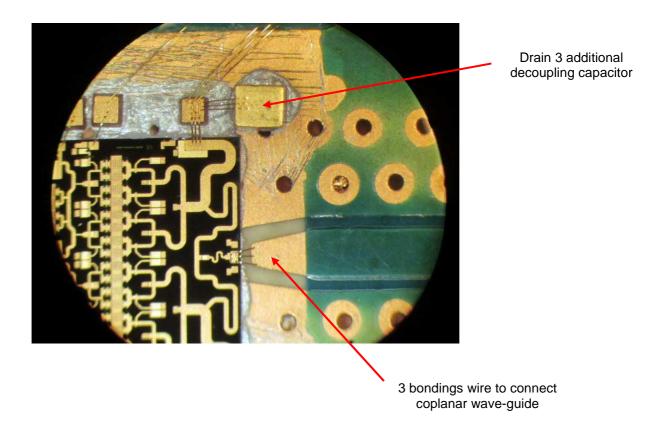

Decoupling scheme depends on customer implementation, in order to prevent unstability it is hightly recommended to place a 47pF RF decoupling chip capacitor at each DC terminal with the shortest possible bonding wires. Additionnally, a 10nF chip capacitor can be added on the drain 3 connection.

The decoupling network depends on supply, on grounding environement, on form factor, on all parasitics added by the customer environement. According to this, the appropriate network sometimes need to be fine-tuned in accordance with rules applyable in the high frequency domain.

It may also be required to add very low frequency, high capacitor value. On each drain a 10 Ohms / 10 nF RC serie network made of 0402 format capacitors have been implemented reference test-jig.

CGY2139AUH/C2 Application schematics

8/15

| Component NAME      | Value | Туре           | Comment                                                                                                                 |

|---------------------|-------|----------------|-------------------------------------------------------------------------------------------------------------------------|

| All 47pF capacitors | 47pF  | Chip Capacitor | Chip capacitor PRESIDIO COMPONENTS P/N SA151BX470M2HX5#013B soldered close to the die with bonding as short as possible |

| All 10nF capacitors | 10nF  | Chip Capacitor | MURATA GMA085R71C103MD01T<br>GM260 X7R 103M 16M100 PM520                                                                |

Due to the highly symmetrical design of the component and the requirements of the power combiner, it is recommended to keep the supply design as symmetrical as possible, this means IDQ1N equal to IDQ1S, IDQ2N equal to IDQ3S and IDQ3N equal to IDQ3S, for the same reason, it is recommended to keep VD1N equal the VD1S, VD2N equal the VD2S and VD3N equal the VD3S. It is important to keep VG1N equal the VG1S, VG2N equal the VG3S and VG3N equal the VG3S.

CGY2139AUH/C2 can be supplied with only a single pulsed Vd voltage and only a single Vg voltage. Nevertheless, it is very important to keep efficient decoupling networks on drain and gates. Improper decoupling networks can lead to oscillations through supply guided feedback loop.

CGY2139AUH/C2 have been designed to present a 50 Ohms plan at the die port. 2 to 3 standard wire bondings (25um in diameter 300um in length) can be used to connect the die to the environment (microstrip or coplanar). The wire bonding terminal (alumina or PCB substrate) should be build to compensate the inductance introduced by the wire bounding over the frequency band.

As the use of different Vg on each stage can be used to optimize a particular parameter corresponding to customer demand, all Vg are left available to the customer.

#### CW OPERATIONS

Website: www.ommic.com

CGY2139AUH/C2 doesn't support CW operation at full bias, reducing Idd using gate voltage (Vg) can be done, Idd reduced by 50% can be accepted to support CW operation.

9/15

#### **TEST JIG**

Website: www.ommic.com

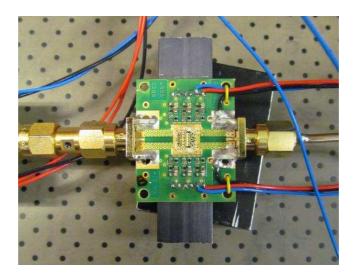

A Connecteurized test-jig have been developped, a picture is showed below.

The test-jig add losses, a probe have been build to evaluate the losses: 0.7dB have been found between die plan and SMA connector at both accesses (input and output).

Due to the smal heatsink implemented, the duty cycle of the test-jig is limited to 10%. Pulse width of 10us with a pulse repetition period of 100us are recommended

Website: www.ommic.com

### Preliminary Datasheet CGY2139AUH/C2

10 / 15

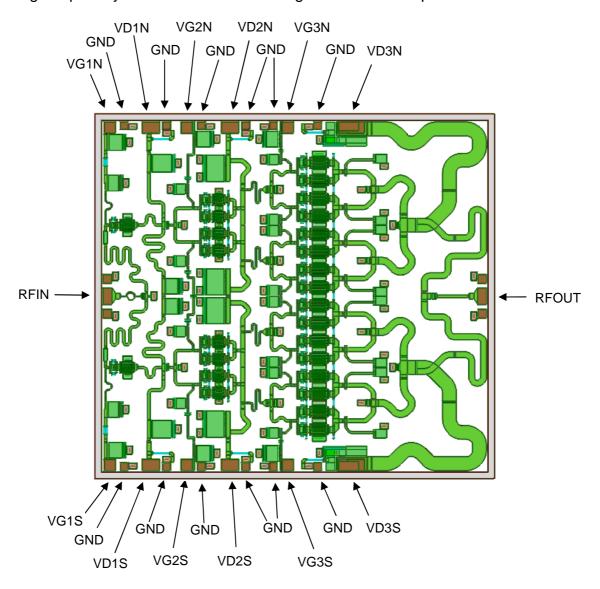

#### DIE LAYOUT AND PIN CONFIGURATION

The Die is symetrical on the RF axis. The die positionned top view with RF input on the left and RF output on the right show DC accesses on the top labelled north (N) and DC accesses on the bottom labelled south (S). VD1N, VD2N, VD3N, VG1N, VG2N, VG3N are DC signals applied on the north side, VD1S, VD2S, VG3S, VG1S, VG2S, VG3S are DC signals applied on the south side. Many ground accesses are complementing the pad layout. The backside is the ground reference plan.

CGY2139AUH/C2 Pad layout

11 / 15

#### **PINOUT**

The amplifier has a North face and a south face, north is top and south is bottom when RF input is on the left an RF output on the right.

| Symbol | Pad      | Description                          |

|--------|----------|--------------------------------------|

| RFOUT  | OUT      | RF output                            |

| RFIN   | IN       | RF input                             |

| VD1N   | VD1N     | First stage Drain (amplifier North)  |

| VD2N   | VD2N     | Second stage Drain (amplifier North) |

| VD3N   | VD3N     | Third stage Drain (amplifier North)  |

| VG1N   | VG1N     | First stage Gate (amplifier North)   |

| VG2N   | VG2N     | Second stage Gate (amplifier North)  |

| VG3N   | VG3N     | Third stage Gate (amplifier North)   |

| VD1S   | VD1S     | First stage Drain (amplifier South)  |

| VD2S   | VD2S     | Second stage Drain (amplifier South) |

| VD3S   | VD3S     | Third stage Drain (amplifier South)  |

| VG1S   | VG1S     | First stage Gate (amplifier South)   |

| VG2S   | VG2S     | Second stage Gate (amplifier South)  |

| VG3S   | VG3S     | Third stage Gate (amplifier South)   |

| GND    | BACKSIDE | Ground                               |

#### Note:

In order to ensure good RF performances and stability It is key to connect to the ground the pad available on the backside of the die.

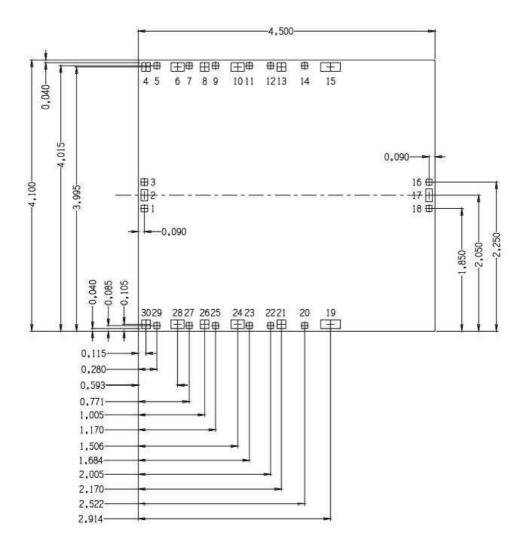

#### **BONDINGS PAD COORDINATES**

| Symbol | X coordinate (um) | Y coordinate (um) | Pad size (um x um)                  |

|--------|-------------------|-------------------|-------------------------------------|

| GND    | 90                | 1850              | Ground pad associated with RF input |

| RFIN   | 90                | 2050              | 100 x 190                           |

| GND    | 90                | 2250              | Ground pad associated with RF input |

| VG1N   | 115               | 3995              | 130 x 130                           |

| GND    | 280               | 4015              | 90 x 90                             |

| VD1N   | 595               | 3995              | 200 x 130                           |

| GND    | 771               | 4015              | 90 x 90                             |

| VG2N   | 1005              | 3995              | 130 x 130                           |

Website: www.ommic.com

## Preliminary Datasheet CGY2139AUH/C2

12 / 15

| GND   | 1170     | 4015 | 90 x 90                              |

|-------|----------|------|--------------------------------------|

| VD2N  | 1506     | 3995 | 200 x 130                            |

| GND   | 1684     | 4015 | 90 x 90                              |

| GND   | 2005     | 4015 | 90 x 90                              |

| VG3N  | 2170     | 3995 | 130 x 130                            |

| GND   | 2522     | 4015 | 90 x 90                              |

| VD3N  | 2914     | 3995 | 300 x 100                            |

| GND   | 4410     | 1850 | Ground pad associated with RF output |

| RFOUT | 4410     | 2050 | 100 x 190                            |

| GND   | 4410     | 2250 | Ground pad associated with RF output |

| GND   | BACKSIDE |      | Ground                               |

CGY2139AUH/C2 Pad size and coordinates

e-mail: information@ommic.com

13 / 15

#### **BONDINGS PAD DRAWING**

Website: www.ommic.com

MMIC Steps on the wafer are 4.5 and 4.1 mm along X and Y coordinated respectively, dicing typically reduce the die by 30um.

CGY2139AUH/C2 Pad layout drawing

14 / 15

#### **PACKAGE**

| Туре | Description                    | Terminals | Pitch (mm) | Package size<br>(mm) |

|------|--------------------------------|-----------|------------|----------------------|

| DIE  | 100% RF and DC on-wafer tested | 30        | -          | 4.5 x 4.1 x 0.1      |

#### **SOLDERING**

To avoid permanent damages or impact on reliability during soldering process, die temperature should never exceed 330℃.

Temperature in excess of 300℃ should not be applied to the die longer than 1mn

Toxic fumes will be generated at temperatures higher than 400℃

#### ORDERING INFORMATION

| Generic type | Package type | Version | Sort Type | Description           |

|--------------|--------------|---------|-----------|-----------------------|

| CGY2139A     | UH           | C2      | -         | On-Wafer measured Die |

| CGY2139A     | UH           | C2      | EK        | Test-jig              |

Website: www.ommic.com

e-mail: information@ommic.com

15/15

#### **DEFINITIONS**

#### Limiting values definition

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

#### **Application information**

Applications that are described herein for any of these products are for illustrative purposes only. OMMIC makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **DISCLAIMERS**

#### Life support applications

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. OMMIC's customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify OMMIC for any damages resulting from such application.

#### Right to make changes

OMMIC reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. OMMIC assumes no responsibility or liability for the use of any of these products, conveys no licence or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.