## **LXT350**

#### T1/E1 Short Haul Transceiver with Crystal-less Jitter Attenuation

#### **Datasheet**

The LXT350 is a full-featured, fully-integrated transceiver for T1 and E1 short-haul applications. The LXT350 is software switchable between T1 and E1 operation, and offers pulse equalization settings for all short-haul T1 and E1 line interface (LIU) applications.

LXT350 provides both a serial port for microprocessor control (Host mode) as well as standalone operation (Hardware mode). The device incorporates advanced crystal-less digital jitter attenuation in either the transmit or receive data path starting at 3 Hz. B8ZS/HDB3 encoding/decoding and unipolar or bipolar data I/O are selectable. Loss of signal monitoring and a variety of diagnostic loopback modes can also be selected.

## **Applications**

- SONET/SDH tributary interfaces

- Digital cross connects

- Public/private switching trunk line interfaces

- Microwave transmission systems

#### **Product Features**

- Fully integrated transceivers for Short-Haul T1 or E1 interfaces

- Crystal-less digital jitter attenuation

- -Select either transmit or receive path

- No crystal or high speed external clock required

- Meet or exceed specifications in ANSI T1.403 and T1.408; ITU I.431, G.703, G.736, G.775 and G.823; ETSI 300-166 and 300-233; and AT&T Pub 62411

- Supports 75  $\Omega$  (E1 coax), 100  $\Omega$  (T1 twisted-pair) and 120  $\Omega$  (E1 twisted-pair) applications

- Fully restores the received signal after transmission through a cable with attenuation of 18dB, at 1024 kHz

- Five pulse equalization settings for T1 short-haul applications

- Transmit/receive performance monitors with Driver Fail Monitor Open (DFM) and Loss of Signal (LOS) outputs

- Selectable unipolar or bipolar data I/O and B8ZS/HDB3 encoding/decoding

- QRSS generator/detector for testing or monitoring

- Output short circuit current limit protection

- Local, remote and analog loopback capability

- Compatible with Intel's LXT360/361 T1/ E1 long haul/short haul transceiver (Universal LIU)

- Multiple register serial interface for microprocessor control

- Available in 28-pin PLCC and 44-pin PQFP packages

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See <a href="https://www.intel.com/products/processor\_number">https://www.intel.com/products/processor\_number</a> for details.

The Intel® LXT350 Transceiver may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Intel and Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2006, Intel Corporation. All Rights Reserved.

| 1.0 | Pin As | ssignmer    | nts and Signal Descriptions                                | 8  |

|-----|--------|-------------|------------------------------------------------------------|----|

|     | 1.1    | Mode        | Dependent Signals                                          | 9  |

| 2.0 | Funct  | ional Des   | scription                                                  | 14 |

|     | 2.1    | Initializ   | zation                                                     | 14 |

|     |        | 2.1.1       | Reset Operation                                            | 14 |

|     | 2.2    | Transr      | mitter                                                     | 14 |

|     |        | 2.2.1       | Transmit Digital Data Interface                            | 14 |

|     |        | 2.2.2       | Transmit Monitoring                                        | 15 |

|     |        | 2.2.3       | Transmit Drivers                                           | 15 |

|     |        | 2.2.4       | Transmit Idle Mode                                         | 15 |

|     |        | 2.2.5       | Transmit Pulse Shape                                       | 15 |

|     | 2.3    | Receiv      | /er                                                        | 16 |

|     |        | 2.3.1       | Receive Data Recovery                                      | 16 |

|     |        | 2.3.2       | Receive Digital Data Interface                             | 16 |

|     | 2.4    | Jitter A    | Attenuation                                                | 16 |

|     | 2.5    | Hardw       | are Mode                                                   | 17 |

|     | 2.6    | Host N      | Node                                                       | 17 |

|     |        | 2.6.1       | Interrupt Handling                                         | 17 |

|     | 2.7    | Diagno      | ostic Mode Operation                                       | 19 |

|     |        | 2.7.1       | Loopback Modes                                             | 20 |

|     |        |             | 2.7.1.1 Local Loopback (LLOOP)                             | 20 |

|     |        |             | 2.7.1.2 Analog Loopback (ALOOP)                            |    |

|     |        |             | 2.7.1.3 Remote Loopback (RLOOP)                            |    |

|     |        |             | 2.7.1.4 Dual Loopback (DLOOP)                              |    |

|     |        | 2.7.2       | Internal Pattern Generation                                |    |

|     |        |             | 2.7.2.1 Transmit All Ones (TAOS)                           | 23 |

|     |        |             | 2.7.2.2 Quasi-Random Signal Source (QRSS)                  |    |

|     |        | 2.7.3       | Error Insertion and Detection                              |    |

|     |        |             | 2.7.3.1 Bipolar Violation Insertion (INSBPV)               |    |

|     |        |             | 2.7.3.2 Logic Error Insertion (INSLER)                     |    |

|     |        |             | 2.7.3.3 Logic Error Detection (QPD)                        |    |

|     |        |             | 2.7.3.4 Bipolar Violation Detection (BPV)                  |    |

|     |        |             | 2.7.3.6 HDB3 Zero Substitution Violation Detection (ZEROV) |    |

|     |        | 2.7.4       | Alarm Condition Monitoring                                 |    |

|     |        | 2.7.7       | 2.7.4.1 Loss of Signal (LOS)                               |    |

|     |        |             | 2.7.4.2 Alarm Indication Signal Detection (AIS)            | 26 |

|     |        |             | 2.7.4.3 Driver Failure Monitor Open (DFMO)                 |    |

|     |        |             | 2.7.4.4 Elastic Store Overflow/Underflow (ESOVR and ESUNF) |    |

|     |        |             | 2.7.4.5 Built-In Self Test (BIST)                          |    |

| 3.0 | Regis  | ter Defini  | itions                                                     | 28 |

| 4.0 | Applio | cation Info | ormation                                                   | 33 |

|     | 4.1    | Transr      | mit Return Loss                                            | 33 |

|     | 4.2    |             | ormer Data                                                 |    |

|     | 4.3    |             | ation Circuits                                             |    |

|     | -      |             |                                                            |    |

### LXT350 — T1/E1 Short Haul Transceiver with Crystal-less Jitter Attenuation

|         | 4.4     | Line Pr<br>4.4.1<br>4.4.2 | otection  Hardware Mode Application  Host Mode Application | . 35 |

|---------|---------|---------------------------|------------------------------------------------------------|------|

| 5.0     | Test Sp | oecificati                | ons                                                        |      |

| 6.0     | Mecha   | nical Spe                 | ecifications                                               | .49  |

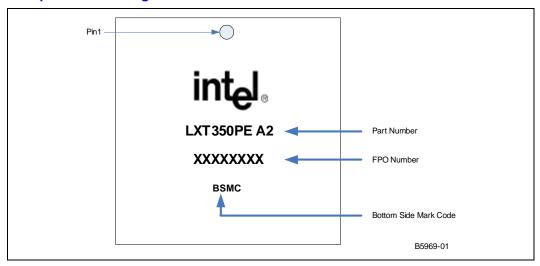

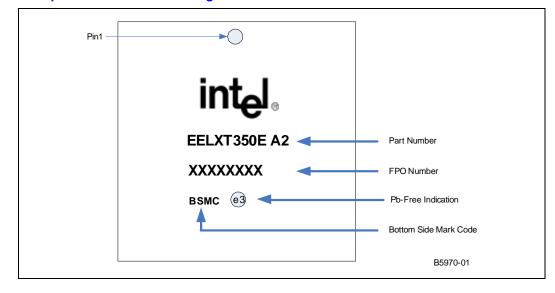

|         | 6.1     | -                         | pel Markings                                               |      |

|         |         | •                         | · ·                                                        |      |

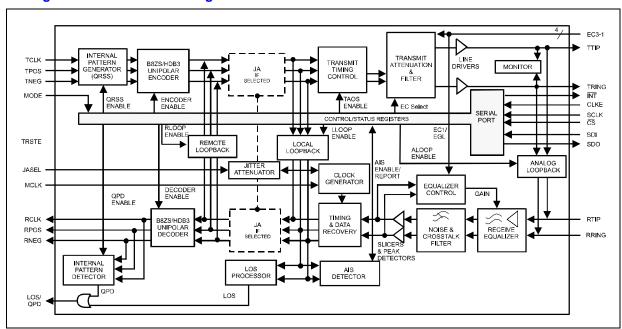

| 7.0     | Produc  | t Orderir                 | g Information                                              | .52  |

| Figures |         |                           |                                                            |      |

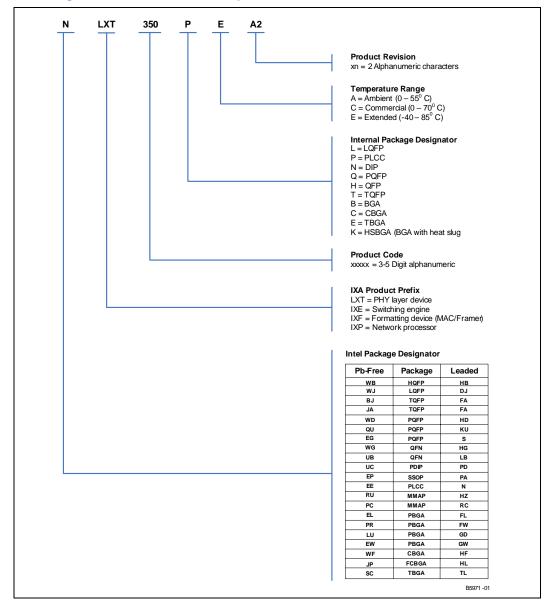

| igaioo  | 1       | I XT350                   | ) Block Diagram                                            | 7    |

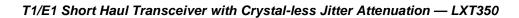

|         | 2       |                           | ) Pin Assignments                                          |      |

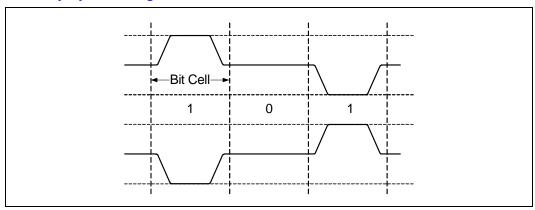

|         | 3       |                           | uty Cycle Coding                                           |      |

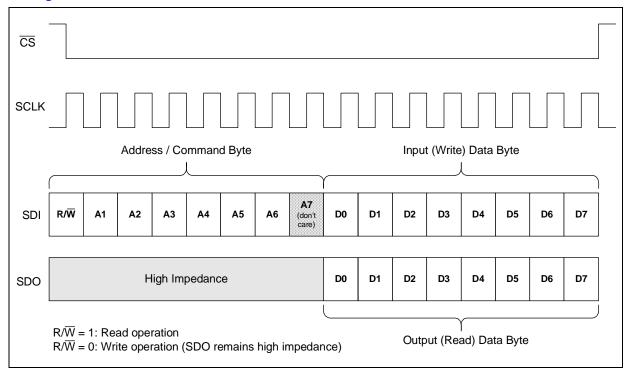

|         | 4       |                           | Port Data Structure                                        |      |

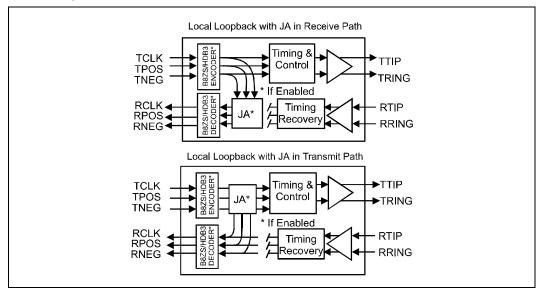

|         | 5       |                           | vith LLOOP                                                 |      |

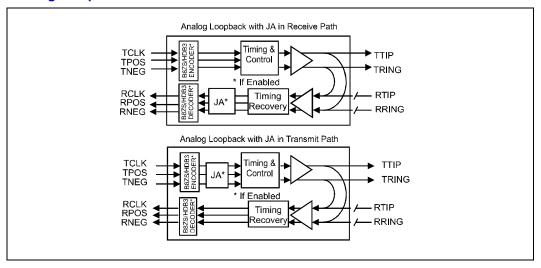

|         | 6       |                           | oopback                                                    |      |

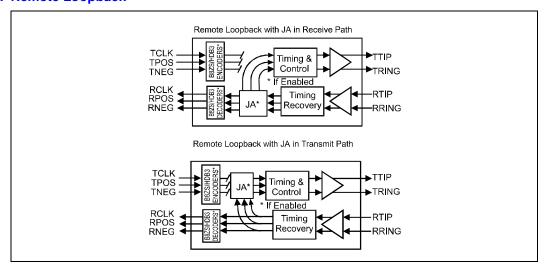

|         | 7       |                           | Loopback                                                   |      |

|         | 8       | •                         | e Loopback                                                 |      |

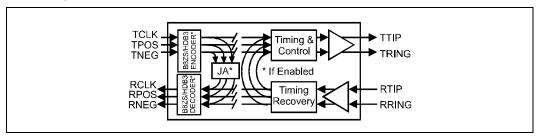

|         | 9       | Dual Lo                   | opback                                                     | . 23 |

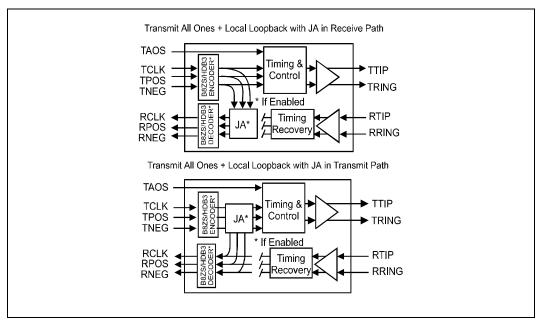

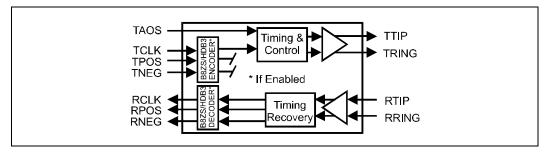

|         | 10      | TAOS I                    | Data Path                                                  | . 23 |

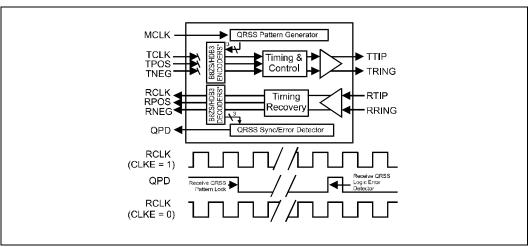

|         | 11      | QRSS                      | Mode                                                       | . 24 |

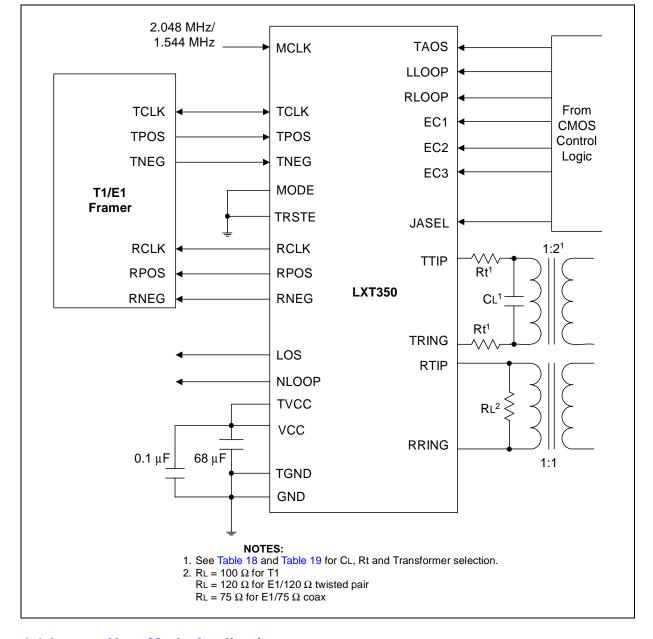

|         | 12      | Typical                   | T1/E1 LXT350 Hardware Mode Application                     | . 36 |

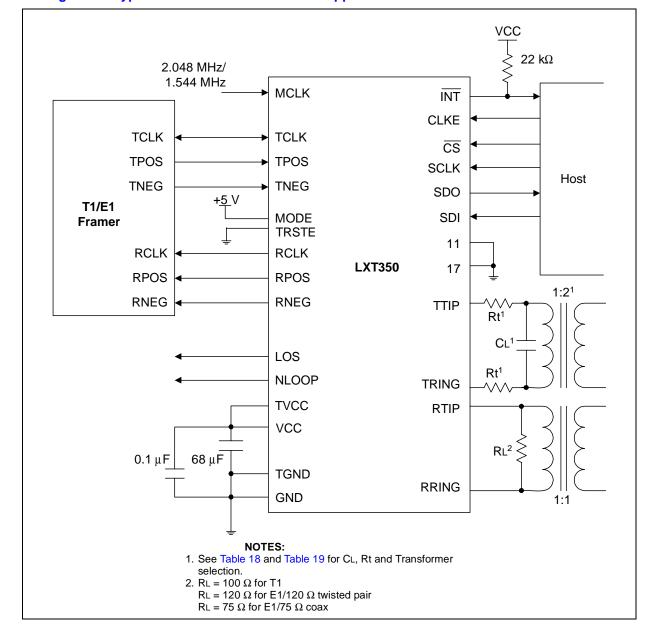

|         | 13      | Typical                   | T1/E1 LXT350 Host Mode Application                         | . 37 |

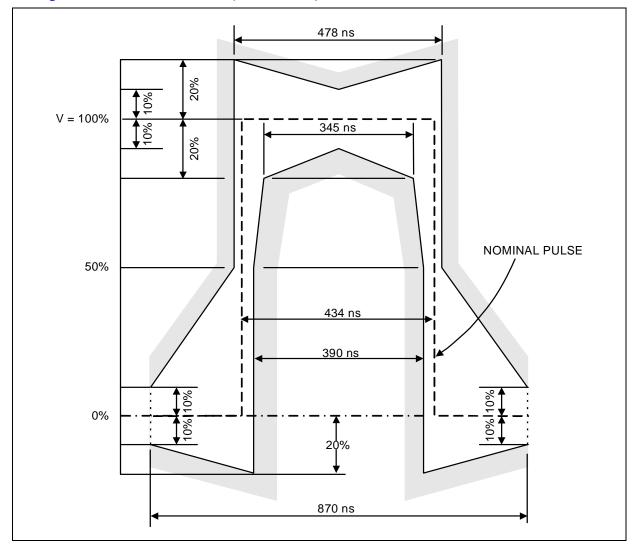

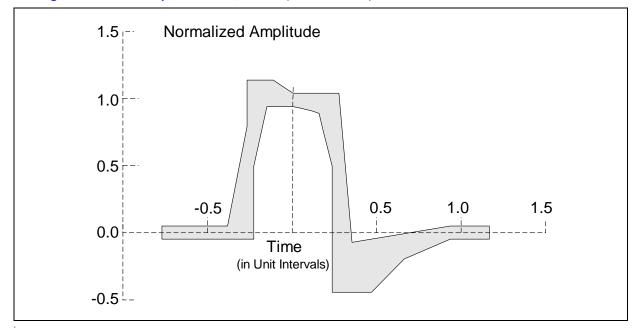

|         | 14      | 2.048 N                   | 1Hz E1 Pulse (See Table 26)                                | . 41 |

|         | 15      | 1.544 N                   | 1bps T1 Pulse, DSX-1 (See Table 27)                        | . 42 |

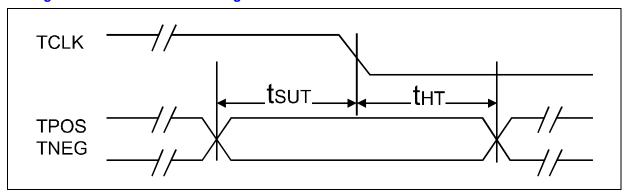

|         | 16      | Transm                    | it Clock Timing                                            | . 43 |

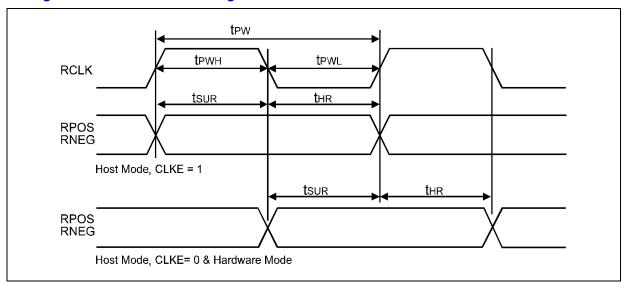

|         | 17      |                           | e Clock Timing                                             |      |

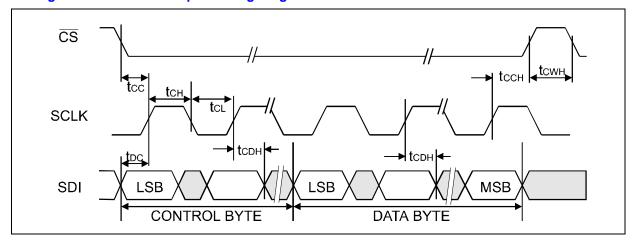

|         | 18      |                           | Pata Input Timing Diagram                                  |      |

|         | 19      |                           | Oata Output Timing Diagram                                 |      |

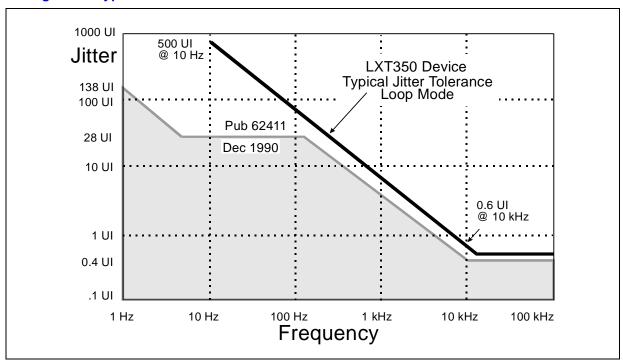

|         | 20      |                           | T1 Jitter Tolerance at 36 dB                               |      |

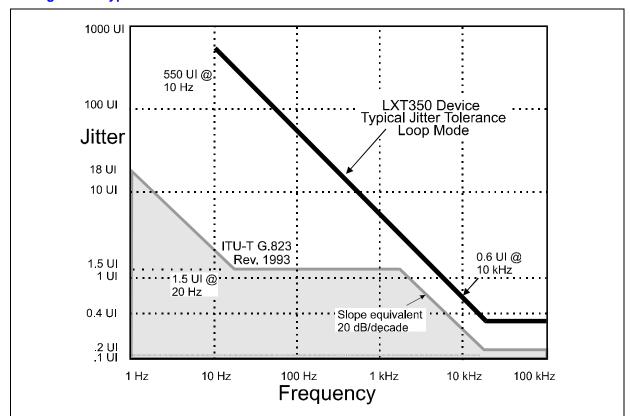

|         | 21      |                           | E1 Jitter Tolerance at 43 dB                               |      |

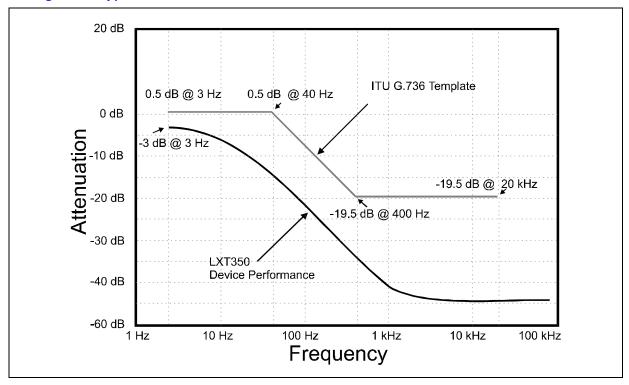

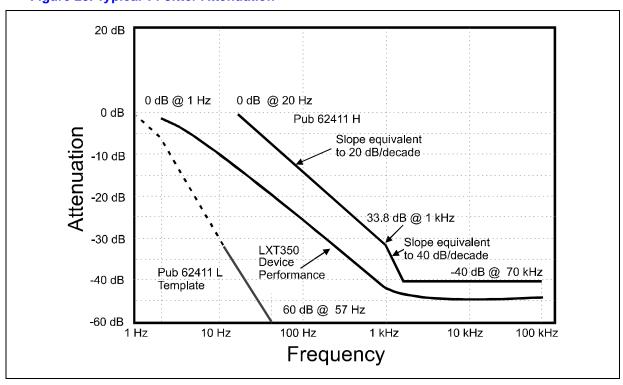

|         | 22      |                           | E1 Jitter Attenuation                                      |      |

|         | 23      |                           | T1 Jitter Attenuation                                      |      |

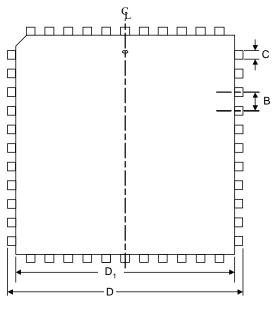

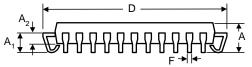

|         | 24      |                           | Leaded Chip Carrier Package Specifications                 |      |

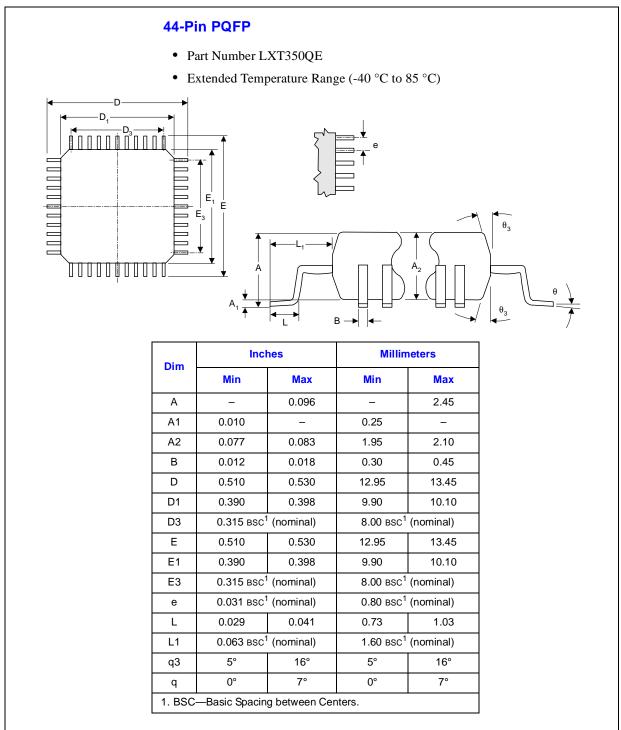

|         | 25      | Plastic                   | Quad Flat Package Specifications                           | . 50 |

|         | 26      | Sample                    | PLCC Package - Intel® LXT350 Transceiver                   | . 51 |

|         | 27      |                           | Pb-Free PLCC Package - Intel® LXT350 Transceiver           |      |

|         | 28      | Orderin                   | g Information Matrix – Sample                              | . 52 |

## **Tables**

| LXT350 Clock and Data Pins by Mode1 LXT350 Control Pins by Mode                                                                                                                                                                                                                                                                                                                                                 | 9 10 10 18 19 19 28 29 29 29 30 30 31 1x 31 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| CLKE Pin Settings1                                                                                                                                                                                                                                                                                                                                                                                              |                                             |

| Control and Operational Mode Selection Diagnostic Mode Availability                                                                                                                                                                                                                                                                                                                                             |                                             |

| Diagnostic Mode Availability                                                                                                                                                                                                                                                                                                                                                                                    |                                             |

| Register Addresses Register and Bit Summary Control Register #1 Read/Write, Address (A7-A0) = x010000x                                                                                                                                                                                                                                                                                                          |                                             |

| Register and Bit Summary Control Register #1 Read/Write, Address (A7-A0) = x010000x                                                                                                                                                                                                                                                                                                                             |                                             |

| Control Register #1 Read/Write, Address (A7-A0) = x010000x                                                                                                                                                                                                                                                                                                                                                      | 29<br>30<br>31<br>1x31                      |

| Equalizer Control Input Settings                                                                                                                                                                                                                                                                                                                                                                                | 29<br>30<br>31<br>1x31                      |

| Equalizer Control Input Settings                                                                                                                                                                                                                                                                                                                                                                                | 29<br>30<br>31<br>1x31                      |

| Control Register #3 Read/Write, Address (A7-A0) = x010010x                                                                                                                                                                                                                                                                                                                                                      | 30<br>31<br>1x31                            |

| Interrupt Clear Register Read/Write, Address (A7-A0) = x010011x  Transition Status Register Read Only, Address (A7-A0) = x010100x  Performance Status Register Read Only, Address (A7-A0) = x010100  Control Register #4 Read/Write, Address (A7-A0) = x010111x  E1 Transmit Return Loss Requirements                                                                                                           | 30<br>31<br>1x31                            |

| Transition Status Register Read Only, Address (A7-A0) = x010100x.  Performance Status Register Read Only, Address (A7-A0) = x010100x.  Control Register #4 Read/Write, Address (A7-A0) = x010111x                                                                                                                                                                                                               | 31<br>1x31<br>32                            |

| Performance Status Register Read Only, Address (A7-A0) = x010101 Control Register #4 Read/Write, Address (A7-A0) = x010111x                                                                                                                                                                                                                                                                                     | 1x31<br>32                                  |

| Control Register #4 Read/Write, Address (A7-A0) = x010111x                                                                                                                                                                                                                                                                                                                                                      | 32                                          |

| 17 E1 Transmit Return Loss Requirements 18 Transmit Return Loss (2.048 Mbps) 19 Transmit Return Loss (1.544 Mbps) 20 Transformer Specifications 21 Recommended Transformers 22 Absolute Maximum Ratings 23 Recommended Operating Conditions 24 DC Electrical Characteristics 25 Analog Characteristics 26 2.048 MHz E1 Pulse Mask Specifications 27 1.544 Mbps T1, DSX-1 Pulse Mask Corner Point Specifications |                                             |

| Transmit Return Loss (2.048 Mbps)                                                                                                                                                                                                                                                                                                                                                                               |                                             |

| Transmit Return Loss (1.544 Mbps)                                                                                                                                                                                                                                                                                                                                                                               | 33                                          |

| Transformer Specifications                                                                                                                                                                                                                                                                                                                                                                                      | 34                                          |

| 21 Recommended Transformers                                                                                                                                                                                                                                                                                                                                                                                     | 34                                          |

| Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                        | 34                                          |

| 23 Recommended Operating Conditions 24 DC Electrical Characteristics 25 Analog Characteristics 26 2.048 MHz E1 Pulse Mask Specifications 27 1.544 Mbps T1, DSX-1 Pulse Mask Corner Point Specifications                                                                                                                                                                                                         | 35                                          |

| <ul> <li>DC Electrical Characteristics</li></ul>                                                                                                                                                                                                                                                                                                                                                                | 38                                          |

| <ul> <li>Analog Characteristics</li></ul>                                                                                                                                                                                                                                                                                                                                                                       | 38                                          |

| <ul> <li>26 2.048 MHz E1 Pulse Mask Specifications</li> <li>1.544 Mbps T1, DSX-1 Pulse Mask Corner Point Specifications</li> </ul>                                                                                                                                                                                                                                                                              | 39                                          |

| 27 1.544 Mbps T1, DSX-1 Pulse Mask Corner Point Specifications                                                                                                                                                                                                                                                                                                                                                  | 39                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                 | 41                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                 |                                             |

| 28 T1 Operation Master and Transmit Clock Timing Characteristics                                                                                                                                                                                                                                                                                                                                                |                                             |

| (See Figure 16)                                                                                                                                                                                                                                                                                                                                                                                                 | 43                                          |

| 29 E1 Operation Master and Transmit Clock Timing Characteristics                                                                                                                                                                                                                                                                                                                                                |                                             |

| (See Figure 16)                                                                                                                                                                                                                                                                                                                                                                                                 |                                             |

| Receive Timing Characteristics for T1 Operation (See Figure 17)                                                                                                                                                                                                                                                                                                                                                 |                                             |

| Receive Timing Characteristics for E1 Operation (See Figure 17)                                                                                                                                                                                                                                                                                                                                                 |                                             |

| 32 Serial I/O Timing Characteristics (See Figure 18 and Figure 19)                                                                                                                                                                                                                                                                                                                                              |                                             |

| 33 Product Ordering Information                                                                                                                                                                                                                                                                                                                                                                                 | 45                                          |

# **Revision History**

| Revision | Date         | Description                                                                                                                                    |

|----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 002      | 31-Mar-2006  | <ul> <li>Added Section 6.1, "Top Label Markings" on page 51.</li> <li>Added Section 7.0, "Product Ordering Information" on page 52.</li> </ul> |

| 001      | January 2001 | First release.                                                                                                                                 |

Figure 1. LXT350 Block Diagram

## 1.0 Pin Assignments and Signal Descriptions

Figure 2. LXT350 Pin Assignments

## 1.1 Mode Dependent Signals

As shown in Figure 2, the LXT350 has various signal pins that change function (and name) according to the selected mode(s) of operation. These pins, associated signal names and operating modes are summarized in Table 1 and Table 2. LXT350 signals are described in Table 3.

Table 1. LXT350 Clock and Data Pins by Mode<sup>1</sup>

| Pin # |     | External D        | Oata Modes    | QRSS Modes   |               |  |  |  |  |  |

|-------|-----|-------------------|---------------|--------------|---------------|--|--|--|--|--|

| PLCC  | QFP | Bipolar Mode      | Unipolar Mode | Bipolar Mode | Unipolar Mode |  |  |  |  |  |

| 1     | 39  | MCLK              |               |              |               |  |  |  |  |  |

| 2     | 41  |                   | TCLK          |              |               |  |  |  |  |  |

| 3     | 42  | TPOS TDATA INSLER |               |              |               |  |  |  |  |  |

| 4     | 43  | TNEG              | INSBPV        | INSBPV       |               |  |  |  |  |  |

| 6     | 3   | RNEG              | BPV           | RNEG         | BPV           |  |  |  |  |  |

| 7     | 4   | RPOS              | RDATA         | RPOS         | RDATA         |  |  |  |  |  |

| 8     | 5   | RCLK              |               |              |               |  |  |  |  |  |

| 13    | 15  | TTIP              |               |              |               |  |  |  |  |  |

| 16    | 19  | TRING             |               |              |               |  |  |  |  |  |

| 19    | 24  | RTIP              |               |              |               |  |  |  |  |  |

| 20    | 25  | RRING             |               |              |               |  |  |  |  |  |

<sup>1.</sup> Data pins change based on whether external data or internal QRSS mode is active. Clock pins remain the same in both Hardware and Host modes.

Table 2. LXT350 Control Pins by Mode

| Pin  | #   | Hardware             | e Modes     | Host N               | lodes       | Pin  | #   | Hardware             | e Modes | Host N               | lodes |  |

|------|-----|----------------------|-------------|----------------------|-------------|------|-----|----------------------|---------|----------------------|-------|--|

| PLCC | QFP | Unipolar/<br>Bipolar | QRSS        | Unipolar/<br>Bipolar | QRSS        | PLCC | QFP | Unipolar/<br>Bipolar | QRSS    | Unipolar/<br>Bipolar | QRSS  |  |

| 5    | 2   | МО                   | MODE        |                      | MODE        |      | 32  | EC                   | 2       | SI                   | DI    |  |

| 9    | 7   | TRS                  | STE         | TRSTE                |             | 25   | 35  | EC                   | 3       | SD                   | 0     |  |

| 11   | 10  | JAS                  | EL          | Low                  |             | 26   | 36  | RLO                  | ОР      | C                    | S     |  |

| 12   | 13  | LOS                  | LOS/<br>QPD | LOS                  | LOS/<br>QPD | 27   | 37  | LLO                  | LLOOP   |                      | SCLK  |  |

| 23   | 31  | EC                   | 1           | ĪN                   | Т           | 28   | 38  | TAOS                 | QRSS    | CLI                  | ΚE    |  |

Table 3. LXT350 Signal Descriptions

| 2 41 TCLK  DI 2.048 MHz clock. The transceiver sample edge of TCLK (or MCLK, if TCLK is not properties)  BIPOLAR MODES:  Transmit – Positive and Negative. TPOS negative sides of a bipolar input pair. Data pair line is input at these pins. TPOS/TNE TCLK (or MCLK, if TCLK is not present).  UNIPOLAR MODES:  Transmit Data. TDATA carries unipolar data pair line and is sampled on the falling edg.  Transmit Insert Logic Error. In ORSS mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Paradidia.                                                                                                                                                                                                         |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1 39 MCLK DI clocks. For T1 applications, a 1.544 MHz of clock. MCLK must be jitter-free and have with a typical duty cycle of 50%. Upon Los from MCLK.  Transmit Clock. For T1 applications, a 1. 2 41 TCLK DI 2.048 MHz clock. The transceiver sample edge of TCLK (or MCLK, if TCLK is not properties and Negative. TPOS negative sides of a bipolar input pair. Data pair line is input at these pins. TPOS/TNE TCLK (or MCLK, if TCLK is not present).  UNIPOLAR MODES: Transmit Data. TDATA carries unipolar data pair line and is sampled on the falling edg. Transmit Insert Logic Error. In ORSS mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | tion                                                                                                                                                                                                               |  |  |

| 2 41 TCLK  DI 2.048 MHz clock. The transceiver sample edge of TCLK (or MCLK, if TCLK is not properties)  BIPOLAR MODES:  Transmit – Positive and Negative. TPOS negative sides of a bipolar input pair. Data pair line is input at these pins. TPOS/TNE TCLK (or MCLK, if TCLK is not present).  UNIPOLAR MODES:  Transmit Data. TDATA carries unipolar data pair line and is sampled on the falling edg.  Transmit Insert Logic Error. In ORSS mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | clock is required; for E1, a 2.048 MHz an accuracy better than ± 50 ppm                                                                                                                                            |  |  |

| Transmit – Positive and Negative. TPOS negative sides of a bipolar input pair. Data pair line is input at these pins. TPOS/TNE TCLK (or MCLK, if TCLK is not present).  UNIPOLAR MODES:  Transmit Data. TDATA carries unipolar da pair line and is sampled on the falling edg  Transmit Insert Logic Error. In ORSS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>Transmit Clock</b> . For T1 applications, a 1.544 MHz clock is required; for E1, a 2.048 MHz clock. The transceiver samples TPOS and TNEG on the <b>falling edge</b> of TCLK (or MCLK, if TCLK is not present). |  |  |

| negative sides of a bipolar input pair. Data pair line is input at these pins. TPOS/TNE TCLK (or MCLK, if TCLK is not present).  UNIPOLAR MODES:  Transmit Data. TDATA carries unipolar da pair line and is sampled on the falling edg  Transmit Insert Logic Error. In ORSS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                    |  |  |

| INSLER   Di pair line and is sampled on the falling edg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | a to be transmitted onto the twisted-                                                                                                                                                                              |  |  |

| Transmit Insert Logic Error, In QRSS mod                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                    |  |  |

| 4 43 TNEG / INSBPV DI INSLER inserts a logic error into the trans inserted error follows the data flow of the samples this pin on the falling edge of TCI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | mitted QRSS data pattern. The active loopback mode. The LXT350                                                                                                                                                     |  |  |

| Transmit Insert Bipolar Violation. INSBI<br>TCLK (or MCLK, if TCLK is not present) to<br>insertions in the transmit data stream. A<br>insert each BPV. In <i>QRSS mode</i> , the BPV<br>QRSS pattern.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | control Bipolar Violation (BPV) Low-to-High transition is required to                                                                                                                                              |  |  |

| 5 2 MODE DI Mode Select. Connect Low to select Hard Host mode. See Table 5 on page 19 for a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                    |  |  |

| BIPOLAR MODES:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                    |  |  |

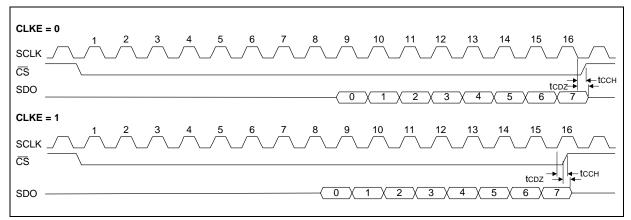

| Receive – Negative and Positive. RPOS negative sides of a bipolar output pair. Dat output on these pins. A signal on RNEG of pulse on RTIP/RRING. A signal on RPOS pulse on RTIP/RRING. RNEG/RPOS are Hardware mode, RPOS/RNEG are stable RCLK. In Host mode, the CLKE pin select /RNEG are stable and valid as described /RNEG are stable /RNEG are stab | ta recovered from the line interface is corresponds to receipt of a negative corresponds to receipt of a positive Non-Return-to-Zero (NRZ). In e and valid on the rising edge of ts the RCLK clock edge when RPOS  |  |  |

| UNIPOLAR MODES:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                    |  |  |

| Receive Bipolar Violation. BPV goes Hig violation from the line. This is an NRZ ou RCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                    |  |  |

| Receive Data. RDATA is the unipolar NR: line interface. In <i>Hardware mode</i> , RDATA of RCLK. In <i>Host mode</i> , the CLKE pin se RDATA is stable and valid as described in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | is stable and valid on the rising edge lects the RCLK clock edge when                                                                                                                                              |  |  |

| 8 5 RCLK DO Receive Recovered Clock. The clock recoutput on this pin. Under LOS conditions, RCLK signal (derived from the recovered appears at the RCLK pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | there is a smooth transition from the                                                                                                                                                                              |  |  |

DI = Digital Input; DO = Digital Output; DI/O = Digital Input/Output; AI = Analog Input; AO = Analog Output.

Midrange is a voltage level such that 2.3 V ≤ Midrange ≤ 2.7 V. Midrange may also be established by letting the pin float.

Table 3. LXT350 Signal Descriptions (Continued)

| Pi       | in#         | Symbol                | I/O <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|-------------|-----------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLCC     | QFP         | Symbol                | 1/0              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9        | 7           | TRSTE                 | DI               | Tristate.  HARDWARE MODES:  Connect TRSTE High to force all output pins to the high impedance state.  TRSTE, in conjunction with the MODE pin, selects the operating modes listed in Table 5 on page 19.  HOST MODES:  Connect TRSTE High to force all output pins to the high-impedance state.  Connect this pin Low for normal operation.                                                                                                                                                                                                                                                                                                                                                                           |

|          |             |                       |                  | HARDWARE MODES:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 11       | 10          | JASEL                 | DI               | Jitter Attenuation Select. Selects jitter attenuation location:  Setting JASEL High activates the jitter attenuator in the receive path.  Setting JASEL Low activates the jitter attenuator in the transmit path.  Setting JASEL to Midrange <sup>2</sup> disables jitter attenuation.  HOST MODES:  Connect Low in Host mode.                                                                                                                                                                                                                                                                                                                                                                                        |

| 12       | 13          | LOS / QPD             | DO               | Loss of Signal Indicator. LOS goes High upon receipt of 175 consecutive spaces and returns Low when the received signal reaches a mark density of 12.5% (determined by receipt of 16 marks within a sliding window of 128 bits with fewer than 100 consecutive zeros). Note that the transceiver outputs received marks on RPOS and RNEG even when LOS is High.  QRSS Pattern Detect. In QRSS mode, QPD stays High until the transceiver detects a QRSS pattern. When a QRSS pattern is detected, the pin goes Low. Any bit errors cause QPD to go High for half a clock cycle. This output can be used to trigger an external error counter. Note that a LOS condition will cause QPD to remain High. See Figure 11. |

| 13<br>16 | 15<br>19    | TTIP<br>TRING         | АО               | <b>Transmit Tip and Ring.</b> Differential driver output pair designed to drive a 50 - 200 $\Omega$ load. The transformer and line matching resistors should be selected to give the desired pulse height and return loss performance. See "Application Information" on page 33.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 14       | 16          | TGND                  | -                | Ground return for the transmit driver power supply TVCC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |