**Description**

# TwinDie™ 1.2V DDR4 SDRAM

# MT40A1G16 - 64 Meg x 16 x 16 Banks x 1 Ranks

The 16Gb (TwinDie™) DDR4 SDRAM uses Micron's 8Gb DDR4 SDRAM die; two x8s combined to make one x16. Similar signals as mono x16, there is one extra ZQ connection for faster ZQ Calibration and a BG1 control required for x8 addressing. Refer to Micron's 8Gb DDR4 SDRAM data sheet (x8 option) for the specifications not included in this document. Specifications for base part number MT40A1G8 correlate to TwinDie manufacturing part number MT40A1G16.

#### **Features**

- Uses two x8 8Gb Micron die to make one x16

- Single rank TwinDie

- $V_{DD} = V_{DDO} = 1.2V (1.14-1.26V)$

- 1.2V V<sub>DDO</sub>-terminated I/O

- JEDEC-standard ball-out

- Low-profile package

- T<sub>C</sub> of 0°C to 95°C

- 0°C to 85°C: 8192 refresh cycles in 64ms

- 85°C to 95°C: 8192 refresh cycles in 32ms

| Options                                              | Marking |

|------------------------------------------------------|---------|

| • Configuration                                      | _       |

| <ul> <li>64 Meg x 16 x 16 banks x 1 rank</li> </ul>  | 1G16    |

| • 96-ball FBGA package (Pb-free)                     |         |

| - 9.5mm x 14mm x 1.2mm Die Rev :A                    | HBA     |

| - 8.0mm x 14mm x 1.2mm Die Rev :B,                   | WBU     |

| D                                                    |         |

| - 7.5mm x 13.5mm x 1.2mm Die Rev :E                  | KNR     |

| • Timing – cycle time <sup>1</sup>                   |         |

| -0.625ns @ CL = 22 (DDR4-3200)                       | -062E   |

| -0.682ns @ CL = 21 (DDR4-2933)                       | -068    |

| - 0.750ns @ CL = 19 (DDR4-2666)                      | -075    |

| -0.750ns @ CL = 18 (DDR4-2666)                       | -075E   |

| -0.833ns @ CL = 17(DDR4-2400)                        | -083    |

| -0.833ns @ CL = 16 (DDR4-2400)                       | -083E   |

| -0.937ns @ CL = 15 (DDR4-2133)                       | -093E   |

| -1.071ns @ CL = 13 (DDR4-1866)                       | -107E   |

| <ul> <li>Self refresh</li> </ul>                     |         |

| <ul> <li>Standard</li> </ul>                         | None    |

| <ul> <li>Operating temperature</li> </ul>            |         |

| - Commercial (0°C $\leq$ T <sub>C</sub> $\leq$ 95°C) | None    |

| • Revision                                           | :A      |

|                                                      | :B, D   |

|                                                      | :Е      |

Note: 1. CL = CAS (READ) latency.

**Table 1: Key Timing Parameters**

| Speed Grade        | Data Rate (MT/s) | Target <sup>t</sup> RCD- <sup>t</sup> RP-CL | <sup>t</sup> RCD (ns) | <sup>t</sup> RP (ns) | CL (ns) |

|--------------------|------------------|---------------------------------------------|-----------------------|----------------------|---------|

| -062E <sup>1</sup> | 3200             | 22-22-22                                    | 13.75                 | 13.75                | 13.75   |

| -068 <sup>1</sup>  | 2933             | 21-21-21                                    | 14.32                 | 14.32                | 14.32   |

| -075 <sup>2</sup>  | 2666             | 19-19-19                                    | 14.25                 | 14.25                | 14.25   |

| -075E <sup>2</sup> | 2666             | 18-18-18                                    | 13.5                  | 13.5                 | 13.5    |

| -083 <sup>3</sup>  | 2400             | 17-17-17                                    | 14.16                 | 14.16                | 14.16   |

| -083E <sup>3</sup> | 2400             | 16-16-16                                    | 13.32                 | 13.32                | 13.32   |

| -093E <sup>4</sup> | 2133             | 15-15-15                                    | 14.06                 | 14.06                | 14.06   |

| -107E <sup>5</sup> | 1866             | 13-13-13                                    | 13.92                 | 13.92                | 13.92   |

Notes: 1. Backward compatible to 1600, CL = 11; 1866, CL = 13; 2133, CL = 15; 2400, CL = 17; and 2666, CL = 19.

- 2. Backward compatible to 1600, CL = 11; 1866, CL = 13; 2133, CL = 15; and 2400, CL = 17.

- 3. Backward compatible to 1600, CL = 11; 1866, CL = 13; and 2133, CL = 15.

- 4. Backward compatible to 1600, CL = 11 and 1866, CL = 13.

- 5. Backward compatible to 1600, CL = 11.

### 16Gb: x16 TwinDie Single Rank DDR4 SDRAM **Description**

#### **Table 2: Addressing**

| Parameter                  | 1024 Meg x 16                   |

|----------------------------|---------------------------------|

| Configuration              | 64 Meg x 16 x 16 banks x 1 rank |

| Bank group address         | BG[1:0]                         |

| Bank count per group       | 4                               |

| Bank address in bank group | BA[1:0]                         |

| Row addressing             | 64K (A[15:0])                   |

| Column addressing          | 1K (A[9:0])                     |

| Page size                  | 1KB                             |

Note: 1. Page size is per bank, calculated as follows:

Page size = 2<sup>COLBITS</sup> × ORG/8, where COLBIT = the number of column address bits and ORG = the number of DQ bits.

### 16Gb: x16 TwinDie Single Rank DDR4 SDRAM Important Notes and Warnings

# **Important Notes and Warnings**

Micron Technology, Inc. ("Micron") reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions. This document supersedes and replaces all information supplied prior to the publication hereof. You may not rely on any information set forth in this document if you obtain the product described herein from any unauthorized distributor or other source not authorized by Micron.

Automotive Applications. Products are not designed or intended for use in automotive applications unless specifically designated by Micron as automotive-grade by their respective data sheets. Distributor and customer/distributor shall assume the sole risk and liability for and shall indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage resulting directly or indirectly from any use of non-automotive-grade products in automotive applications. Customer/distributor shall ensure that the terms and conditions of sale between customer/distributor and any customer of distributor/customer (1) state that Micron products are not designed or intended for use in automotive applications unless specifically designated by Micron as automotive-grade by their respective data sheets and (2) require such customer of distributor/customer to indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage resulting from any use of non-automotive-grade products in automotive applications.

Critical Applications. Products are not authorized for use in applications in which failure of the Micron component could result, directly or indirectly in death, personal injury, or severe property or environmental damage ("Critical Applications"). Customer must protect against death, personal injury, and severe property and environmental damage by incorporating safety design measures into customer's applications to ensure that failure of the Micron component will not result in such harms. Should customer or distributor purchase, use, or sell any Micron component for any critical application, customer and distributor shall indemnify and hold harmless Micron and its subsidiaries, subcontractors, and affiliates and the directors, officers, and employees of each against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, or death arising in any way out of such critical application, whether or not Micron or its subsidiaries, subcontractors, or affiliates were negligent in the design, manufacture, or warning of the Micron product.

Customer Responsibility. Customers are responsible for the design, manufacture, and operation of their systems, applications, and products using Micron products. ALL SEMICONDUCTOR PRODUCTS HAVE INHERENT FAIL-URE RATES AND LIMITED USEFUL LIVES. IT IS THE CUSTOMER'S SOLE RESPONSIBILITY TO DETERMINE WHETHER THE MICRON PRODUCT IS SUITABLE AND FIT FOR THE CUSTOMER'S SYSTEM, APPLICATION, OR PRODUCT. Customers must ensure that adequate design, manufacturing, and operating safeguards are included in customer's applications and products to eliminate the risk that personal injury, death, or severe property or environmental damages will result from failure of any semiconductor component.

Limited Warranty. In no event shall Micron be liable for any indirect, incidental, punitive, special or consequential damages (including without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort, warranty, breach of contract or other legal theory, unless explicitly stated in a written agreement executed by Micron's duly authorized representative.

## **Ball Assignments**

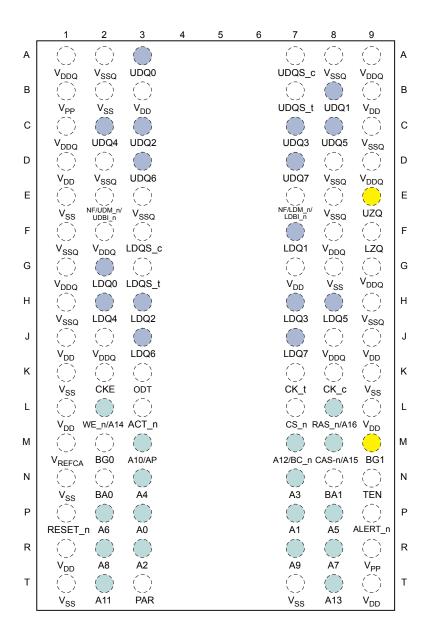

Figure 1: 96-Ball x16 SR DDP Ball Assignments

- Notes: 1. See Ball Descriptions in the monolithic data sheet.

- 2. A slash "/" defines a selectable function. For example: Ball E2 = NF/UDM\_n/UDBI\_n where either NF, UDM\_n, or UDBI\_n is defined via MRS.

# **Functional Block Diagrams**

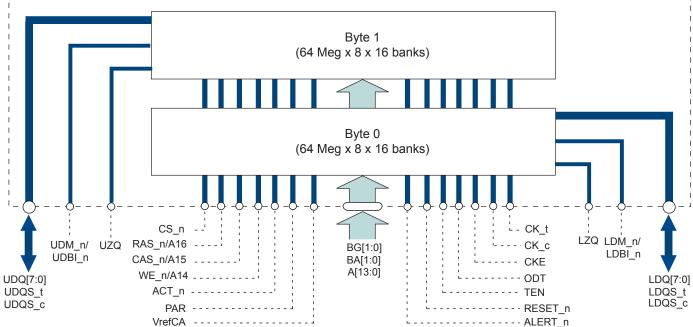

Figure 2: Functional Block Diagram (128 Meg x 16 x 16 Banks x 1 Rank)

(128 Meg x 16 x 16 banks) Byte 1 (64 Meg x 8 x 16 banks) Byte 0

# 16Gb: x16 TwinDie Single Rank DDR4 SDRAM Connectivity Test Mode

# **Connectivity Test Mode**

Connectivity test (CT) mode for the x16 TwinDie single rank (SR) device is the same as two mono x8 devices connected in parallel. The mapping is restated for clarity.

#### **Minimum Terms Definition for Logic Equations**

The test input and output pins are related by the following equations, where INV denotes a logical inversion operation and XOR a logical exclusive OR operation:

MT0 = XOR (A1, A6, PAR)

MT1 = XOR (A8, ALERT\_n, A9)

MT2 = XOR (A2, A5, A13)

MT3 = XOR (A0, A7, A11)

MT4 = XOR (CK\_c, ODT, CAS\_n/A15)

MT5 = XOR (CKE, RAS\_n/A16, A10/AP)

MT6 = XOR (ACT\_n, A4, BA1)

MT7L = XOR (BG1, LDM\_n/LDBI\_n, CK\_t)

MT7U = XOR (BG1, UDM\_n/UDBI\_n, CK\_t)

MT8 = XOR (WE\_n/A14, A12 / BC, BA0)

MT9 = XOR (BG0, A3, RESET\_n and TEN)

# Logic Equations for a x16 TwinDie, SR Device

| Byte 0         | Byte 1         |

|----------------|----------------|

| LDQ0 = MT0     | UDQ0 = MT0     |

| LDQ1 = MT1     | UDQ1 = MT1     |

| LDQ2 = MT2     | UDQ2 = MT2     |

| LDQ3 = MT3     | UDQ3 = MT3     |

| LDQ4 = MT4     | UDQ4 = MT4     |

| LDQ5 = MT5     | UDQ5 = MT5     |

| LDQ6 = MT6     | UDQ6 = MT6     |

| LDQ7 = MT7L    | UDQ7 = MT7U    |

| $LDQS_t = MT8$ | $UDQS_t = MT8$ |

| $LDQS_c = MT9$ | $UDQS_c = MT9$ |

|                |                |

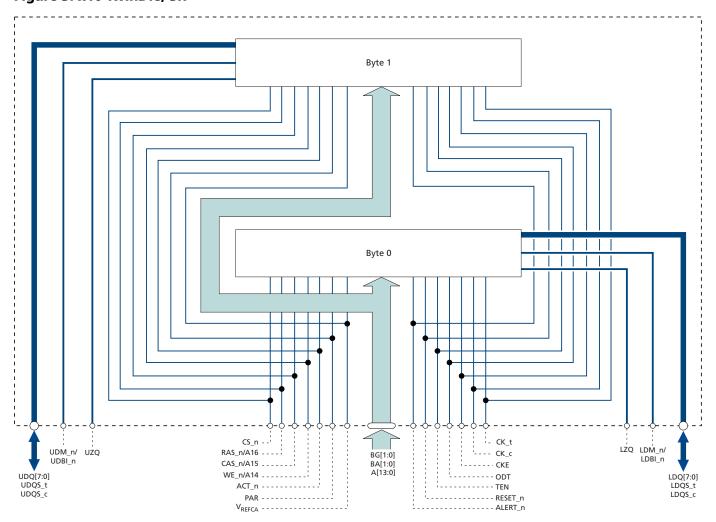

#### x16 TwinDie, SR Internal Connections

The figure below shows the internal connections of the x16 TwinDie, SR. The diagram shows why byte 0 and byte 1 outputs have the same logic equations except LDQ7 and UDQ7; they are different because the DM n/DBI n pins are not common for each byte.

Figure 3: x16 TwinDie, SR

## **Electrical Specifications – Leakages**

**Table 3: Input and Output Leakages**

| Symbol            | Parameter                                                                                                                                         | Min  | Max | Units | Notes |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|-------|

| I <sub>I</sub>    | Input leakage current<br>Any input $0V \le V_{IN} \le V_{DD}$ ,<br>$V_{REF}$ pin $0V \le V_{IN} \le 1.1V$<br>(All other pins not under test = 0V) | -4   | 4   | μА    | 1     |

| I <sub>VREF</sub> | $V_{REF}$ supply leakage current<br>$V_{REFDQ} = V_{DD}/2$ or $V_{REFCA} = V_{DD}/2$<br>(All other pins not under test = 0V)                      | -4   | 4   | μΑ    | 2     |

| I <sub>ZQ</sub>   | Input leakage on ZQ pin                                                                                                                           | -3   | 3   | μA    |       |

| I <sub>TEN</sub>  | Input leakage on TEN pin                                                                                                                          | -12  | 20  | μΑ    |       |

| I <sub>OZPD</sub> | Output leakage: V <sub>OUT</sub> = V <sub>DDQ</sub>                                                                                               | _    | 10  | μΑ    | 3     |

| I <sub>OZPU</sub> | Output leakage: V <sub>OUT</sub> = V <sub>SSQ</sub>                                                                                               | -100 | _   | μΑ    | 3, 4  |

- Notes: 1. Any input 0V < Vin < 1.1V

- 2.  $V_{REFCA} = V_{DD}/2$ ,  $V_{DD}$  at valid level.

- 3. DQs are disabled.

- 4. ODT is disabled with the ODT input HIGH.

### **Temperature and Thermal Impedance**

It is imperative that the DDR4 SDRAM device's temperature specifications, shown in the following table, be maintained in order to ensure the junction temperature is in the proper operating range to meet data sheet specifications. An important step in maintaining the proper junction temperature is using the device's thermal impedances correctly. The thermal impedances listed in Table 5 (page 9) apply to the current die revision and packages.

Incorrectly using thermal impedances can produce significant errors. Read Micron technical note TN-00-08, "Thermal Applications," prior to using the values listed in the thermal impedance table. For designs that are expected to last several years and require the flexibility to use several DRAM die shrinks, consider using final target theta values (rather than existing values) to account for increased thermal impedances from the die size reduction.

The DDR4 SDRAM device's safe junction temperature range can be maintained when the T<sub>C</sub> specification is not exceeded. In applications where the device's ambient temperature is too high, use of forced air and/or heat sinks may be required to satisfy the case temperature specifications.

**Table 4: Thermal Characteristics**

Notes 1-3 apply to entire table

| Parameter             | Symbol         | Value   | Units | Notes |

|-----------------------|----------------|---------|-------|-------|

| Operating temperature | T <sub>C</sub> | 0 to 85 | °C    |       |

|                       |                | 0 to 95 | °C    | 4     |

Notes:

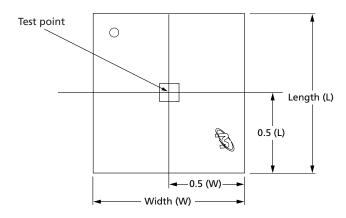

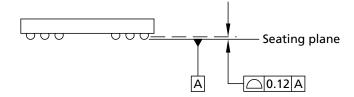

- 1. MAX operating case temperature T<sub>C</sub> is measured in the center of the package, as shown below.

- 2. A thermal solution must be designed to ensure that the device does not exceed the maximum T<sub>C</sub> during operation.

- 3. Device functionality is not guaranteed if the device exceeds maximum  $T_{\text{C}}$  during operation.

- If T<sub>C</sub> exceeds 85°C, the DRAM must be refreshed externally at 2x refresh, which is a 3.9μs interval refresh rate. The use of self refresh temperature (SRT) or automatic self refresh (ASR), if available, must be enabled.

**Figure 4: Temperature Test Point Location**

**Table 5: Thermal Impedance**

| Die Rev. | Substrate conductivity | ⊖ JA (°C/W)<br>Airflow =<br>0m/s | ⊖ JA (°C/W)<br>Airflow =<br>1m/s | ⊖ JA (°C/W)<br>Airflow =<br>2m/s | ⊖ JB (°C/W) | ⊖ JC (°C/W) | Notes |

|----------|------------------------|----------------------------------|----------------------------------|----------------------------------|-------------|-------------|-------|

| A        | Low                    | TBD                              | TBD                              | TBD                              | N/A         | TBD         | 1     |

| A        | High                   | TBD                              | TBD                              | TBD                              | TBD         | N/A         | '     |

| B D      | Low                    | 43.9                             | 33.0                             | 29.5                             | N/A         | 3.3         | 1     |

| B, D     | High                   | 27.1                             | 21.7                             | 20.1                             | 10.5        | N/A         | '     |

| E        | Low                    | TBD                              | TBD                              | TBD                              | N/A         | TBD         | 1     |

|          | High                   | TBD                              | TBD                              | TBD                              | TBD         | N/A         |       |

Note: 1. Thermal resistance data is based on a number of samples from multiple lots and should be viewed as a typical number.

# **DRAM Package Electrical Specifications**

#### **Table 6: DRAM Package Electrical Specifications for x16 Devices**

Notes 1-4 apply to the entire table

|                               | priy to the entire |                         | <b>DDR4-16</b> | 00, -1866 | DDR4-21 | 33, -2400 | DDR4-26 | DDR4-2666, -2933 |      | 66, -2933 |  |  |

|-------------------------------|--------------------|-------------------------|----------------|-----------|---------|-----------|---------|------------------|------|-----------|--|--|

| Parameter                     |                    | Symbol                  | Min            | Max       | Min     | Max       | Min     | Max              | Unit | Notes     |  |  |

| Input/                        | Zpkg               | Z <sub>IO</sub>         | 30             | 50        | 30      | 50        | 30      | 50               | ohm  | 5, 6      |  |  |

| output                        | Package delay      | Td <sub>IO</sub>        | 65             | 120       | 65      | 120       | 65      | 120              | ps   | 6,7       |  |  |

|                               | Lpkg               | L <sub>IO</sub>         | _              | 5.0       | _       | 5.0       | _       | 5.0              | nH   |           |  |  |

|                               | Cpkg               | C <sub>IO</sub>         | _              | 3.0       | _       | 3.0       | _       | 3.0              | pF   |           |  |  |

| DQSL_t/                       | Zpkg               | Z <sub>IO DQS</sub>     | 30             | 50        | 30      | 50        | 30      | 50               | ohm  | 5         |  |  |

| DQSL_c/                       | Package delay      | Td <sub>IO DQS</sub>    | 65             | 120       | 65      | 120       | 65      | 120              | ps   | 7         |  |  |

| DQSU_t/<br>DQSU_c             | Lpkg               | L <sub>IO DQS</sub>     | _              | 5.0       | -       | 5.0       | _       | 5.0              | nH   |           |  |  |

| DQ30_c                        | Cpkg               | C <sub>IO DQS</sub>     | _              | 3.0       | -       | 3.0       | _       | 3.0              | pF   |           |  |  |

| DQSL_t/                       | Delta Zpkg         | DZ <sub>IO DQS</sub>    | _              | 20        | -       | 20        | _       | 20               | ohm  | 5, 8      |  |  |

| DQSL_c,<br>DQSU_t/<br>DQSU_c, | Delta delay        | DTd <sub>IO DQS</sub>   | _              | 45        | _       | 45        | _       | 45               | ps   | 7, 8      |  |  |

| Input CTRL                    | Zpkg               | Z <sub>I CTRL</sub>     | 35             | 65        | 35      | 65        | 35      | 65               | ohm  | 5, 9      |  |  |

| pins                          | Package delay      | Td <sub>I CTRL</sub>    | 75             | 120       | 75      | 120       | 75      | 120              | ps   | 7, 9      |  |  |

|                               | Lpkg               | L <sub>I CTRL</sub>     | _              | 6.5       | -       | 6.5       | _       | 6.5              | nH   |           |  |  |

|                               | Cpkg               | C <sub>I CTRL</sub>     | _              | 2.5       | -       | 2.5       | _       | 2.5              | pF   |           |  |  |

| Input CMD                     | Zpkg               | Z <sub>I ADD CMD</sub>  | 35             | 65        | 35      | 65        | 35      | 65               | ohm  | 5, 10     |  |  |

| ADD pins                      | Package delay      | Td <sub>I ADD CMD</sub> | 70             | 125       | 70      | 125       | 70      | 125              | ps   | 7, 10     |  |  |

|                               | Lpkg               | L <sub>I ADD CMD</sub>  | _              | 6.5       | -       | 6.5       | _       | 6.5              | nH   |           |  |  |

|                               | Cpkg               | C <sub>I ADD CMD</sub>  | _              | 3.0       | -       | 3.0       | _       | 3.0              | pF   |           |  |  |

| CK_t, CK_c                    | Zpkg               | Z <sub>CK</sub>         | 30             | 55        | 30      | 55        | 30      | 55               | ohm  | 5         |  |  |

|                               | Package delay      | Td <sub>CK</sub>        | 80             | 135       | 80      | 135       | 80      | 135              | ps   | 7         |  |  |

|                               | Delta Zpkg         | DZ <sub>DCK</sub>       | _              | 0.5       | _       | 0.5       | _       | 0.5              | ohm  | 5, 11     |  |  |

|                               | Delta delay        | DTd <sub>DCK</sub>      | _              | 1.2       | _       | 1.2       | _       | 1.2              | ps   | 7, 11     |  |  |

| Input CLK                     | Lpkg               | L <sub>I CLK</sub>      | _              | 6.0       | _       | 6.0       | _       | 6.0              | nH   |           |  |  |

|                               | Cpkg               | C <sub>I CLK</sub>      | _              | 3.0       | _       | 3.0       | _       | 3.0              | pF   |           |  |  |

| ZQ Zpkg                       | •                  | Z <sub>O ZQ</sub>       | _              | 40        | _       | 40        | _       | 40               | ohm  | 5         |  |  |

| ZQ delay                      |                    | Td <sub>O ZQ</sub>      | 55             | 120       | 55      | 120       | 55      | 120              | ps   | 7         |  |  |

| ALERT Zpkg                    |                    | Z <sub>O ALERT</sub>    | 30             | 55        | 30      | 55        | 30      | 55               | ohm  | 5         |  |  |

| ALERT delay                   | ,                  | Td <sub>O ALERT</sub>   | 65             | 110       | 65      | 110       | 65      | 110              | ps   | 7         |  |  |

- Notes: 1. The package parasitic (L and C) are not subject to production testing. If the package parasitic (L and C) are measured, the capacitance is measured with  $V_{DD}$ ,  $V_{DDQ}$ ,  $V_{SS}$ , and  $V_{SSQ}$ shorted with all other signal pins floating. The inductance is measured with V<sub>DD</sub>, V<sub>DDQ</sub>,  $V_{SS}$ , and  $V_{SSQ}$  shorted and all other signal pins shorted at the die, not pin, side.

- 2. Package implementations should satisfy targets if the Zpkg and package delay fall within the ranges shown, and the maximum Lpkg and Cpkg do not exceed the maximum

#### 16Gb: x16 TwinDie Single Rank DDR4 SDRAM DRAM Package Electrical Specifications

values shown. The package design targets are provided for reference, system signal simulations should not use these values but use the Micron package model.

- 3. It is assumed that Lpkg can be approximated as Lpkg =  $Z_O \times Td$ .

- 4. It is assumed that Cpkg can be approximated as Cpkg =  $Td/Z_O$ .

- 5. Package-only impedance (Zpkg) is calculated based on the Lpkg and Cpkg total for a given pin where: Zpkg (total per pin) = SQRT (Lpkg/Cpkg).

- 6. Z<sub>IO</sub> and Td<sub>IO</sub> apply to DQ, DM, DQS\_c, DQS\_t, TDQS\_t, and TDQS\_c.

- 7. Package-only delay (Tpkg) is calculated based on Lpkg and Cpkg total for a given pin where: Tdpkg (total per pin) = SQRT (Lpkg × Cpkg).

- 8. Absolute value of ZIO (DQS\_t), ZIO (DQS\_c) for impedance (Z) or absolute value of TdIO (DQS\_t), TdIO (DQS\_c) for delay (Td).

- 9. Z<sub>I CTRL</sub> and Td<sub>I CTRL</sub> apply to ODT, CS\_n, and CKE.

- 10.  $Z_{IADD\ CMD}$  and  $Td_{IADD\ CMD}$  apply to A[17:0], BA[1:0], BG[1:0], RAS\_n CAS\_n, and WE\_n.

- 11. Absolute value of ZCK\_t, ZCK\_c for impedance (Z) or absolute value of TdCK\_t, TdCK\_c for delay (Td).

**Table 7: Pad Input/Output Capacitance**

|                                                                            |                         |       | -1600,<br>-2133 |       | -2400,<br>666 | DDR4  | -2933 |      |                 |

|----------------------------------------------------------------------------|-------------------------|-------|-----------------|-------|---------------|-------|-------|------|-----------------|

| Parameter                                                                  | Symbol                  | Min   | Max             | Min   | Max           | Min   | Max   | Unit | Notes           |

| Input/output capacitance: DQ,<br>DM, DQS_t, DQS_c, TDQS_t,<br>TDQS_c       | C <sub>IO</sub>         | 1.8   | 2.8             | 1.8   | 2.8           | 1.8   | 2.8   | pF   | 1, 2, 3         |

| Input capacitance: CK_t and CK_c                                           | C <sub>CK</sub>         | 2.1   | 2.9             | 2.1   | 2.9           | 2.1   | 2.9   | pF   | 1, 2, 3, 4      |

| Input capacitance delta: CK_t and CK_c                                     | C <sub>DCK</sub>        | 0     | 0.05            | 0     | 0.05          | 0     | 0.05  | pF   | 1, 2, 3, 5      |

| Input/output capacitance delta: DQS_t and DQS_c                            | C <sub>DDQS</sub>       | 0     | 0.05            | 0     | 0.05          | 0     | 0.05  | pF   | 1, 3            |

| Input capacitance: CTRL, ADD, CMD input-only pins                          | C <sub>I</sub>          | 1.6   | 2.6             | 1.6   | 2.6           | 1.6   | 2.6   | pF   | 1, 3, 6         |

| Input capacitance delta: All CTRL input-only pins                          | C <sub>DI_CTRL</sub>    | -0 .9 | 0.9             | -0 .9 | 0.9           | -0 .9 | 0.9   | pF   | 1, 3, 7         |

| Input capacitance delta: All ADD/CMD input-only pins                       | C <sub>DI_ADD_CMD</sub> | -0 .9 | 0.9             | -0 .9 | 0.9           | -0 .9 | 0.9   | pF   | 1, 3, 8, 9      |

| Input/output capacitance delta:<br>DQ, DM, DQS_t, DQS_c, TDQS_t,<br>TDQS_c | C <sub>DIO</sub>        | -0.16 | 0.16            | -0.16 | 0.16          | -0.16 | 0.16  | pF   | 1, 2, 10,<br>11 |

| Input/output capacitance:<br>ALERT pin                                     | C <sub>ALERT</sub>      | 1.1   | 2.3             | 1.1   | 2.3           | 1.1   | 2.3   | pF   | 1, 3            |

| Input/output capacitance: ZQ pin                                           | C <sub>ZQ</sub>         | -     | 3.7             | _     | 3.7           | _     | 3.7   | pF   | 1, 3, 12        |

| Input/output capacitance: TEN pin                                          | C <sub>TEN</sub>        | 0.2   | 2.3             | 0.2   | 2.3           | 0.2   | 2.3   | pF   | 1, 3, 13        |

Notes: 1. Although the DM, TDQS\_t, and TDQS\_c pins have different functions, the loading matches DQ and DQS.

#### 16Gb: x16 TwinDie Single Rank DDR4 SDRAM DRAM Package Electrical Specifications

- 2. This parameter is not subject to a production test; it is verified by design and characterization and are provided for reference; system signal simulations should not use these values but use the Micron package model. The capacitance, if and when, is measured according to the JEP147 specification, "Procedure for Measuring Input Capacitance Using a Vector Network Analyzer (VNA)," with  $V_{DD}$ ,  $V_{DDQ}$ ,  $V_{SS}$ , and  $V_{SSQ}$  applied and all other pins floating (except the pin under test, CKE, RESET\_n and ODT, as necessary).  $V_{DD} = V_{DDQ} = 1.5 \text{V}$ ,  $V_{BIAS} = V_{DD}/2$  and on-die termination off.

- 3. This parameter applies to SR x16 TwinDie, obtained by de-embedding the package L and C parasitics.

- 4.  $C_{DIO} = C_{IO}(DQ, DM) 0.5 \times (C_{IO}(DQS_t) + C_{IO}(DQS_c))$ .

- 5. Absolute value of C<sub>IO</sub> (DQS\_t), C<sub>IO</sub> (DQS\_c)

- 6. Absolute value of CCK\_t, CCK\_c

- 7. C<sub>I</sub> applies to ODT, CS\_n, CKE, A[15:0], BA[1:0], RAS\_n, CAS\_n, and WE\_n.

- 8. C<sub>DI CTRL</sub> applies to ODT, CS\_n, and CKE.

- 9.  $C_{DI CTRL} = C_I(CTRL) 0.5 \times (C_I(CLK_t) + C_I(CLK_c)).$

- 10.  $C_{DI\_ADD\_CMD}$  applies to A[15:0], BA1:0], RAS\_n, CAS\_n and WE\_n.

- 11.  $C_{DI ADD CMD} = C_I(ADD\_CMD) 0.5 \times (C_I(CLK\_t) + C_I(CLK\_c)).$

- 12. Maximum external load capacitance on ZQ pin: 5pF.

- 13. Only applicable if TEN pin does not have an internal pull-up.

12

# **Current Specifications – Limits**

Table 8: x16  $I_{DD}$ ,  $I_{PP}$ , and  $I_{DDQ}$  Current Limits – Rev. A

| Symbol                                                                 | DDR4-2133 <sup>1</sup> | DDR4-2400 | DDR4-2666 | DDR4-2933 | Unit | Notes                       |

|------------------------------------------------------------------------|------------------------|-----------|-----------|-----------|------|-----------------------------|

| I <sub>DD0</sub> : One bank ACTIVATE-to-PRECHARGE current              | 110                    | 120       | 130       | TBD       | mA   | 2, 3, 4                     |

| $I_{PPO}$ : One bank ACTIVATE-to-PRECHARGE $I_{PP}$ current            | 6                      | 6         | 6         | TBD       | mA   |                             |

| I <sub>DD1</sub> : One bank ACTIVATE-to-READ-to-PRE-<br>CHARGE current | 140                    | 150       | 160       | TBD       | mA   | 3, 4, 5                     |

| I <sub>DD2N</sub> : Precharge standby current                          | 90                     | 100       | 110       | TBD       | mA   | 4, 6, 7, 8,<br>9, 10, 11    |

| I <sub>DD2NT</sub> : Precharge standby ODT current                     | 110                    | 120       | 130       | TBD       | mA   | 4, 11                       |

| I <sub>DD2P</sub> : Precharge power-down current                       | 50                     | 60        | 70        | TBD       | mA   | 4, 11                       |

| I <sub>DD2Q</sub> : Precharge quiet standby current                    | 90                     | 90        | 100       | TBD       | mA   | 4, 11                       |

| I <sub>DD3N</sub> : Active standby current                             | 110                    | 110       | 120       | TBD       | mA   | 4, 11                       |

| I <sub>PP3N</sub> : Active standby I <sub>PP</sub> current             | 6                      | 6         | 6         | TBD       | mA   |                             |

| I <sub>DD3P</sub> : Active power-down current                          | 70                     | 80        | 80        | TBD       | mA   | 4, 11                       |

| I <sub>DD4R</sub> : Burst read current                                 | 300                    | 300       | 350       | TBD       | mA   | 4, 14, 13,<br>11            |

| I <sub>DD4W</sub> : Burst write current                                | 300                    | 320       | 350       | TBD       | mA   | 4, 11, 15,<br>16, 17,<br>18 |

| I <sub>DD5R</sub> : Burst refresh current (1X REF)                     | 128                    | 128       | 136       | TBD       | mA   | 4, 19, 20                   |

| I <sub>PP5R</sub> : Burst refresh I <sub>PP</sub> current (1X REF)     | 10                     | 10        | 10        | TBD       | mA   |                             |

| I <sub>DD6N</sub> : Self refresh current; 0–85°C                       | 60                     | 60        | 60        | TBD       | mA   | 11, 21                      |

| I <sub>DD6E</sub> : Self refresh current; 0–95°C                       | 70                     | 70        | 70        | TBD       | mA   | 11, 22                      |

| I <sub>DD6R</sub> : Self refresh current; 0–45°C                       | 50                     | 50        | 50        | TBD       | mA   | 11, 23,<br>24               |

| I <sub>DD6A</sub> : Auto self refresh current (25°C)                   | 40                     | 40        | 40        | TBD       | mA   | 11, 24                      |

| I <sub>DD6A</sub> : Auto self refresh current (45°C)                   | 50                     | 50        | 50        | TBD       | mA   | 11, 24                      |

| I <sub>DD6A</sub> : Auto self refresh current (75°C)                   | 70                     | 70        | 70        | TBD       | mA   | 11, 24                      |

| I <sub>PP6X</sub> : Auto self refresh current I <sub>PP</sub> current  | 10                     | 10        | 10        | TBD       | mA   | 11, 24                      |

| I <sub>DD7</sub> : Bank interleave read current                        | 400                    | 410       | 430       | TBD       | mA   | 4                           |

| I <sub>PP7</sub> : Bank interleave read I <sub>PP</sub> current        | 30                     | 30        | 30        | TBD       | mA   |                             |

| I <sub>DD8</sub> : Maximum power-down current                          | 40                     | 40        | 40        | TBD       | mA   | 11                          |

- Notes: 1. DDR4-1600 and DDR4-1866 use the same  $I_{DD}$  limits as DDR4-2133.

- 2. When additive latency is enabled for  $I_{DD0}$ , current changes by approximately 0%.

- 3.  $I_{PP0}$  test and limit is applicable for  $I_{DD0}$  and  $I_{DD1}$  conditions.

- 4. The  $I_{DD}$  values must be derated (increased) when operated outside of the range  $0^{\circ}C \leq T_{C}$ ≤ 85°C:

When  $T_C < 0^{\circ}C$ :  $I_{DD2P}$  and  $I_{DD3P}$  must be derated by 6%;  $I_{DD4R}$  and  $I_{DD4W}$  must be derated by 4%; and I<sub>DD7</sub> must be derated by 11%.

#### 16Gb: x16 TwinDie Single Rank DDR4 SDRAM Current Specifications – Limits

When  $T_C > 85^{\circ}C$ :  $I_{DD0}$ ,  $I_{DD1}$ ,  $I_{DD2N}$ ,  $I_{DD2NT}$ ,  $I_{DD2Q}$ ,  $I_{DD3N}$ ,  $I_{DD3P}$ ,  $I_{DD4R}$ ,  $I_{DD4W}$ , and  $I_{DD5R}$  must be derated by 40%.

- 5. When additive latency is enabled for I<sub>DD1</sub>, current changes by approximately +4%.

- 6. When additive latency is enabled for I<sub>DD2N</sub>, current changes by approximately +0%.

- 7. When DLL is disabled for I<sub>DD2N</sub>, current changes by approximately –23%.

- 8. When CAL is enabled for  $I_{DD2N}$ , current changes by approximately –25%.

- 9. When gear-down is enabled for IDD2N, current changes by approximately 0%.

- 10. When CA parity is enabled for I<sub>DD2N</sub>, current changes by approximately +7%.

- 11. I<sub>PP3N</sub> test and limit is applicable for all I<sub>DD2x</sub>, I<sub>DD3x</sub>, I<sub>DD4x</sub>, I<sub>DD6x</sub>, and I<sub>DD8</sub> conditions; that is, testing I<sub>PP3N</sub> should satisfy the I<sub>PP</sub>s for the noted I<sub>DD</sub> tests.

- 12. When additive latency is enabled for  $I_{DD3N}$ , current changes by approximately +0.6%.

- 13. When additive latency is enabled for I<sub>DD4R</sub>, current changes by approximately +5%.

- 14. When read DBI is enabled for I<sub>DD4R</sub>, current changes by approximately 0%.

- 15. When additive latency is enabled for  $I_{DD4W}$ , current changes by approximately +4%.

- 16. When write DBI is enabled for IDD4W, current changes by approximately 0%.

- 17. When write CRC is enabled for IDD4W, current changes by approximately -3%.

- 18. When CA parity is enabled for  $I_{DD4W}$ , current changes by approximately +12%.

- 19. When 2X REF is enabled for I<sub>DD5R</sub>, current changes by approximately –14%.

- 20. When 4X REF is enabled for  $I_{DD5R}$ , current changes by approximately -33%.

- 21. Applicable for MR2 settings A7 = 0 and A6 = 0; manual mode with normal temperature range of operation  $(0-85^{\circ}C)$ .

- 22. Applicable for MR2 settings A7 = 1 and A7 = 0; manual mode with extended temperature range of operation  $(0-95^{\circ}C)$ .

- 23. Applicable for MR2 settings A7 = 0 and A7 = 1; manual mode with reduced temperature range of operation  $(0-45^{\circ}C)$ .

- 24. I<sub>DD6R</sub> and I<sub>DD6A</sub> values are typical.

Table 9: x16 I<sub>DD</sub>, I<sub>PP</sub>, and I<sub>DDO</sub> Current Limits – Rev. B

| Symbol                                                                         | DDR4-2133 <sup>1</sup> | DDR4-2400 | DDR4-2666 | DDR4-2933 | DDR4-3200 | Unit | Notes                       |

|--------------------------------------------------------------------------------|------------------------|-----------|-----------|-----------|-----------|------|-----------------------------|

| <b>I<sub>DD0</sub></b> : One bank ACTIVATE-to-PRE-CHARGE current               | 90                     | 96        | 102       | 108       | 114       | mA   | 2, 3, 4                     |

| I <sub>PP0</sub> : One bank ACTIVATE-to-PRE-<br>CHARGE I <sub>PP</sub> current | 6                      | 6         | 6         | 6         | 6         | mA   |                             |

| I <sub>DD1</sub> : One bank ACTIVATE-to-<br>READ-to-PRECHARGE current          | 114                    | 120       | 126       | 132       | 138       | mA   | 3, 4, 5                     |

| I <sub>DD2N</sub> : Precharge standby current                                  | 66                     | 68        | 70        | 72        | 74        | mA   | 4, 6, 7,<br>8, 9, 10,<br>11 |

| I <sub>DD2NT</sub> : Precharge standby ODT current                             | 90                     | 100       | 100       | 110       | 120       | mA   | 4, 11                       |

| I <sub>DD2P</sub> : Precharge power-down current                               | 50                     | 50        | 50        | 50        | 50        | mA   | 4, 11                       |

| I <sub>DD2Q</sub> : Precharge quiet standby current                            | 60                     | 60        | 60        | 60        | 60        | mA   | 4, 11                       |

| I <sub>DD3N</sub> : Active standby current                                     | 80                     | 86        | 92        | 98        | 104       | mA   | 4, 11                       |

| I <sub>PP3N</sub> : Active standby I <sub>PP</sub> current                     | 6                      | 6         | 6         | 6         | 6         | mA   |                             |

| I <sub>DD3P</sub> : Active power-down current                                  | 70                     | 74        | 78        | 82        | 86        | mA   | 4, 11                       |

#### 16Gb: x16 TwinDie Single Rank DDR4 SDRAM **Current Specifications – Limits**

Table 9: x16 I<sub>DD</sub>, I<sub>PP</sub>, and I<sub>DDQ</sub> Current Limits – Rev. B (Continued)

| Symbol                                                                      | DDR4-2133 <sup>1</sup> | DDR4-2400 | DDR4-2666 | DDR4-2933 | DDR4-3200 | Unit | Notes                       |

|-----------------------------------------------------------------------------|------------------------|-----------|-----------|-----------|-----------|------|-----------------------------|

| I <sub>DD4R</sub> : Burst read current                                      | 250                    | 270       | 292       | 314       | 336       | mA   | 4, 14,<br>13, 11            |

| I <sub>DD4W</sub> : Burst write current                                     | 230                    | 246       | 264       | 282       | 300       | mA   | 4, 11,<br>15, 16,<br>17, 18 |

| I <sub>DD5R</sub> : Burst refresh current (1X<br>REF)                       | 100                    | 106       | 112       | 118       | 124       | mA   | 4, 19,<br>20                |

| I <sub>PP5R</sub> : Burst refresh I <sub>PP</sub> current (1X REF)          | 10                     | 10        | 10        | 10        | 10        | mA   |                             |

| I <sub>DD6N</sub> : Self refresh current; 0–85°C                            | 60                     | 60        | 60        | 60        | 60        | mA   | 11, 21                      |

| I <sub>DD6E</sub> : Self refresh current; 0–95°C                            | 70                     | 70        | 70        | 70        | 70        | mA   | 11, 22                      |

| I <sub>DD6R</sub> : Self refresh current; 0–45°C                            | 40                     | 40        | 40        | 40        | 40        | mA   | 11, 23,<br>24               |

| I <sub>DD6A</sub> : Auto self refresh current (25°C)                        | 17.2                   | 17.2      | 17.2      | 17.2      | 17.2      | mA   | 11, 24                      |

| I <sub>DD6A</sub> : Auto self refresh current (45°C)                        | 40                     | 40        | 40        | 40        | 40        | mA   | 11, 24                      |

| <b>I<sub>DD6A</sub></b> : Auto self refresh current (75°C)                  | 60                     | 60        | 60        | 60        | 60        | mA   | 11, 24                      |

| <b>I<sub>PP6X</sub></b> : Auto self refresh current I <sub>PP</sub> current | 10                     | 10        | 10        | 10        | 10        | mA   | 11, 24                      |

| I <sub>DD7</sub> : Bank interleave read current                             | 340                    | 350       | 360       | 370       | 380       | mA   | 4                           |

| $I_{PP7}$ : Bank interleave read $I_{PP}$ current                           | 30                     | 30        | 30        | 30        | 30        | mA   |                             |

| I <sub>DD8</sub> : Maximum power-down current                               | 50                     | 50        | 50        | 50        | 50        | mA   | 11                          |

- Notes: 1. DDR4-1600 and DDR4-1866 use the same I<sub>DD</sub> limits as DDR4-2133.

- 2. When additive latency is enabled for I<sub>DD0</sub>, current changes by approximately 0%.

- 3.  $I_{PP0}$  test and limit is applicable for  $I_{DD0}$  and  $I_{DD1}$  conditions.

- 4. The  $I_{DD}$  values must be derated (increased) when operated outside of the range  $0^{\circ}C \leq T_{C}$ ≤ 85°C:

When  $T_C < 0$ °C:  $I_{DD2P}$  and  $I_{DD3P}$  must be derated by 6%;  $I_{DD4R}$  and  $I_{DD4W}$  must be derated by 4%; and I<sub>DD7</sub> must be derated by 11%.

When  $T_C > 85^{\circ}C$ :  $I_{DD0}$ ,  $I_{DD1}$ ,  $I_{DD2N}$ ,  $I_{DD2NT}$ ,  $I_{DD2Q}$ ,  $I_{DD3N}$ ,  $I_{DD3P}$ ,  $I_{DD4R}$ ,  $I_{DD4W}$ , and  $I_{DD5R}$  must be derated by 3%; I<sub>DD2P</sub> must be derated by 40%.

- 5. When additive latency is enabled for IDD1, current changes by approximately +4%.

- 6. When additive latency is enabled for  $I_{DD2N}$ , current changes by approximately +0%.

- 7. When DLL is disabled for  $I_{DD2N}$ , current changes by approximately -23%.

- 8. When CAL is enabled for  $I_{DD2N}$ , current changes by approximately -25%.

- 9. When gear-down is enabled for I<sub>DD2N</sub>, current changes by approximately 0%.

- 10. When CA parity is enabled for I<sub>DD2N</sub>, current changes by approximately +7%.

#### 16Gb: x16 TwinDie Single Rank DDR4 SDRAM Current Specifications – Limits

- 11.  $I_{PP3N}$  test and limit is applicable for all  $I_{DD2x}$ ,  $I_{DD3x}$ ,  $I_{DD4x}$ ,  $I_{DD6x}$ , and  $I_{DD8}$  conditions; that is, testing  $I_{PP3N}$  should satisfy the  $I_{PP}$ s for the noted  $I_{DD}$  tests.

- 12. When additive latency is enabled for I<sub>DD3N</sub>, current changes by approximately +0.6%.

- 13. When additive latency is enabled for I<sub>DD4R</sub>, current changes by approximately +5%.

- 14. When read DBI is enabled for I<sub>DD4R</sub>, current changes by approximately 0%.

- 15. When additive latency is enabled for  $I_{DD4W}$ , current changes by approximately +4%.

- 16. When write DBI is enabled for I<sub>DD4W</sub>, current changes by approximately 0%.

- 17. When write CRC is enabled for I<sub>DD4W</sub>, current changes by approximately –3%.

- 18. When CA parity is enabled for  $I_{DD4W}$ , current changes by approximately +12%.

- 19. When 2X REF is enabled for I<sub>DD5R</sub>, current changes by approximately –14%.

- 20. When 4X REF is enabled for I<sub>DD5R</sub>, current changes by approximately –33%.

- 21. Applicable for MR2 settings A7 = 0 and A6 = 0; manual mode with normal temperature range of operation  $(0-85^{\circ}C)$ .

- 22. Applicable for MR2 settings A7 = 1 and A7 = 0; manual mode with extended temperature range of operation  $(0-95^{\circ}C)$ .

- 23. Applicable for MR2 settings A7 = 0 and A7 = 1; manual mode with reduced temperature range of operation  $(0-45^{\circ}C)$ .

- 24. I<sub>DD6R</sub> and I<sub>DD6A</sub> values are typical.

Table 10: x16  $I_{DD}$ ,  $I_{PP}$ , and  $I_{DDO}$  Current Limits – Rev. D

| Symbol                                                                              | DDR4-2133 <sup>1</sup> | DDR4-2400 | DDR4-2666 | DDR4-2933 | DDR4-3200 | Unit | Notes                       |

|-------------------------------------------------------------------------------------|------------------------|-----------|-----------|-----------|-----------|------|-----------------------------|

| <b>I<sub>DD0</sub></b> : One bank ACTIVATE-to-<br>PRECHARGE current                 | 90                     | 96        | 102       | 108       | 114       | mA   | 2, 3, 4                     |

| <b>I<sub>PP0</sub></b> : One bank ACTIVATE-to-<br>PRECHARGE I <sub>PP</sub> current | 6                      | 6         | 6         | 6         | 6         | mA   |                             |

| <b>I<sub>DD1</sub></b> : One bank ACTIVATE-to-<br>READ-to-PRECHARGE current         | 114                    | 120       | 126       | 132       | 138       | mA   | 3, 4, 5                     |

| <b>I<sub>DD2N</sub>:</b> Precharge standby current                                  | 66                     | 68        | 70        | 72        | 74        | mA   | 4, 6, 7,<br>8, 9, 10,<br>11 |

| I <sub>DD2NT</sub> : Precharge standby<br>ODT current                               | 90                     | 100       | 100       | 110       | 120       | mA   | 4, 11                       |

| <b>I<sub>DD2P</sub></b> : Precharge power-down current                              | 50                     | 50        | 50        | 50        | 50        | mA   | 4, 11                       |

| <b>I</b> <sub>DD2Q</sub> : Precharge quiet stand-<br>by current                     | 60                     | 60        | 60        | 60        | 60        | mA   | 4, 11                       |

| I <sub>DD3N</sub> : Active standby current                                          | 90                     | 96        | 102       | 108       | 112       | mA   | 4, 11                       |

| $I_{PP3N}$ : Active standby $I_{PP}$ current                                        | 6                      | 6         | 6         | 6         | 6         | mA   |                             |

| $I_{DD3P}$ : Active power-down current                                              | 70                     | 74        | 78        | 82        | 86        | mA   | 4, 11                       |

| I <sub>DD4R</sub> : Burst read current                                              | 250                    | 270       | 292       | 314       | 336       | mA   | 4, 14,<br>13, 11            |

| I <sub>DD4W</sub> : Burst write current                                             | 250                    | 264       | 284       | 300       | 320       | mA   | 4, 11,<br>15, 16,<br>17, 18 |

### 16Gb: x16 TwinDie Single Rank DDR4 SDRAM **Current Specifications – Limits**

#### Table 10: x16 I<sub>DD</sub>, I<sub>PP</sub>, and I<sub>DDQ</sub> Current Limits – Rev. D (Continued)

| Symbol                                                                | DDR4-2133 <sup>1</sup> | DDR4-2400 | DDR4-2666 | DDR4-2933 | DDR4-3200 | Unit | Notes         |

|-----------------------------------------------------------------------|------------------------|-----------|-----------|-----------|-----------|------|---------------|

| I <sub>DDSR</sub> : Burst refresh current (1X REF)                    | 112                    | 116       | 122       | 128       | 132       | mA   | 4, 19, 20     |

| I <sub>PP5R</sub> : Burst refresh I <sub>PP</sub> current (1X REF)    | 10                     | 10        | 10        | 10        | 10        | mA   |               |

| I <sub>DD6N</sub> : Self refresh current; 0–<br>85°C                  | 62                     | 62        | 62        | 62        | 62        | mA   | 11, 21        |

| I <sub>DD6E</sub> : Self refresh current; 0–<br>95°C                  | 72                     | 72        | 72        | 72        | 72        | mA   | 11, 22        |

| I <sub>DD6R</sub> : Self refresh current; 0–45°C                      | 42                     | 42        | 42        | 42        | 42        | mA   | 11, 23,<br>24 |

| I <sub>DD6A</sub> : Auto self refresh current (25°C)                  | 17.2                   | 17.2      | 17.2      | 17.2      | 17.2      | mA   | 11, 24        |

| I <sub>DD6A</sub> : Auto self refresh current (45°C)                  | 42                     | 42        | 42        | 42        | 42        | mA   | 11, 24        |

| <b>I<sub>DD6A</sub>:</b> Auto self refresh current (75°C)             | 62                     | 62        | 62        | 62        | 62        | mA   | 11, 24        |

| I <sub>PP6X</sub> : Auto self refresh current I <sub>PP</sub> current | 10                     | 10        | 10        | 10        | 10        | mA   | 11, 24        |

| I <sub>DD7</sub> : Bank interleave read current                       | 340                    | 350       | 360       | 370       | 380       | mA   | 4             |

| <b>I<sub>PP7</sub></b> : Bank interleave read I <sub>PP</sub> current | 30                     | 30        | 30        | 30        | 30        | mA   |               |

| I <sub>DD8</sub> : Maximum power-down current                         | 50                     | 50        | 50        | 50        | 50        | mA   | 11            |

- Notes: 1. DDR4-1600 and DDR4-1866 use the same I<sub>DD</sub> limits as DDR4-2133.

- 2. When additive latency is enabled for I<sub>DD0</sub>, current changes by approximately 0%.

- 3.  $I_{PP0}$  test and limit is applicable for  $I_{DD0}$  and  $I_{DD1}$  conditions.

- 4. The  $I_{DD}$  values must be derated (increased) when operated outside of the range  $0^{\circ}C \leq T_{C}$ ≤ 85°C:

When  $T_C < 0$ °C:  $I_{DD2P}$  and  $I_{DD3P}$  must be derated by 6%;  $I_{DD4R}$  and  $I_{DD4W}$  must be derated by 4%; and I<sub>DD7</sub> must be derated by 11%.

When  $T_C > 85$ °C:  $I_{DD0}$ ,  $I_{DD1}$ ,  $I_{DD2N}$ ,  $I_{DD2NT}$ ,  $I_{DD2Q}$ ,  $I_{DD3N}$ ,  $I_{DD3P}$ ,  $I_{DD4R}$ ,  $I_{DD4W}$ , and  $I_{DD5R}$  must be derated by 3%; I<sub>DD2P</sub> must be derated by 40%.

- 5. When additive latency is enabled for IDD1, current changes by approximately +4%.

- 6. When additive latency is enabled for I<sub>DD2N</sub>, current changes by approximately +0%.

- 7. When DLL is disabled for I<sub>DD2N</sub>, current changes by approximately –23%.

- 8. When CAL is enabled for I<sub>DD2N</sub>, current changes by approximately –25%.

- 9. When gear-down is enabled for I<sub>DD2N</sub>, current changes by approximately 0%.

- 10. When CA parity is enabled for  $I_{DD2N}$ , current changes by approximately +7%.

- 11.  $I_{PP3N}$  test and limit is applicable for all  $I_{DD2x}$ ,  $I_{DD3x}$ ,  $I_{DD4x}$ ,  $I_{DD6x}$ , and  $I_{DD8}$  conditions; that is, testing  $I_{PP3N}$  should satisfy the  $I_{PP}$ s for the noted  $I_{DD}$  tests.

- 12. When additive latency is enabled for I<sub>DD3N</sub>, current changes by approximately +0.6%.

- 13. When additive latency is enabled for IDD4R, current changes by approximately +5%.

#### 16Gb: x16 TwinDie Single Rank DDR4 SDRAM Current Specifications – Limits

- 14. When read DBI is enabled for  $I_{DD4R}$ , current changes by approximately 0%.

- 15. When additive latency is enabled for I<sub>DD4W</sub>, current changes by approximately +4%.

- 16. When write DBI is enabled for I<sub>DD4W</sub>, current changes by approximately 0%.

- 17. When write CRC is enabled for  $I_{DD4W}$ , current changes by approximately -3%.

- 18. When CA parity is enabled for  $I_{DD4W}$ , current changes by approximately +12%.

- 19. When 2X REF is enabled for I<sub>DD5R</sub>, current changes by approximately –14%.

- 20. When 4X REF is enabled for I<sub>DD5R</sub>, current changes by approximately –33%.

- 21. Applicable for MR2 settings A7 = 0 and A6 = 0; manual mode with normal temperature range of operation  $(0-85^{\circ}C)$ .

- 22. Applicable for MR2 settings A7 = 1 and A7 = 0; manual mode with extended temperature range of operation  $(0-95^{\circ}C)$ .

- 23. Applicable for MR2 settings A7 = 0 and A7 = 1; manual mode with reduced temperature range of operation  $(0-45^{\circ}C)$ .

- 24. I<sub>DD6R</sub> and I<sub>DD6A</sub> values are typical.

Table 11: x16 I<sub>DD</sub>, I<sub>PP</sub>, and I<sub>DDQ</sub> Current Limits – Rev. E

| Symbol                                                                        | DDR4-2133 <sup>1</sup> | DDR4-2400 | DDR4-2666 | DDR4-2933 | DDR4-3200 | Unit | Notes                       |

|-------------------------------------------------------------------------------|------------------------|-----------|-----------|-----------|-----------|------|-----------------------------|

| I <sub>DD0</sub> : One bank ACTIVATE-to-<br>PRECHARGE current                 | 90                     | 96        | 102       | 108       | 114       | mA   | 2, 3, 4                     |

| I <sub>PP0</sub> : One bank ACTIVATE-to-<br>PRECHARGE I <sub>PP</sub> current | 6                      | 6         | 6         | 6         | 6         | mA   |                             |

| I <sub>DD1</sub> : One bank ACTIVATE-to-<br>READ-to-PRECHARGE current         | 114                    | 120       | 126       | 132       | 138       | mA   | 3, 4, 5                     |

| I <sub>DD2N</sub> : Precharge standby current                                 | 66                     | 68        | 70        | 72        | 74        | mA   | 4, 6, 7, 8,<br>9, 10, 11    |

| I <sub>DD2NT</sub> : Precharge standby ODT current                            | 90                     | 100       | 100       | 110       | 120       | mA   | 4, 11                       |

| I <sub>DD2P</sub> : Precharge power-down current                              | 50                     | 50        | 50        | 50        | 50        | mA   | 4, 11                       |

| <b>I<sub>DD2Q</sub></b> : Precharge quiet standby current                     | 60                     | 60        | 60        | 60        | 60        | mA   | 4, 11                       |

| I <sub>DD3N</sub> : Active standby current                                    | 90                     | 96        | 102       | 108       | 112       | mA   | 4, 11                       |

| $I_{PP3N}$ : Active standby $I_{PP}$ current                                  | 6                      | 6         | 6         | 6         | 6         | mA   |                             |

| <b>I<sub>DD3P</sub></b> : Active power-down current                           | 70                     | 74        | 78        | 82        | 86        | mA   | 4, 11                       |

| I <sub>DD4R</sub> : Burst read current                                        | 270                    | 290       | 312       | 334       | 356       | mA   | 4, 14, 13,<br>11            |

| I <sub>DD4W</sub> : Burst write current                                       | 240                    | 256       | 274       | 292       | 310       | mA   | 4, 11, 15,<br>16, 17,<br>18 |

| <b>I<sub>DD5R</sub></b> : Burst refresh current (1X REF)                      | 112                    | 116       | 122       | 128       | 132       | mA   | 4, 19, 20                   |

| I <sub>PPSR</sub> : Burst refresh I <sub>PP</sub> current (1X REF)            | 10                     | 10        | 10        | 10        | 10        | mA   |                             |

| I <sub>DD6N</sub> : Self refresh current; 0–85°C                              | 68                     | 68        | 68        | 68        | 68        | mA   | 11, 21                      |

Table 11: x16 I<sub>DD</sub>, I<sub>PP</sub>, and I<sub>DDO</sub> Current Limits – Rev. E (Continued)

| Symbol                                                                | DDR4-2133 <sup>1</sup> | DDR4-2400 | DDR4-2666 | DDR4-2933 | DDR4-3200 | Unit | Notes         |

|-----------------------------------------------------------------------|------------------------|-----------|-----------|-----------|-----------|------|---------------|

| I <sub>DD6E</sub> : Self refresh current; 0–<br>95°C                  | 92                     | 92        | 92        | 92        | 92        | mA   | 11, 22        |

| I <sub>DD6R</sub> : Self refresh current; 0–<br>45°C                  | 42                     | 42        | 42        | 42        | 42        | mA   | 11, 23,<br>24 |

| <b>I<sub>DD6A</sub></b> : Auto self refresh current (25°C)            | 17.2                   | 17.2      | 17.2      | 17.2      | 17.2      | mA   | 11, 24        |

| <b>I<sub>DD6A</sub></b> : Auto self refresh current (45°C)            | 42                     | 42        | 42        | 42        | 42        | mA   | 11, 24        |

| <b>I<sub>DD6A</sub></b> : Auto self refresh current (75°C)            | 62                     | 62        | 62        | 62        | 62        | mA   | 11, 24        |

| I <sub>PP6X</sub> : Auto self refresh current I <sub>PP</sub> current | 10                     | 10        | 10        | 10        | 10        | mA   | 11, 24        |

| I <sub>DD7</sub> : Bank interleave read current                       | 348                    | 358       | 368       | 378       | 388       | mA   | 4             |

| <b>I<sub>PP7</sub></b> : Bank interleave read I <sub>PP</sub> current | 30                     | 30        | 30        | 30        | 30        | mA   |               |

| I <sub>DD8</sub> : Maximum power-down current                         | 50                     | 50        | 50        | 50        | 50        | mA   | 11            |

- Notes: 1. DDR4-1600 and DDR4-1866 use the same I<sub>DD</sub> limits as DDR4-2133.

- 2. When additive latency is enabled for  $I_{DD0}$ , current changes by approximately 0%.

- 3. IPPO test and limit is applicable for IDDO and IDD1 conditions.

- 4. The  $I_{DD}$  values must be derated (increased) when operated outside of the range  $0^{\circ}C \leq T_{C}$ ≤ 85°C:

When  $T_C < 0^{\circ}C$ :  $I_{DD2P}$  and  $I_{DD3P}$  must be derated by 6%;  $I_{DD4R}$  and  $I_{DD4W}$  must be derated by 4%; and I<sub>DD7</sub> must be derated by 11%.

When  $T_C > 85$ °C:  $I_{DD0}$ ,  $I_{DD1}$ ,  $I_{DD2N}$ ,  $I_{DD2NT}$ ,  $I_{DD2Q}$ ,  $I_{DD3N}$ ,  $I_{DD3P}$ ,  $I_{DD4R}$ ,  $I_{DD4W}$ , and  $I_{DD5R}$  must be derated by 3%; I<sub>DD2P</sub> must be derated by 40%.

- 5. When additive latency is enabled for I<sub>DD1</sub>, current changes by approximately +4%.

- 6. When additive latency is enabled for  $I_{DD2N}$ , current changes by approximately +0%.

- 7. When DLL is disabled for  $I_{DD2N}$ , current changes by approximately -23%.

- 8. When CAL is enabled for I<sub>DD2N</sub>, current changes by approximately –25%.

- 9. When gear-down is enabled for I<sub>DD2N</sub>, current changes by approximately 0%.

- 10. When CA parity is enabled for I<sub>DD2N</sub>, current changes by approximately +7%.

- 11.  $I_{PP3N}$  test and limit is applicable for all  $I_{DD2x}$ ,  $I_{DD3x}$ ,  $I_{DD4x}$ ,  $I_{DD6x}$ , and  $I_{DD8}$  conditions; that is, testing I<sub>PP3N</sub> should satisfy the I<sub>PP</sub>s for the noted I<sub>DD</sub> tests.

- 12. When additive latency is enabled for I<sub>DD3N</sub>, current changes by approximately +0.6%.

- 13. When additive latency is enabled for IDD4R, current changes by approximately +5%.

- 14. When read DBI is enabled for I<sub>DD4R</sub>, current changes by approximately 0%.

- 15. When additive latency is enabled for I<sub>DD4W</sub>, current changes by approximately +4%.

- 16. When write DBI is enabled for I<sub>DD4W</sub>, current changes by approximately 0%.

- 17. When write CRC is enabled for I<sub>DD4W</sub>, current changes by approximately –3%.

- 18. When CA parity is enabled for  $I_{DD4W}$ , current changes by approximately +12%.

- 19. When 2X REF is enabled for I<sub>DD5R</sub>, current changes by approximately -14%.

# 16Gb: x16 TwinDie Single Rank DDR4 SDRAM Current Specifications – Limits

- 20. When 4X REF is enabled for  $I_{DD5R}$ , current changes by approximately -33%.

- 21. Applicable for MR2 settings A7 = 0 and A6 = 0; manual mode with normal temperature range of operation  $(0-85^{\circ}C)$ .

- 22. Applicable for MR2 settings A7 = 1 and A7 = 0; manual mode with extended temperature range of operation  $(0-95^{\circ}C)$ .

- 23. Applicable for MR2 settings A7 = 0 and A7 = 1; manual mode with reduced temperature range of operation  $(0-45^{\circ}C)$ .

- 24. I<sub>DD6R</sub> and I<sub>DD6A</sub> values are typical.

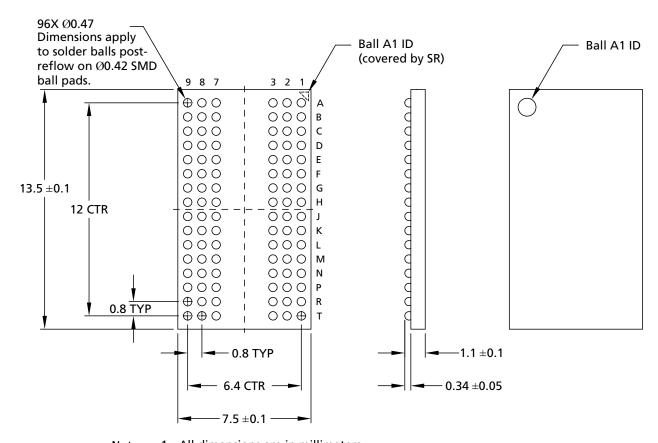

# **Package Dimensions**

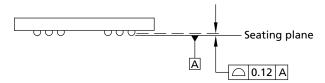

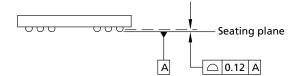

Figure 5: 96-Ball FBGA Die Rev. A (package code HBA)

Notes:

- 1. All dimensions are in millimeters.

- 2. Solder ball material: SAC302 (96.8% Sn, 3% Ag, 0.2% Cu).

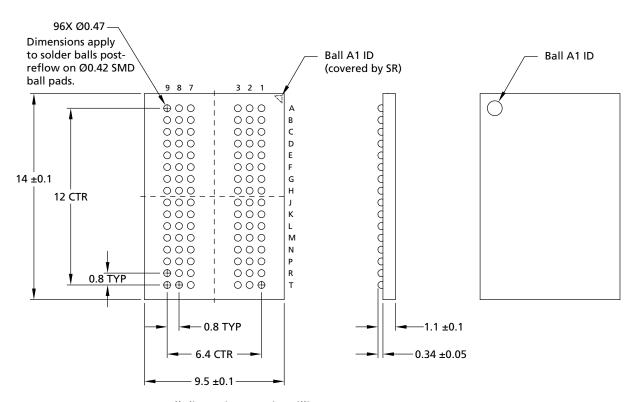

Figure 6: 96-Ball FBGA Die Rev. B (package code WBU)

Notes: 1. All dimensions are in millimeters.

2. Solder ball material: SAC302 (96.8% Sn, 3% Ag, 0.2% Cu).

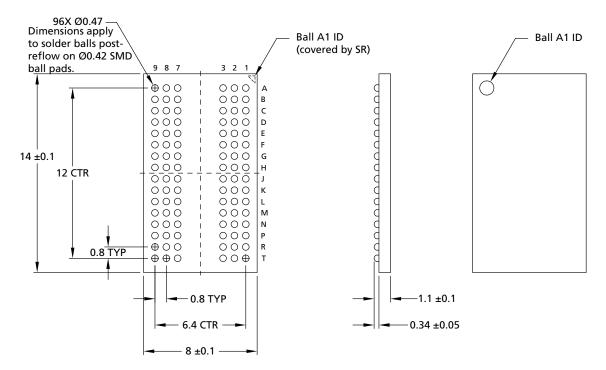

Figure 7: 96-Ball FBGA Die Rev. E (package code KNR)

Notes: 1. All dimensions are in millimeters.

2. Solder ball material: SAC302 (96.8% Sn, 3% Ag, 0.2% Cu).

8000 S. Federal Way, P.O. Box 6, Boise, ID 83707-0006, Tel: 208-368-4000 www.micron.com/products/support Sales inquiries: 800-932-4992

Micron and the Micron logo are trademarks of Micron Technology, Inc. TwinDie is a trademark of Micron Technology, Inc.

All other trademarks are the property of their respective owners.

This data sheet contains minimum and maximum limits specified over the power supply and temperature range set forth herein. Although considered final, these specifications are subject to change, as further product development and data characterization sometimes occur.