## National Semiconductor

## NSC800™ High-Performance Low-Power CMOS Microprocessor

## **General Description**

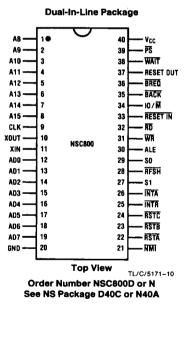

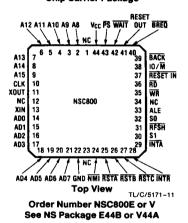

The NSC800 is an 8-bit CMOS microprocessor that functions as the central processing unit (CPU) in National Semiconductor's NSC800 microcomputer family. National's microCMOS technology used to fabricate this device provides system designers with performance equivalent to comparable NMOS products, but with the low power advantage of CMOS. Some of the many system functions incorporated on the device, are vectored priority interrupts, refresh control, power-save feature and interrupt acknowledge. The NSC800 is available in dual-in-line and surface mounted chip carrier packages.

The system designer can choose not only from the dedicated CMOS peripherals that allow direct interfacing to the NSC800 but from the full line of National's CMOS products to allow a low-power system solution. The dedicated peripherals include NSC810A RAM I/O Timer, NSC858 UART, and NSC831 I/O.

All devices are available in commercial, industrial and military temperature ranges along with two added reliability flows. The first is an extended burn in test and the second is the military class C screening in accordance with Method 5004 of MIL-STD-883.

### **Features**

- Fully compatible with Z80<sup>®</sup> instruction set: Powerful set of 158 instructions 10 addressing modes 22 internal registers

- Low power: 50 mW at 5V V<sub>CC</sub>

- Unique power-save feature

- Multiplexed bus structure

- Schmitt trigger input on reset

- On-chip bus controller and clock generator

- Variable power supply 2.4V-6.0V

- On-chip 8-bit dynamic RAM refresh circuitry

- Speed: 1.0 µs instruction cycle at 4.0 MHz

| NSC800-4  | 4.0 MHz |

|-----------|---------|

| NSC800-35 | 3.5 MHz |

| NSC800-3  | 2.5 MHz |

| NSC800-1  | 1.0 MHz |

|           |         |

- Capable of addressing 64k bytes of memory and 256 I/O devices

- Five interrupt request lines on-chip

**NSC800**

microCMOS

7

## **Table of Contents**

- **1.0 ABSOLUTE MAXIMUM RATINGS**

- 2.0 OPERATING CONDITIONS

- 3.0 DC ELECTRICAL CHARACTERISTICS

- 4.0 AC ELECTRICAL CHARACTERISTICS

#### 5.0 TIMING WAVEFORMS NSC800 HARDWARE

## 6.0 PIN DESCRIPTIONS

6.1 Input Signals 6.2 Output Signals 6.3 Input/Output Signals

#### 7.0 CONNECTION DIAGRAMS

#### **8.0 FUNCTIONAL DESCRIPTION**

- 8.1 Register Array

- 8.2 Dedicated Registers

- 8.2.1 Program Counter

- 8.2.2 Stack Pointer

- 8.2.3 Index Register

- 8.2.4 Interrupt Register

- 8.2.5 Refresh Register

- 8.3 CPU Working and Alternate Register Sets 8.3.1 CPU Working Registers 8.3.2 Alternate Registers

#### 8.4 Register Functions

- 8.4.1 Accumulator

- 8.4.2 F Register-Flags

- 8.4.3 Carry (C)

- 8.4.4 Adds/Subtract (N)

- 8.4.5 Parity/Overflow (P/V)

- 8.4.6 Half Carry (H)

- 8.4.7 Zero Flag (Z)

- 8.4.8 Sign Flag (S)

- 8.4.9 Additional General Purpose Registers

- 8.4.10 Alternate Configurations

- 8.5 Arithmetic Logic Unit (ALU)

- 8.6 Instruction Register and Decoder

#### 9.0 TIMING AND CONTROL

- 9.1 Internal Clock Generator

- 9.2 CPU Timing

- 9.3 Initialization

- 9.4 Power Save Feature

#### 9.0 TIMING AND CONTROL

9.5 Bus Access Control 9.6 Interrupt Control

#### **NSC800 SOFTWARE**

#### **10.0 INTRODUCTION**

#### 11.0 ADDRESSING MODES

- 11.1 Register 11.2 Implied 11.3 Immediate 11.4 Immediate Extended 11.5 Direct Addressing 11.6 Register Indirect 11.7 Indexed 11.8 Relative 11.9 Modified Page Zero 11.10 Bit **12.0 INSTRUCTION SET** 12.1 Instruction Set Index/Alphabetical 12.2 Instruction Set Mnemonic Notation 12.3 Assembled Object Code Notation 12.4 8-Bit Loads 12.5 16-Bit Loads 12.6 8-Bit Arithmetic 12.7 16-Bit Arithmetic

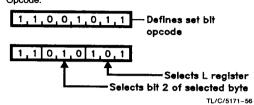

- 12.8 Bit Set, Reset, and Test

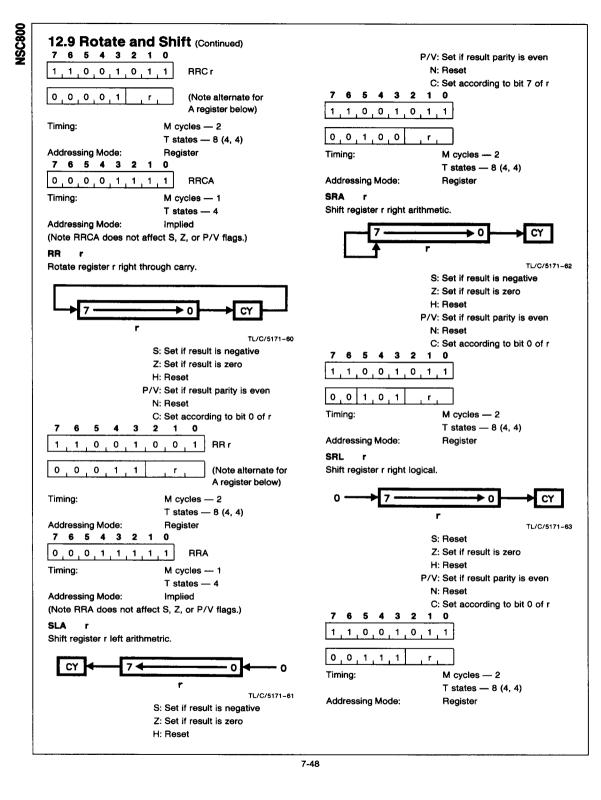

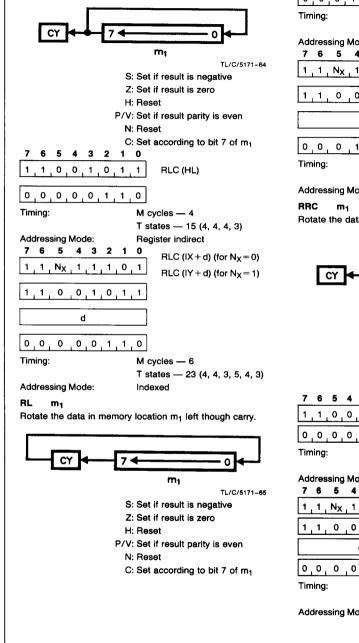

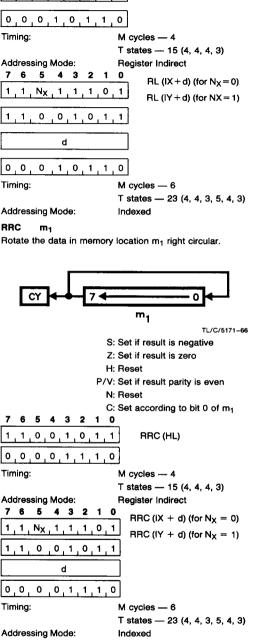

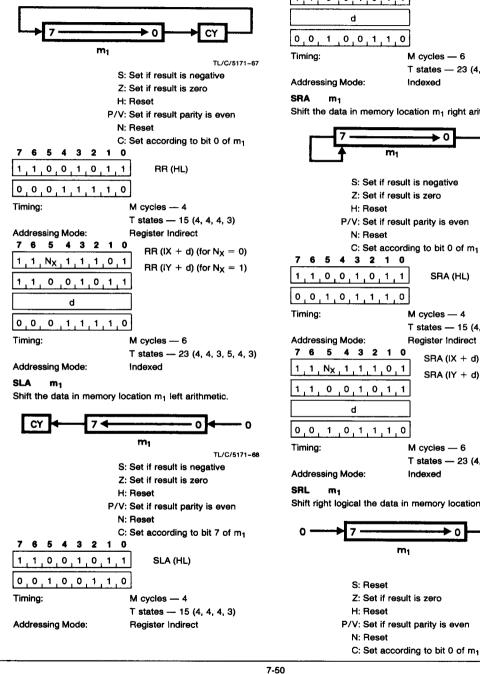

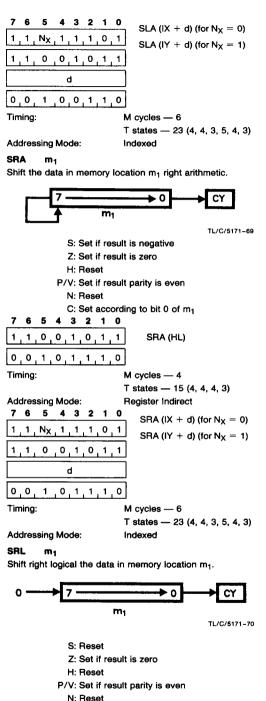

- 12.9 Rotate and Shift

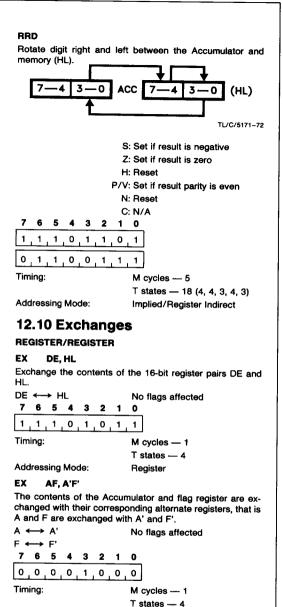

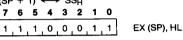

- 12.10 Exchanges

- 12.11 Memory Block Moves and Searches

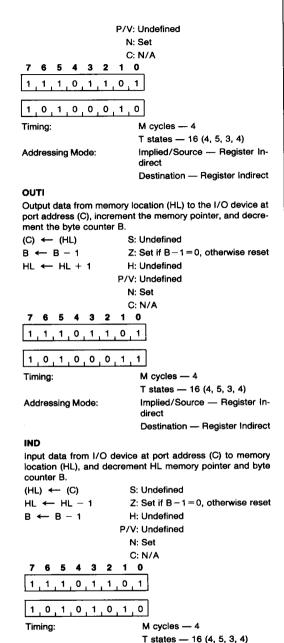

- 12.12 Input/Output

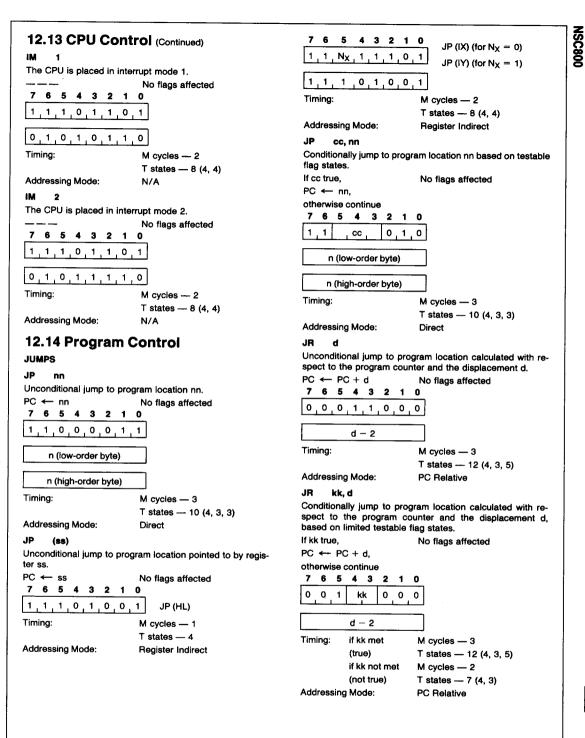

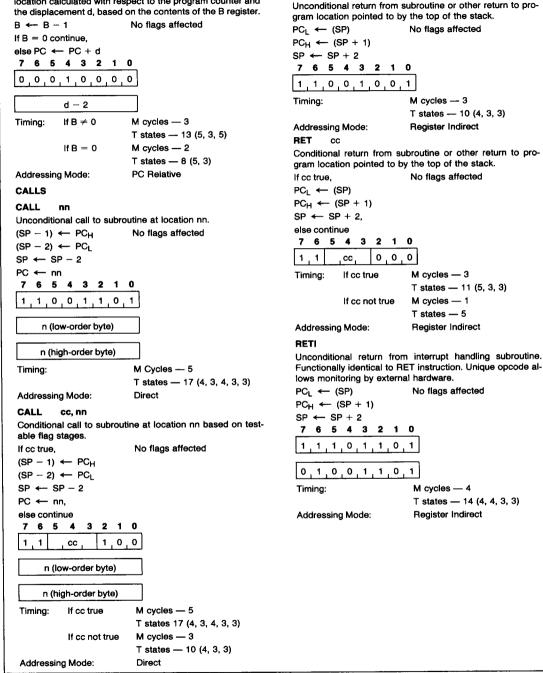

- 12.13 CPU Control

- 12.14 Program Control

- 12.15 Instruction Set: Alphabetical Order

- 12.16 Instruction Set: Numerical Order

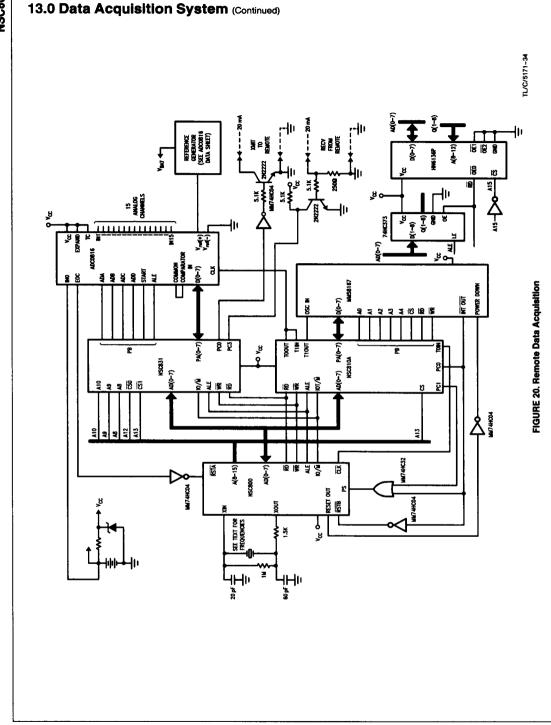

#### **13.0 DATA ACQUISITION SYSTEM**

#### 14.0 NSC800M/883B MIL STD 883/CLASS C SCREENING

- **15.0 BURN-IN CIRCUITS**

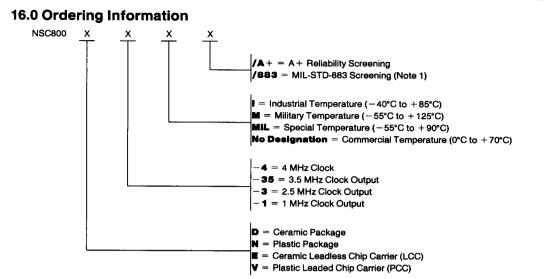

- **16.0 ORDERING INFORMATION**

- 17.0 RELIABILITY INFORMATION

## 1.0 Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required. please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Storage Temperature                          | -65°C to +150°C                 |

|----------------------------------------------|---------------------------------|

| Voltage on Any Pin<br>with Respect to Ground | -0.3V to V <sub>CC</sub> + 0.3V |

| Maximum V <sub>CC</sub>                      | 7V                              |

| Power Dissipation                            | 1W                              |

| Lead Temp. (Soldering, 10 seconds)           | 300°C                           |

#### 2.0 Operating Conditions NSC800-1

NSC800-3

NSC800-4

NSC800-4MIL

$T_A = -40^{\circ}C \text{ to } +85^{\circ}C$

$\rightarrow$  T<sub>A</sub> = -55°C to +90°C

NSC800

## 3.0 DC Electrical Characteristics $V_{CC} = 5V \pm 10\%$ , GND = 0V, unless otherwise specified.

| Symbol           | Parameter                    | Conditions                                                                                                                                                                             | Min                  | Тур | Max                 | Units |

|------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|---------------------|-------|

| VIH              | Logical 1 Input Voltage      |                                                                                                                                                                                        | 0.8 V <sub>CC</sub>  |     | Vcc                 | V     |

| VIL              | Logical 0 Input Voltage      |                                                                                                                                                                                        | 0                    |     | 0.2 V <sub>CC</sub> | V     |

| V <sub>HY</sub>  | Hysteresis at RESET IN input | $V_{CC} = 5V$                                                                                                                                                                          | 0.25                 | 0.5 |                     | v     |

| VOH1             | Logical 1 Output Voltage     | $I_{OUT} = -1.0 \text{ mA}$                                                                                                                                                            | 2.4                  |     |                     | v     |

| V <sub>OH2</sub> | Logical 1 Output Voltage     | $I_{OUT} = -10 \mu A$                                                                                                                                                                  | V <sub>CC</sub> -0.5 |     |                     | v     |

| V <sub>OL1</sub> | Logical 0 Output Voltage     | I <sub>OUT</sub> = 2 mA                                                                                                                                                                | 0                    |     | 0.4                 | v     |

| VOL2             | Logical 0 Output Voltage     | l <sub>OUT</sub> = 10 μA                                                                                                                                                               | 0                    |     | 0.1                 | V     |

| Ι <sub>ΙL</sub>  | Input Leakage Current        | $0 \le V_{\rm IN} \le V_{\rm CC}$                                                                                                                                                      | - 10.0               |     | 10.0                | μA    |

| IOL              | Output Leakage Current       | $0 \le V_{IN} \le V_{CC}$                                                                                                                                                              | - 10.0               |     | 10.0                | μA    |

| lcc              | Active Supply Current        | $I_{OUT} = 0, f_{(XIN)} = 2 \text{ MHz}, T_A = 25^{\circ}\text{C}$                                                                                                                     |                      | 8   | 11                  | mA    |

| lcc              | Active Supply Current        | $I_{OUT} = 0, f_{(XIN)} = 5 \text{ MHz}, T_A = 25^{\circ}\text{C}$                                                                                                                     |                      | 10  | 15                  | mA    |

| lcc              | Active Supply Current        | $I_{OUT} = 0$ , $f_{(XIN)} = 7$ MHz,<br>$T_A = 25^{\circ}C$                                                                                                                            |                      | 15  | 21                  | mA    |

| lcc              | Active Supply Current        | $I_{OUT} = 0, f_{(XIN)} = 8 \text{ MHz}, T_A = 25^{\circ}\text{C}$                                                                                                                     |                      | 15  | 21                  | mA    |

| la 👘             | Quiescent Current            | $\begin{split} I_{OUT} &= 0, \overline{PS} = 0, V_{IN} = 0 \text{ or } V_{IN} = V_{CC} \\ f_{(XIN)} &= 0 \text{ MHz}, T_A = 25^\circ\text{C}, X_{IN} = 0, \text{ CLK} = 1 \end{split}$ |                      | 2   | 5                   | mA    |

| IPS              | Power-Save Current           | $\begin{split} I_{OUT} &= 0, \ \overline{PS} = 0, \ V_{IN} = 0 \ \text{or} \ V_{IN} = V_{CC} \\ f_{(XIN)} &= 5.0 \ \text{MHz} \ , \ T_A = 25^{\circ} \end{split}$                      |                      | 5   | 7                   | mA    |

| CIN              | Input Capacitance            |                                                                                                                                                                                        |                      | 6   | 10                  | pF    |

| COUT             | Output Capacitance           |                                                                                                                                                                                        |                      | 8   | 12                  | pF    |

| Vcc              | Power Supply Voltage         | (Note 2)                                                                                                                                                                               | 2.4                  | 5   | 6                   | v     |

Note 1: Absolute Maximum Ratings indicate limits beyond which permanent damage may occur. Continuous operation at these limits is not intended and should be limited to those conditions specified under DC Electrical Characteristics.

Note 2: CPU operation at lower voltages will reduce the maximum operating speed. Operation at voltages other than 5V ±10% is guaranteed by design, not tested.

|                        |                                                                | NSC  | 300-1 | NSC | 800-3 | NSC | 800-35 | NSC | 800-4 | [     |                                                     |

|------------------------|----------------------------------------------------------------|------|-------|-----|-------|-----|--------|-----|-------|-------|-----------------------------------------------------|

| Symbol                 | Parameter                                                      | Min  | Max   | Min | Max   | Min | Max    | Min | Max   | Units | Notes                                               |

| t <sub>X</sub>         | Period at XIN and XOUT<br>Pins                                 | 500  | 3333  | 200 | 3333  | 142 | 3333   | 125 | 3333  | ns    |                                                     |

| Т                      | Period at Clock Output<br>(=2 t <sub>X</sub> )                 | 1000 | 6667  | 400 | 6667  | 284 | 6667   | 250 | 6667  | ns    |                                                     |

| t <sub>R</sub>         | Clock Rise Time                                                |      | 110   |     | 110   |     | 90     |     | 80    | ns    | Measured from<br>10%–90% of signal                  |

| t⊨                     | Clock Fall Time                                                |      | 70    |     | 60    |     | 55     |     | 50    | ns    | Measured from 10%–90% of signal                     |

| tL                     | Clock Low Time                                                 | 435  |       | 150 |       | 90  |        | 80  |       | ns    | 50% duty cycle, square wave input on XIN            |

| tн                     | Clock High Time                                                | 450  |       | 145 |       | 85  |        | 75  |       | ns    | 50% duty cycle, square<br>wave input on XIN         |

| tACC(OP)               | ALE to Valid Data                                              |      | 1340  |     | 490   |     | 340    |     | 300   | ns    | Add t for each WAIT ST                              |

| tACC(MR)               | ALE to Valid Data                                              |      | 1875  |     | 620   |     | 405    |     | 360   | ns    | Add t for each WAIT ST                              |

| t <sub>AFR</sub>       | AD(0-7) Float after<br>RD Falling                              |      | 0     |     | 0     |     | 0      |     | 0     | ns    |                                                     |

| t <sub>BABE</sub>      | BACK Rising to Bus<br>Enable                                   |      | 1000  |     | 400   |     | 300    |     | 250   | ns    |                                                     |

| t <sub>BABF</sub>      | BACK Falling to<br>Bus Float                                   |      | 50    |     | 50    |     | 50     |     | 50    | ns    |                                                     |

| t <sub>BACL</sub>      | BACK Fall to CLK<br>Falling                                    | 425  |       | 125 |       | 60  |        | 55  |       | ns    |                                                     |

| tBRH                   | BREQ Hold Time                                                 | 0    |       | 0   |       | 0   |        | 0   |       | ns    |                                                     |

| t <sub>BRS</sub>       | BREQ Set-Up Time                                               | 100  |       | 50  |       | 50  |        | 45  |       | ns    |                                                     |

| <sup>t</sup> CAF       | Clock Falling ALE<br>Falling                                   | 0    | 70    | 0   | 65    | 0   | 60     | 0   | 55    | ns    |                                                     |

| <sup>t</sup> CAR       | Clock Rising to ALE<br>Rising                                  | 0    | 100   | 0   | 100   | 0   | 90     | 0   | 80    | ns    |                                                     |

| <sup>t</sup> CRD       | Clock Rising to<br>Read Rising                                 |      | 100   |     | 90    |     | 90     |     | 80    | ns    |                                                     |

| <sup>t</sup> CRF       | Clock Rising to<br>Refresh Falling                             |      | 80    |     | 70    |     | 70     |     | 65    | ns    |                                                     |

| t <sub>DAI</sub>       | ALE Falling to INTA<br>Falling                                 | 445  |       | 160 |       | 95  |        | 85  |       | ns    |                                                     |

| tDAR                   | ALE Falling to<br>RD Falling                                   | 400  | 575   | 160 | 250   | 100 | 180    | 90  | 160   | ns    |                                                     |

| tDAW                   | ALE Falling to<br>WR Falling                                   | 900  | 1010  | 350 | 420   | 225 | 300    | 200 | 265   | ns    |                                                     |

| t <sub>D(BACK)</sub> 1 | ALE Falling to BACK<br>Falling                                 | 2460 |       | 975 |       | 635 |        | 560 |       | ns    | Add t for each WAIT sta<br>Add t for opcode fetch o |

| tD(BACK)2              | BREQ Rising to BACK<br>Rising                                  | 500  | 1610  | 200 | 700   | 140 | 540    | 125 | 475   | ns    |                                                     |

| t <sub>D(I)</sub>      | ALE Falling to INTR,<br>NMI, RSTA-C, PS,<br>BREQ, Inputs Valid |      | 1360  |     | 475   |     | 284    |     | 250   | ns    | Add t for each WAIT sta<br>Add t for opcode fetch o |

| t <sub>DPA</sub>       | Rising PS to<br>Falling ALE                                    | 500  | 1685  | 200 | 760   | 140 | 580    | 125 | 510   | ns    | See Figure 14 also                                  |

| <sup>t</sup> D(WAIT)   | ALE Falling to<br>WAIT Input Valid                             |      | 550   |     | 250   |     | 170    |     | 125   | ns    |                                                     |

| Symbol               | Parameter                                           | NSC800-1 |     | NSC800-3 |     | NSC800-35 |     | NSC800-4 |     | Units | Notes                                                                                                |

|----------------------|-----------------------------------------------------|----------|-----|----------|-----|-----------|-----|----------|-----|-------|------------------------------------------------------------------------------------------------------|

| Symbol               |                                                     | Min      | Max | Min      | Max | Min       | Max | Min      | Max | Units | NUICE                                                                                                |

| T <sub>H(ADH)1</sub> | A(8–15) Hold Time During<br>Opcode Fetch            | 0        |     | 0        |     | 0         |     | 0        |     | ns    |                                                                                                      |

| T <sub>H(ADH)2</sub> | A(8–15) Hold Time During<br>Memory or IO, RD and WR | 400      |     | 100      |     | 85        | :   | 60       |     | ns    |                                                                                                      |

| TH(ADL)              | AD(0-7) Hold Time                                   | 100      |     | 60       |     | 35        |     | 30       |     | ns    |                                                                                                      |

| T <sub>H(WD)</sub>   | Write Data Hold Time                                | 400      |     | 100      |     | 85        |     | 75       |     | ns    |                                                                                                      |

| ŧınн                 | Interrupt Hold Time                                 | 0        |     | 0        |     | 0         |     | 0        |     | ns    |                                                                                                      |

| tins                 | Interrupt Set-Up Time                               | 100      |     | 50       |     | 50        |     | 45       |     | ns    |                                                                                                      |

| t <sub>NMI</sub>     | Width of NMI Input                                  | 50       |     | 30       |     | 25        |     | 20       |     | ns    |                                                                                                      |

| t <sub>RDH</sub>     | Data Hold after Read                                | 0        |     | 0        |     | 0         |     | 0        |     | ns    |                                                                                                      |

| t <sub>RFLF</sub>    | RFSH Rising to ALE<br>Falling                       | 60       |     | 50       |     | 45        |     | 40       |     | ns    |                                                                                                      |

| t <sub>RL(MR)</sub>  | RD Rising to ALE Rising (Memory Read)               | 390      |     | 100      |     | 50        |     | 45       |     | ns    |                                                                                                      |

| tS(AD)               | AD(0-7) Set-Up Time                                 | 300      |     | 45       |     | 45        |     | 40       |     | ns    |                                                                                                      |

| <sup>t</sup> S(ALE)  | A(8–15), SO, SI, IO/M<br>Set-Up Time                | 350      |     | 70       |     | 55        |     | 50       |     | ns    |                                                                                                      |

| ts(WD)               | Write Data Set-Up Time                              | 385      |     | 75       |     | 35        |     | 30       |     | ns    |                                                                                                      |

| <sup>t</sup> W(ALE)  | ALE Width                                           | 430      |     | 130      |     | 115       |     | 100      |     | ns    |                                                                                                      |

| twн                  | WAIT Hold Time                                      | 0        |     | 0        |     | 0         |     | 0        |     | ns    |                                                                                                      |

| t <sub>W(I)</sub>    | Width of INTR, RSTA-C,<br>PS, BREQ                  | 500      |     | 200      |     | 140       |     | 125      |     | ns    |                                                                                                      |

| tw(INTA)             | INTA Strobe Width                                   | 1000     |     | 400      |     | 225       |     | 200      |     | ns    | Add two t states for first<br>INTA of each interrupt<br>response string Add t for<br>each WAIT state |

| t <sub>WL</sub>      | WR Rising to ALE Rising                             | 450      |     | 130      |     | 70        |     | 70       |     | ns    |                                                                                                      |

| <sup>t</sup> w(RD)   | Read Strobe Width During<br>Opcode Fetch            | 960      |     | 360      |     | 210       |     | 185      |     | ns    | Add t for each WAIT<br>State Add t/2 for Memory<br>Read Cycles                                       |

| <sup>t</sup> W(RFSH) | Refresh Strobe Width                                | 1925     |     | 725      |     | 450       |     | 395      |     | ns    |                                                                                                      |

| tws                  | WAIT Set-Up Time                                    | 100      |     | 70       |     | 60        |     | 55       |     | ns    |                                                                                                      |

|                      | WAIT Input Width                                    | 550      |     | 250      |     | 195       |     | 175      |     | ns    |                                                                                                      |

| tw(wR)               | Write Strobe Width                                  | 985      |     | 370      |     | 250       |     | 220      |     | ns    | Add t for each WAIT state                                                                            |

| tXCF                 | XIN to Clock Falling                                | 25       | 100 | 15       | 85  | 5         | 90  | 5        | 80  | ns    |                                                                                                      |

| txcR                 | XIN to Clock Rising                                 | 25       | 85  | 15       | 85  | 5         | 90  | 5        | 80  | ns    |                                                                                                      |

Note 1: Test conditions: t = 1000 ns for NSC800-1, 400 ns for NSC800, 285 ns for NSC800-35, 250 ns for NSC800-4.

Note 2: Output timings are measured with a purely capacitive load of 100 pF.

**NSC800**

## 5.0 Timing Waveforms

7-8

This Material Copyrighted By Its Respective Manufacturer

NSC800

## 5.0 Timing Waveforms (Continued)

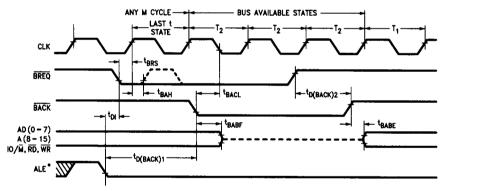

#### Note 1: This t state is the last t state of the last M cycle of any instruction. Note 2: Response to INTR input. Note 3: Response to PS input.

TL/C/5171-6

**NSC800**

\*Waveform not drawn to proportion. Use only for specifying test points.

AC Testing Input/Output Waveform

#### **AC Testing Load Circuit**

TL/C/5171-8

7-9

This Material Copyrighted By Its Respective Manufacturer

## **NSC800 HARDWARE**

## 6.0 Pin Descriptions

#### 6.1 INPUT SIGNALS

**VSC80C**

**Reset Input (RESET IN):** Active low. Sets A (8–15) and AD (0–7) to TRI-STATE® (high impedance). Clears the contents of PC, I and R registers, disables interrupts, and activates reset out.

**Bus Request (BREQ):** Active low. Used when another device requests the system bus. The NSC800 recognizes BREQ at the end of the current machine cycle, and sets A(8-15), AD(0-7), IO/M, RD, and WR to the high impedance state. RFSH is high during a bus request cycle. The CPU acknowledges the bus request via the BACK output signal.

**Non-Maskable Interrupt (NMI):** Active low. The non-maskable interrupt, generated by the peripheral device(s), is the highest priority interrupt. The edge sensitive interrupt requires only a pulse to set an internal flip-flop which generates the internal interrupt request. The NMI flip-flop is monitored on the same clock edge as the other interrupts. It must also meet the minimum set-up time spec for the interrupt to be accepted in the current machine instruction. When the processor accepts the interrupt the flip-flop resets automatically. Interrupt execution is independent of the interrupt enable flip-flop. NMI execution results in saving the PC on the stack and automatic branching to restart address X'0066 in memory.

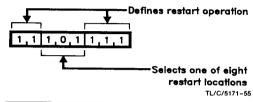

Restart Interrupts, A, B, C (RSTA, RSTB, RSTC): Active low level sensitive. The CPU recognizes restarts generated by the peripherals at the end of the current instruction, if their respective interrupt enable and master enable bits are set. Execution is identical to NMI except the interrupts vector to the following restart addresses:

| Name          | Restart      |

|---------------|--------------|

| Name          | Address (X') |

| NMI           | 0066         |

| RSTA          | 003C         |

| RSTB          | 0034         |

| RSTC          | 002C         |

| INTR (Mode 1) | 0038         |

The order of priority is fixed. The list above starts with the highest priority.

Interrupt Request (INTR): Active low, level sensitive. The CPU recognizes an interrupt request at the end of the current instruction provided that the interrupt enable and master interrupt enable bits are set. INTR is the lowest priority interrupt. Program control selects one of three response modes which determines the method of servicing INTR in conjunction with INTA. See Interrupt Control.

Wait (WAIT): Active low. When set low during RD, WR or INTA machine cycles (during the WR machine cycle, wait must be valid prior to write going active) the CPU extends its machine cycle in increments of t (wait) states. The wait machine cycle continues until the WAIT input returns high.

The wait strobe input will be accepted only during machine cycles that have  $\overline{RD}$ ,  $\overline{WR}$  or INTA strobes and during the machine cycle immediately after an interrupt has been accepted by the CPU. The later cycle has its RD strobe suppressed but it will still accept the wait.

**Power-Save (PS):** Active low. PS is sampled during the last t state of the current instruction cycle. When PS is low, the

CPU stops executing at the end of current instruction and keeps itself in the low-power mode. Normal operation resumes when  $\overline{\text{PS}}$  returns high (see Power Save Feature description).

**CRYSTAL (X<sub>IN</sub>, X<sub>OUT</sub>):** X<sub>IN</sub> can be used as an external clock input. A crystal can be connected across X<sub>IN</sub> and X<sub>OUT</sub> to provide a source for the system clock.

#### 6.2 OUTPUT SIGNALS

Bus Acknowledge (BACK): Active low. BACK indicates to the bus requesting device that the CPU bus and its control signals are in the TRI-STATE mode. The requesting device then commands the bus and its control signals.

Address Bits 8–15 [A(8–15)]: Active high. These are the most significant 8 bits of the memory address during a memory instruction. During an I/O instruction, the port address on the lower 8 address bits gets duplicated onto A(8–15). During a BREQ/BACK cycle, the A(8–15) bus is in the TRI-STATE mode.

Reset Out (RESET OUT): Active high. When RESET OUT is high, it indicates the CPU is being reset. This signal is normally used to reset the peripheral devices.

Input/Output/Memory (IO/ $\overline{M}$ ): An active high on the IO/ $\overline{M}$  output signifies that the current machine cycle is an input/ output cycle. An active low on the IO/ $\overline{M}$  output signifies that the current machine cycle is a memory cycle. It is TRI-STATE during BREQ/BACK cycles.

**Refresh (RFSH):** Active low. The refresh output indicates that the dynamic RAM refresh cycle is in progress. RFSH goes low during T3 and T4 states of all M1 cycles. During the refresh cycle, AD(0-7) has the refresh address and A(8-15) indicates the interrupt vector register data. RFSH is high during BREQ/BACK cycles.

Address Latch Enable (ALE): Active high. ALE is active only during the T1 state of any M cycle and also T3 state of the M1 cycle. The high to low transition of ALE indicates that a valid memory, I/O or refresh address is available on the AD(0-7) lines.

**Read Strobe (RD):** Active low. The CPU receives data via the AD(0-7) lines on the trailing edge of the RD strobe. The RD line is in the TRI-STATE mode during BREQ/BACK cycles.

Write Strobe (WR): Active low. The CPU sends data via the AD(0-7) lines while the WR strobe is low. The WR line is in the TRI-STATE mode during  $\overline{BREQ}/\overline{BACK}$  cycles.

**Clock (CLK):** CLK is the output provided for use as a system clock. The CLK output is a square wave at one half the input frequency.

Interrupt Acknowledge ( $\overline{INTA}$ ): Active low. This signal strobes the interrupt response vector from the interrupting peripheral devices onto the AD(0-7) lines. INTA is active during the M1 cycle immediately following the t state where the CPU recognized the INTR interrupt request.

Two of the three interrupt request modes use INTA. In mode 0 one to four INTA signals strobe a one to four byte instruction onto the AD(0-7) lines. In mode 2 one INTA signal strobes the lower byte of an interrupt response vector onto the bus. In mode 1, INTA is inactive and the CPU response to INTR is the same as for an NMI or restart interrupt.

## 6.0 Pin Descriptions (Continued)

Status (SO, S1): Bus status outputs provide encoded information regarding the current M cycle as follows:

| Machine Cycle        |    | State | Control |    |    |

|----------------------|----|-------|---------|----|----|

|                      | SO | S1    | 10/M    | RD | WR |

| Opcode Fetch         | 1  | 1     | 0       | 0  | 1  |

| Memory Read          | 0  | 1     | 0       | 0  | 1  |

| Memory Write         | 1  | 0     | 0       | 1  | 0  |

| I/O Read             | 0  | 1     | 1       | 0  | 1  |

| I/O Write            | 1  | 0     | 1       | 1  | 0  |

| Halt*                | 0  | 0     | 0       | 0  | 1  |

| Internal Operation*  | 0  | 1     | 0       | 1  | 1  |

| Acknowledge of Int** | 1  | 1     | 0       | 1  | 1  |

\*ALE is not suppressed in this cycle.

\*\*This is the cycle that occurs immediately after the CPU accepts an interrupt (RSTA, RSTB, RSTC, INTR, NMI).

Note 1: During halt, CPU continues to do dummy opcode fetch from location following the halt instruction with a halt status. This is so CPU can continue to do its dynamic RAM refresh.

Note 2: No early status is provided for interrupt or hardware restarts.

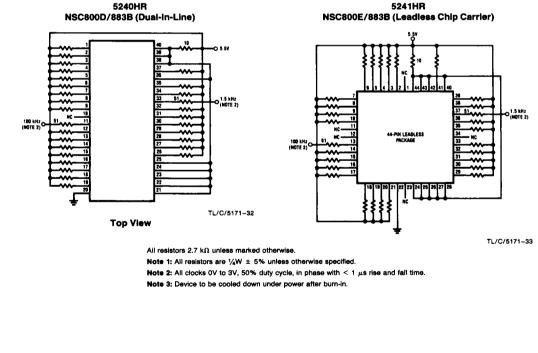

## 7.0 Connection Diagrams

#### 6.3 INPUT/OUTPUT SIGNALS

Multiplexed Address/Data [AD(0-7)]: Active high

| At RD Time:                 | Input data to CPU.                                                            |

|-----------------------------|-------------------------------------------------------------------------------|

| At WR Time:                 | Output data from CPU.                                                         |

| At Falling Edge             | Least significant byte of address                                             |

| of ALE Time:                | during memory reference cycle. 8-bit port address during I/O reference cycle. |

| During BREQ/<br>BACK Cycle: | High impedance.                                                               |

#### **Chip Carrier Package**

7

## 8.0 Functional Description

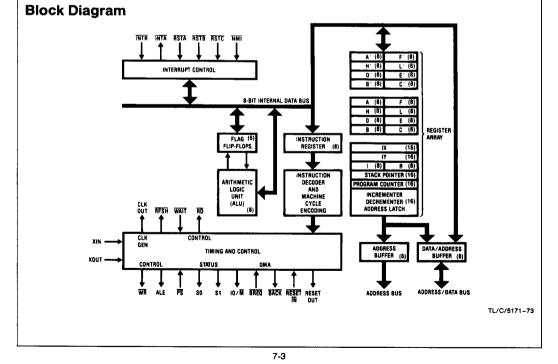

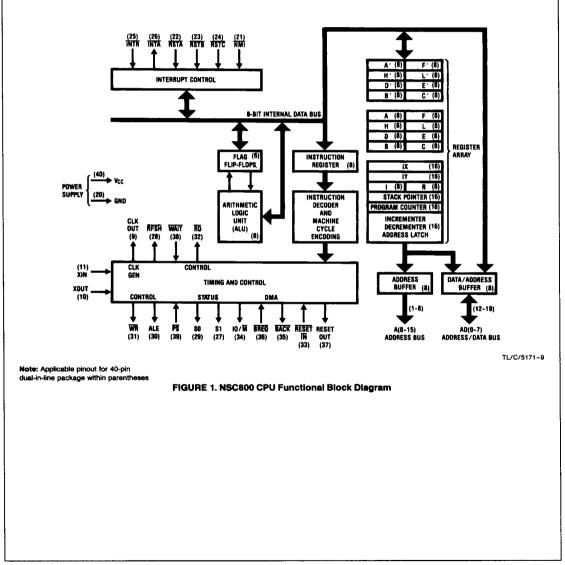

This section reviews the CPU architecture shown below, focusing on the functional aspects from a hardware perspective, including timing details. As illustrated in *Figure 1*, the NSC800 is an 8-bit parallel device. The major functional blocks are: the ALU, register array, interrupt control, timing and control logic. These areas are connected via the 8-bit internal data bus. Detailed descriptions of these blocks ae provided in the following sections.

## 8.0 Functional Description (Continued)

#### 8.1 REGISTER ARRAY

The NSC800 register array is divided into two parts: the dedicated registers and the working registers, as shown in *Figure 2*.

|           | eg. Set | Alternate R      | Set   | Main Reg.   |

|-----------|---------|------------------|-------|-------------|

|           | Flags   | /<br>Accumulator | Flags | Accumulator |

| 1         | F'      | Α'               | F     | Α           |

| Working   | C'      | В'               | С     | В           |

| Registers | E'      | D'               | Е     | D           |

| J         | Ľ.      | H'               | L     | н           |

|           |         |                  |       |             |

#### FIGURE 2. NSC800 Register Array

#### **8.2 DEDICATED REGISTERS**

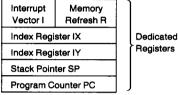

There are 6 dedicated registers in the NSC800: two 8-bit and four 16-bit registers (see *Figure 3*).

Although their contents are under program control, the program has no control over their operational functions, unlike the CPU working registers. The function of each dedicated register is described as follows:

#### **CPU Dedicated Registers**

| Program Counter PC          | (16) |

|-----------------------------|------|

| Stack Pointer SP            | (16) |

| Index Register IX           | (16) |

| Index Register IY           | (16) |

| Interrupt Vector Register I | (8)  |

| Memory Refresh Register R   | (8)  |

#### FIGURE 3. Dedicated Registers

#### 8.2.1 Program Counter (PC)

The program counter contains the 16-bit address of the current instruction being fetched from memory. The PC increments after its contents have been transferred to the address lines. When a program jump occurs, the PC receives the new address which overrides the incrementer.

There are many conditional and unconditional jumps, calls, and return instructions in the NSC800's instruction repertoire that allow easy manipulation of this register in controlling the program execution (i.e. JP NZ nn, JR Zd2, CALL NC, nn).

#### 8.2.2 Stack Pointer (SP)

The 16-bit stack pointer contains the address of the current top of stack that is located in external system RAM. The stack is organized in a last-in, first-out (LIFO) structure. The pointer decrements before data is pushed onto the stack, and increments after data is popped from the stack.

Various operations store or retrieve, data on the stack. This, along with the usage of subroutine calls and interrupts, allows simple implementation of subroutine and interrupt nesting as well as alleviating many problems of data manipulation.

#### 8.2.3 Index Register (IX and IY)

The NSC800 contains two index registers to hold independent, 16-bit base addresses used in the indexed addressing mode. In this mode, an index register, either IX or IY, contains a base address of an area in memory making it a pointer for data tables.

In all instructions employing indexed modes of operation, another byte acts as a signed two's complement displacement. This addressing mode enables easy data table manipulations.

#### 8.2.4 Interrupt Register (I)

When the NSC800 provides a Mode 2 response to INTR, the action taken is an indirect call to the memory location containing the service routine address. The pointer to the address of the service routine is formed by two bytes, the high-byte is from the I Register and the low-byte is from the interrupting peripheral. The peripheral always provides an even address for the lower byte (LSB=0). When the processor receives the lower byte from the peripheral it concatenates it in the following manner:

| l Register | External byte |   |

|------------|---------------|---|

| 8 bits     |               | 0 |

|            |               | 1 |

The LSB of the external byte must be zero.

#### FIGURE 4a. Interrupt Register

The even memory location contains the low-order byte, the next consecutive location contains the high-order byte of the pointer to the beginning address of the interrupt service routine.

#### 8.2.5 Refresh Register (R)

For systems that use dynamic memories rather than static RAM's, the NSC800 provides an integral 8-bit memory refresh counter. The contents of the register are incremented after each opcode fetch and are sent out on the lower portion of the address bus, along with a refresh control signal. This provides a totally transparent refresh cycle and does not slow down CPU operation.

The program can read and write to the R register, although this is usually done only for test purposes.

## 8.0 Functional Description (Continued)

#### 8.3 CPU WORKING AND ALTERNATE REGISTER SETS 8.3.1 CPU Working Registers

The portion of the register array shown in *Figure 4b* represents the CPU working registers. These sixteen 8-bit registers are general-purpose registers because they perform a multitude of functions, depending on the instruction being executed. They are grouped together also due to the types of instructions that use them, particularly alternate set operations.

The F (flag) register is a special-purpose register because its contents are more a result of machine status rather than program data. The F register is included because of its interaction with the A register, and its manipulations in the alternate register set operations.

#### 8.3.2 Alternate Registers

The NSC800 registers designated as CPU working registers have one common feature: the existence of a duplicate register in an alternate register set. This architectural concept simplifies programming during operations such as interrupt response, when the machine status represented by the contents of the registers must be saved.

The alternate register concept makes one set of registers available to the programmer at any given time. Two instructions (EX AF, A'F' and EXX), exchange the current working set of registers with their alternate set. One exchange between the A and F registers and their respective duplicates (A' and F') saves the primary status information contained in the accumulator and the flag register. The second exchange instruction performs the exchange between the remaining registers, B, C, D, E, H, and L, and their respective alternates B', C', D', E', H', and L'. This essentially saves the contents of the original complement of registers while providing the programmer with a usable alternate set.

#### **CPU Main Working Register Set**

| Accumulator A        | (8)     | Flags F     | (8) |

|----------------------|---------|-------------|-----|

| Register B           | (8)     | Register C  | (8) |

| Register D           | (8)     | Register E  | (8) |

| Register H           | (8)     | Register L  | (8) |

| CPU Alternate Workin | g Regis | ter Set     |     |

| Accumulator A'       | (8)     | Flags F'    | (8) |

| Register B'          | (8)     | Register C' | (8) |

| Register D'          | (8)     | Register E' | (8) |

| Register H'          | (8)     | Register L' | (8) |

|                      |         |             |     |

FIGURE 4b. CPU Working and Alternate Registers

## 8.4 REGISTER FUNCTIONS

#### 8.4.1 Accumulator (A Register)

The A register serves as a source or destination register for data manipulation instructions. In addition, it serves as the accumulator for the results of 8-bit arithmetic and logic operations.

The A register also has a special status in some types of operations; that is, certain addressing modes are reserved for the A register only, although the function is available for all the other registers. For example, any register can be loaded by immediate, register indirect, or indexed addressing modes. The A register, however, can also be loaded via an additional register indirect addressing.

Another special feature of the A register is that it produces more efficient memory coding than equivalent instruction functions directed to other registers. Any register can be rotated; however, while it requires a two-byte instruction to normally rotate any register, a single-byte instruction is available for rotating the contents of the accumulator (A register).

#### 8.4.2 F Register - Flags

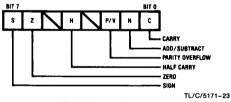

The NSC800 flag register consists of six status bits that contain information regarding the results of previous CPU operations. The register can be read by pushing the contents onto the stack and then reading it, however, it cannot be written to. It is classified as a register because of its affiliation with the accumulator and the existence of a duplicate register for use in exchange instructions with the accumulator.

Of the six flags shown in *Figure 5*, only four can be directly tested by the programmer via conditional jump, call, and return instructions. They are the Sign (S), Zero (Z), Parity/ Overflow (P/V), and Carry (C) flags. The Half Carry (H) and Add/Subtract (N) flags are used for internal operations related to BCD arithmetic.

**FIGURE 5. Flag Register**

# NSC800

## 8.0 Functional Description (Continued)

### 8.4.3 Carry (C)

A carry from the highest order bit of the accumulator during an add instruction, or a borrow generated during a subtraction instruction sets the carry flag. Specific shift and rotate instructions also affect this bit.

Two specific instructions in the NSC800 instruction repertoire set (SCF) or complement (CCF) the carry flag.

Other operations that affect the C flag are as follows:

- Adds ٠

- Subtracts

- Logic Operations (always resets C flag)

- Rotate Accumulator

- Rotate and Shifts

- Decimal Adjust

- Negation of Accumulator

Other operations do not affect the C flag.

#### 8.4.4 Adds/Subtract (N)

This flag is used in conjunction with the H flag to ensure that the proper BCD correction algorithm is used during the decimal adjust instruction (DAA). The correction algorithm depends on whether an add or subtract was previously done with BCD operands.

The operations that set the N flag are:

- Subtractions

- Decrements (8-bit)

- Complementing of the Accumulator

- Block I/O

- Block Searches

- Negation of the Accumulator

The operations that reset the N flag are:

- Adds

- Increments

- Logic Operations

- Rotates

- Set and Complement Carry

- Input Register Indirect

- **Block Transfers**

- Load of the I or R Registers

- Bit Tests

Other operations do not affect the N flag.

#### 8.4.5 Parity/Overflow (P/V)

The Parity/Overflow flag is a dual-purpose flag that indicates results of logic and arithmetic operations. In logic operations, the P/V flag indicates the parity of the result; the flag is set (high) if the result is even, reset (low) if the result is odd. In arithmetic operations, it represents an overflow condition when the result, interpreted as signed two's complement arithmetic, is out of range for the eight-bit accumulator (i.e. - 128 to + 127).

The following operations affect the P/V flag according to the parity of the result of the operation:

- Logic Operations

- Rotate and Shift

- Rotate Digits

- **Decimal Adjust**

- Input Register Indirect

The following operations affect the P/V flag according to the overflow result of the operation.

- Adds (16 bit with carry, 8-bit with/without carry) ٠

- Subtracts (16 bit with carry, 8-bit with/without carry)

- Increments and Decrements

- Negation of Accumulator

The P/V flag has no significance immediately after the following operations.

- Block I/O

- Bit Tests

In block transfers and compares, the P/V flag indicates the status of the BC register, always ending in the reset state after an auto repeat of a block move. Other operations do not affect the P/V flag.

#### 8.4.6 Half Carry (H)

This flag indicates a BCD carry, or borrow, result from the low-order four bits of operation. It can be used to correct the results of a previously packed decimal add, or subtract, operation by use of the Decimal Adjust Instruction (DAA).

The following operations affect the H flag:

- Adds (8-bit) ٠

- Subtracts (8-bit)

- Increments and Decrements

- Decimal Adjust

- Negation of Accumulator

- Always Set by: Logic AND

- Complement Accumulator **Bit Testing**

- Always Reset By: Logic OR's and XOR's **Botates and Shifts**

- Set Carry

- Input Register Indirect

- Block Transfers

- Loads of I and R Registers

The H flag has no significance immediately after the following operations.

- ٠ 16-bit Adds with/without carry

- 16-Bit Subtracts with carry

- Complement of the carry

- Block I/O

- Block Searches

Other operations do not affect the H flag.

## 8.0 Functional Description (Continued)

#### 8.4.7 Zero Flag (Z)

Loading a zero in the accumulator or when a zero results from an operation sets the zero flag.

The following operations affect the zero flag.

- Adds (16-bit with carry, 8-bit with/without carry)

- Subtracts (16-bit with carry, 8-bit with/without carry)

- Logic Operations

- Increments and Decrements

- Rotate and Shifts

- Rotate Digits

- Decimal Adjust

- Input Register Indirect

- Block I/O (always set after auto repeat block I/O)

- Block Searches

- Load of I and R Registers

- Bit Tests

- Negation of Accumulator

The Z flag has no signficance immediately after the following operations:

Block Transfers

Other operations do not affect the zero flag.

#### 8.4.8 Sign Flag (S)

The sign flag stores the state of bit 7 (the most-significant bit and sign bit) of the accumulator following an arithmetic operation. This flag is of use when dealing with signed numbers.

The sign flag is affected by the following operation according to the result:

- · Adds (16-bit with carry, 8-bit with/without carry)

- Subtracts (16-bit with carry, 8-bit with/without carry)

- Logic Operations

- Increments and Decrements

- Rotate and Shifts

- Rotate Digits

- Decimal Adjust

- Input Register Indirect

- Block Search

- Load of I and R Registers

- Negation of Accumulator

The S flag has no significance immediately after the following operations:

- Block I/O

- Block Transfers

- Bit Tests

Other operations do not affect the sign bit.

#### 8.4.9 Additional General-Purpose Registers

The other general-purpose registers are the B, C, D, E, H and L registers and their alternate register set, B', C', D', E', H' and L'. The general-purpose registers can be used interchangeably.

In addition, the B and C registers perform special functions in the NSC800 expanded I/O capabilities, particularly block I/O operations. In these functions, the C register can address I/O ports; the B register provides a counter function when used in the register indirect address mode.

When used with the special condition jump instruction (DJNZ) the B register again provides the counter function.

#### 8.4.10 Alternate Configurations

The six 8-bit general purpose registers (B,C,D,E,H,L) will combine to form three 16-bit registers. This occurs by concatenating the B and C registers to form the BC register, the D and E registers form the DE register, and the H and L registers form the HL register.

Having these 16-bit registers allows 16-bit data handling, thereby expanding the number of 16-bit registers available for memory addressing modes. The HL register typically provides the pointer address for use in register indirect addressing of the memory.

The DE register provides a second memory pointer register for the NSC800's powerful block transfer operations. The BC register also provides an assist to the block transfer operations by acting as a byte-counter for these operations.

#### 8.5 ARITHMETIC-LOGIC UNIT (ALU)

The arithmetic, logic and rotate instructions are performed by the ALU. The ALU internally communicates with the registers and data buffer on the 8-bit internal data bus.

#### 8.6 INSTRUCTION REGISTER AND DECODER

During an opcode fetch, the first byte of an instruction is transferred from the data buffer (i.e. its on the internal data bus) to the instruction register. The instruction register feeds the instruction decoder, which gated by timing signals, generates the control signals that read or write data from or to the registers, control the ALU and provide all required external control signals.

## 9.0 Timing and Control

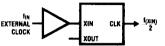

#### 9.1 INTERNAL CLOCK GENERATOR

An inverter oscillator contained on the NSC800 chip provides all necessary timing signals. The chip operation frequency is equal to one half of the frequency of this oscillator.

The oscillator frequency can be controlled by one of the following methods:

1. Leaving the  $X_{OUT}$  pin unterminated and driving the  $X_{IN}$  pin with an externally generated clock as shown in *Figure* 6. When driving  $X_{IN}$  with a square wave, the minimum duty cycle is 30% high.

TL/C/5171-13

#### FIGURE 6. Use of External Clock

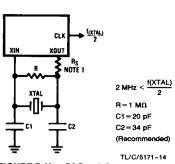

- 2. Connecting a crystal with the proper biasing network between X<sub>IN</sub> and X<sub>OUT</sub> as shown in *Figure 7*. Recommended crystal is a parallel resonance AT cut crystal.

- Note 1: If the crystal frequency is between 1 MHz and 2 MHz a series resistor, R<sub>S</sub>, (4701 to 15001) should be connected between X<sub>OUT</sub> and R, XTAL and C<sub>Z</sub>. Additionally, the capacitance of C1 and C2 should be increased by 2 to 3 times the recommended value. For crystal frequencies less than 1 MHz higher values of C1 and C2 may be required. Crystal parameters will also affect the capacitive loading requirements.

NSC800

#### FIGURE 7. Use Of Crystal

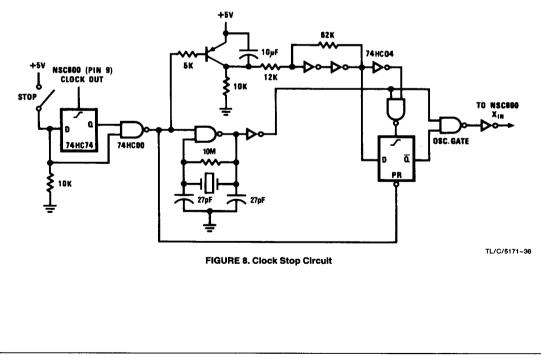

The CPU has a minimum clock frequency input (@  $X_{IN}$ ) of 300 kHz, which results in 150 kHz system clock speed. All registers internal to the chip are static, however there is dynamic logic which limits the minimum clock speed. The input clock can be stopped without fear of losing any data or damaging the part. You stop it in the phase of the clock that has  $X_{IN}$  low and CLK OUT high. When restarting the CPU, precautions must be taken so that the input clock meets these minimum specification. Once started, the CPU will continue operation from the same location at which it was stopped. During DC operation of the CPU, typical current drain will be 2 mA. This current drain can be reduced by placing the CPU in a wait state during an opcode fetch cycle then stopping the clock. For clock stop circuit, see *Figure 8*.

### 9.2 CPU TIMING

The NSC800 uses a multiplexed bus for data and addresses. The 16-bit address bus is divided into a high-order 8-bit address bus that handles bits 8–15 of the address, and a low-order 8-bit multiplexed address/data bus that handles bits 0–7 of the address and bits 0–7 of the data. Strobe outputs from the NSC800 (ALE, RD and WR) indicate when a valid address or data is present on the bus.  $IO/\overline{M}$  indicates whether the ensuing cycle accesses memory or I/O.

During an input or output instruction, the CPU duplicates the lower half of the address [AD(0-7)] onto the upper address bus [A(8-15)]. The eight bits of address will stay on A(8-15) for the entire machine cycle and can be used for chip selection directly.

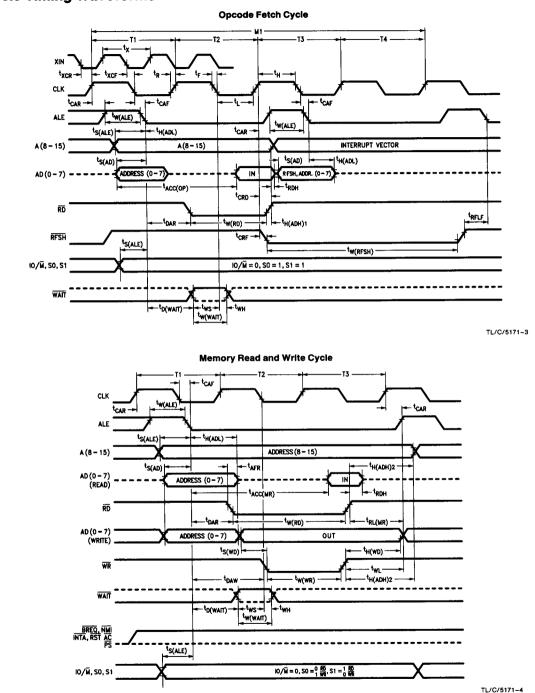

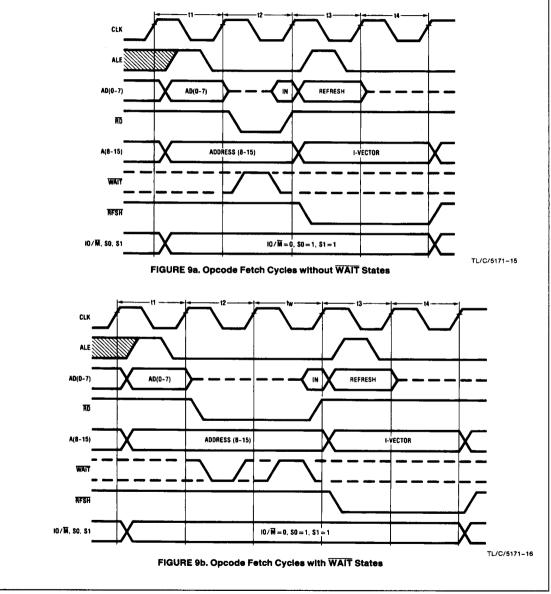

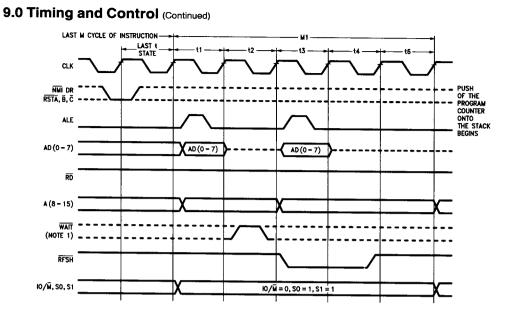

Figure 9 illustrates the timing relationship for opcode fetch cycles with and without a wait state.

During the opcode fetch, the CPU places the contents of the PC on the address bus. The falling edge of ALE indicates a valid address on the AD(0-7) lines. The WAIT input is sampled during  $t_2$  and if active causes the NSC800 to insert a wait state ( $t_w$ ). WAIT is sampled again during  $t_w$  so

that when it goes inactive, the CPU continues its opcode fetch by latching in the data on the rising edge of RD from the AD(0-7) lines. During  $t_3$ , RFSH goes active and AD(0-7) has the dynamic RAM refresh address from register R and A(8-15) the interrupt vector from register I.

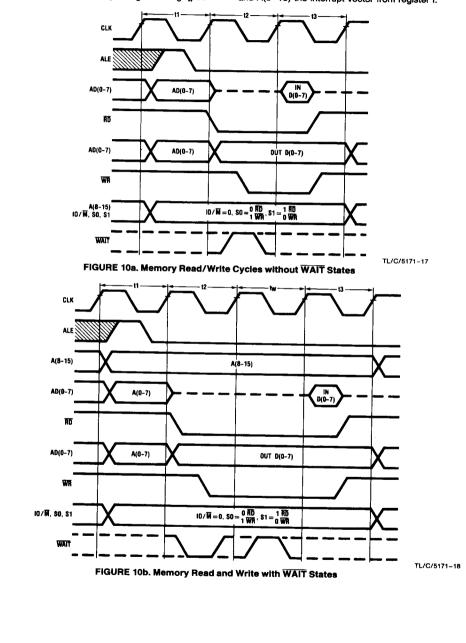

Figure 10 shows the timing for memory read (other than opcode fetchs) and write cycles with and without a wait

state. The  $\overline{RD}$  stobe is widened by  $\frac{\tau}{2}$  (half the machine state) for memory reads so that the actual latching of the input data occurs later.

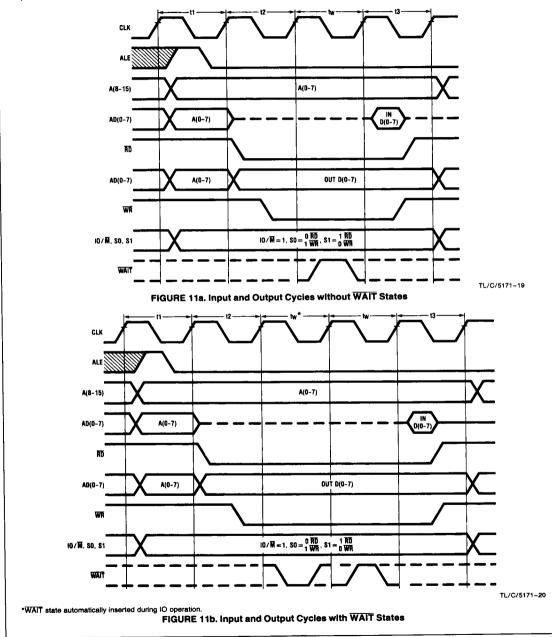

Figure 11 shows the timing for input and output cycles with and without wait states. The CPU automatically inserts one wait state into each I/O instruction to allow sufficient time for an I/O port to decode the address.

#### 9.3 INITIALIZATION

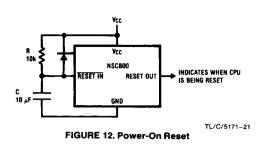

RESET IN initializes the NSC800; RESET OUT initializes the peripheral components. The Schmitt trigger at the RESET IN input facilitates using an R-C network reset scheme during power up (see *Figure 12*).

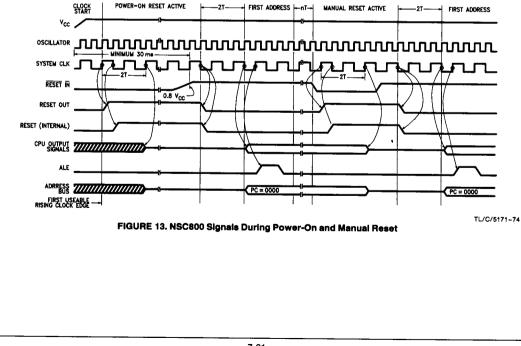

To ensure proper power-up conditions for the NSC800, the following power-up and initialization procedure is recommended:

- Apply power (V<sub>CC</sub> and GND) and set RESET IN active (low). Allow sufficient time (approximately 30 ms if a crystal is used) for the oscillator and internal clocks to stabilize. RESET IN must remain low for at least 3t state (CLK) times. RESET OUT goes high as soon as the active RESET IN signal is clocked into the first flip-flop after the on-chip Schmitt trigger. RESET OUT signal is available to reset the peripherals.

- Set <u>RESET IN</u> high. RESET OUT then goes low as the inactive <u>RESET IN</u> signal is clocked into the first flip-flop after the on-chip Schmitt trigger. Following this the CPU initiates the first opcode fetch cycle.

Note: The NSC800 initialization includes: Clear PC to X'0000 (the first opcode fetch, therefore, is from memory location X'0000). Clear registers I (Interrupt Vector Base) and R (Refresh Counter) to X'00. Clear interrupt control register bits IEA, IEB and IEC. The interrupt control bit IEI is set to 1 to maintain INS8080A/Z80A compatibility (see INTER-RUPTS for more details). The CPU disables maskable interrupts and enters INTR Mode 0. While RESET IN is active (low), the A(8–15) and AD(0–7) lines go to high impedance (TRI-STATE) and all CPU strobes go to the inactive state (see Figure 13).

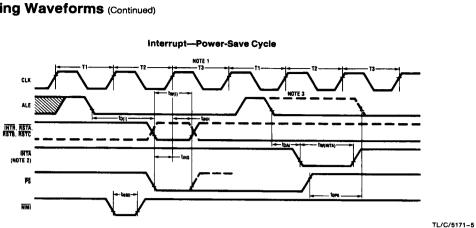

#### 9.4 POWER-SAVE FEATURE

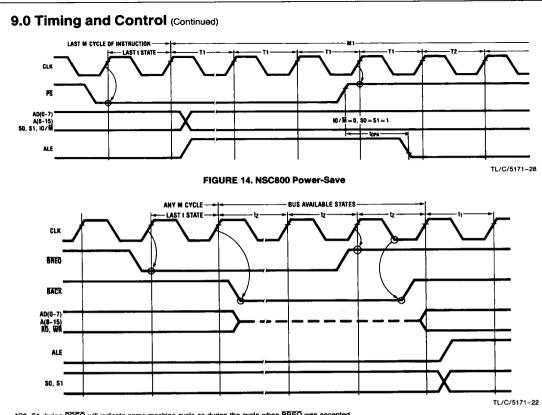

The NSC800 provides a unique power-save mode by the means of the PS pin. PS input is sampled at the last t state of the last M cycle of an instruction. After recognizing an active (low) level on PS, The NSC800 stops its internal clocks, thereby reducing its power dissipation to one half of operating power, yet maintaining all register values and internal control status. The NSC800 keeps its oscillator running, and makes the CLK signal available to the system. When in power-save the ALE strobe will be stopped high and the address lines [AD(0-7), A(8-15)] will indicate the next machine address. When PS returns high, the opcode fetch (or M1 cycle) of the CPU begins in a normal manner. Note this M1 cycle could also be an interrupt acknowledge cycle if the NSC800 was interrupted simultaneously with PS (i.e. PS has priority over a simultaneously occurring interrupt). However, interrupts are not accepted during power save. Figure 14 illustrates the power save timing.

**NSC800**

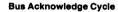

\*S0, S1 during BREQ will indicate same machine cycle as during the cycle when BREQ was accepted.  $t_{Z}$  = time states during which bus and control signals are in high impedance mode.

#### FIGURE 15. Bus Acknowledge Cycle

In the event BREQ is asserted (low) at the end of an instruction cycle and PS is active simultaneously, the following occurs:

1. The NSC800 will go into BACK cycle.

2. Upon completion of BACK cycle if PS is still active the CPU will go into power-save mode.

#### 9.5 BUS ACCESS CONTROL

**NSC800**

Figure 15 illustrates bus access control in the NSC800. The external device controller produces an active BREQ signal that requests the bus. When the CPU responds with BACK then the bus and related control strobes go to high impedance (TRI-STATE) and the RFSH signal remains high. It should be noted that (1) BREQ is sampled at the last t state of any M machine cycle only. (2) The NSC800 will not acknowledge any interrupt/restart requests, and will not peform any dynamic RAM refresh functions until after BREQ input signal is inactive high. (3) BREQ signal has priority over all interrupt request signals, should BREQ and interrupt request become active simultaneously. Therefore, interrupts latched at the end of the instruction cycle will be serviced after a simultaneously occurring BREQ. NMI is latched during an active BREQ.

#### 9.6 INTERRUPT CONTROL

The NSC800 has five interrupt/restart inputs, four are maskable (RSTA, RSTB, RSTC, and INTR) and one is non-maskable (NMI). NMI has the highest priority of all interrupts; the user cannot disable NMI. After recognizing an active input on NMI, the CPU stops before the next instruction, pushes the PC onto the stack, and jumps to address X'0066, where the user's interrupt service routine is located (i.e., restart to memory location X'0066). NMI is intended for interrupts requiring immediate attention, such as power-down, control panel, etc.

RSTA, RSTB and RSTC are restart inputs, which, if enabled, execute a restart to memory location X'003C, X'0034, and X'002C, respectively. Note that the CPU response to the NMI and RST ( $\overline{A}$ ,  $\overline{B}$ ,  $\overline{C}$ ) request input is basically identical, except for the restored memory location. Unlike NMI, however, restart request inputs must be enabled.

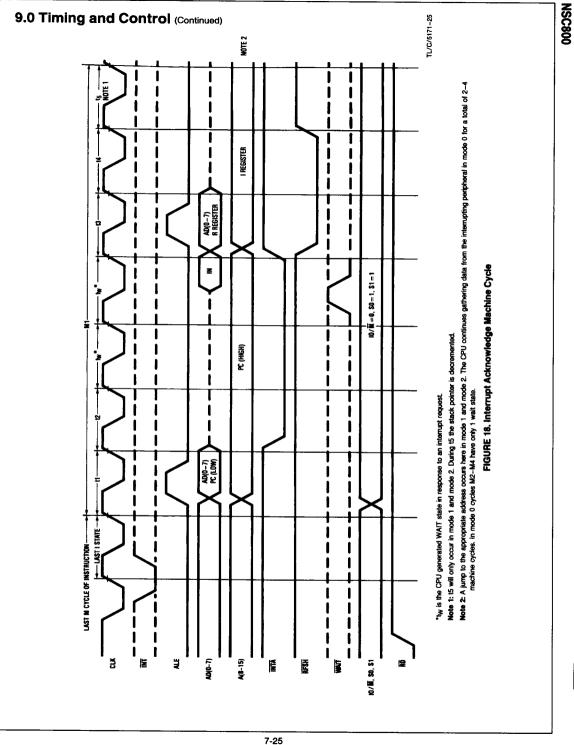

Figure 16 illustrates  $\overline{\text{NM}}$  and  $\overline{\text{RST}}$  interrupt machine cycles. M1 cycle will be a dummy opcode fetch cycle followed by M2 and M3 which are stack push operations. The following instruction then starts from the interrupts restart location.

Note: RD does not go low during this durmmy opcode fetch. A unique indication of INTA can be decoded using 2 ALEs and RD.

TL/C/5171-24

**NSC800**

Note 1: This is the only machine cycle that does not have an RD, WR, or INTA strobe but will accept a wait strobe.

### FIGURE 16. Non-Maskable and Restart Interrupt Machine Cycle

The NSC800 also provides one more general purpose interrupt request input, INTR. When enabled, the CPU responds to INTR in one of the three modes defined by instruction IMO, IM1, and IM2 for modes 0, 1, and 2, respectively. Following reset, the CPU automatically enables mode 0.

Interrupt (INTR) Mode 0: The CPU responds to an interrupt request by providing an INTA (interrupt acknowledge) strobe, which can be used to gate an instruction from a peripheral onto the data bus. The CPU inserts two wait states during the first INTA cycle to allow the interrupting device (or its controller) ample time to gate the instruction and determine external priorities (*Figure 18*). This can be any instruction from one to four bytes. The most popular instruction is one-byte call (restart instruction) or a threebyte call (CALL NN instruction). If it is a three-byte call, the CPU issues a total of three INTA strobes. The last two (which do not include wait states) read NN.

Note: If the instruction stored in the ICU doesn't require the PC to be pushed onto the stack (eq. JP nn), then the PC will not be pushed.

Interrupt (INTR) Mode 1: Similar to restart interrupts except the restart location is X'0038 (Figure 18).

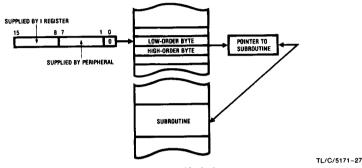

**Interrupt (INTR) Mode 2:** With this mode, the programmer maintains a table that contains the 16-bit starting address of every interrupt service routine. This table can be located anywhere in memory. When the CPU accepts a Mode 2 interrupt (*Figure 17*), it forms a 16-bit pointer to obtain the desired interrupt service routine starting address from the table. The upper 8 bits of this pointer are from the contents of the I register. The lower 8 bits of the pointer are supplied by the interrupting device with the LSB forced to zero. The programmer must load the interrupt vector prior to the interrupt occurring. The CPU uses the pointer starting address the wo adjacent bytes from the interrupt service routine starting address table to complete 16-bit service rout

dress. The first byte of each entry in the table is the least significant (low-order) portion of the address. The programmer must obviously fill this table with the desired addresses before any interrupts are to be accepted.

Note that the programmer can change this table at any time to allow peripherals to be serviced by different service routines. Once the interrupting device supplies the lower portion of the pointer, the CPU automatically pushes the program counter onto the stack, obtains the starting address from the table and does a jump to this address.

The interrupts have fixed priorities built into the NSC800 as:

| NMI  | 0066 | (Highest Priority) |

|------|------|--------------------|

| RSTA | 003C |                    |

| RSTB | 0034 |                    |

| RSTC | 002C |                    |

| INTR | 0038 | (Lowest Priority)  |

|      |      |                    |

Interrupt Enable, Interrupt Disable. The NSC800 has two types of interrupt inputs, a non-maskable interrupt and four software maskable interrupts. The non-maskable interrupt (NMI) cannot be disabled by the programmer and will be accepted whenever a peripheral device requests an interrupt. The NMI is usually reserved for important functions that must be serviced when they occur, such as imminent power failure. The programmer can selectively enable or disable maskable interrupts (INT, RSTA, RSTB and RSTC). This selectivity allows the programmer to disable the maskable interrupts during periods when timing constraints don't allow program interruption.

There are two interrupt enable flip-flops (IFF<sub>1</sub> and IFF<sub>2</sub>) on the NSC800. Two instructions control these flip-flops. Enable Interrupt (EI) and Disable Interrupt (DI). The state of IFF<sub>1</sub> determines the enabling or disabling of the maskable interrupts, while IFF<sub>2</sub> is used as a temporary storage location for the state of IFF<sub>1</sub>.

# **NSC800**

## 9.0 Timing and Control (Continued)

A reset to the CPU will force both IFF<sub>1</sub> and IFF<sub>2</sub> to the reset state disabling maskable interrupts. They can be enabled by an El instruction at any time by the programmer. When an El instruction is executed, any pending interrupt requests will not be accepted until after the instruction following El has been executed. This single instruction delay is necessary in situations where the following instruction is a return instruction and interrupts must not be allowed until ther further for the situations of the entrum the situations of the entrum the set of the situation of the entrum the situation of the entrum the situations of the entrum the situations of the entrum the situation of the entrum thent the e

to the enable state. When the CPU accepts an interrupt, both IFF<sub>1</sub> and IFF<sub>2</sub> are automatically reset, inhibiting further interrupts until the programmer wishes to issue a new EI instruction. Note that for all the previous cases, IFF<sub>1</sub> and IFF<sub>2</sub> are always equal.

The function of IFF<sub>2</sub> is to retain the status of IFF<sub>1</sub> when a non-maskable interrupt occurs. When a non-maskable interrupt is accepted, IFF<sub>1</sub> is reset to prevent further interrupts until reenabled by the programmer. Thus, after a non-maskable interrupt has been accepted, maskable interrupts are disabled but the previous state of IFF<sub>1</sub> is saved by IFF<sub>2</sub>

FIGURE 17. Interrupt Mode 2

This Material Copyrighted By Its Respective Manufacturer

so that the complete state of the CPU just prior to the nonmaskable interrupt may be restored. The method of restoring the status of IFF<sub>1</sub> is through the execution of a Return Non-Maskable Interrupt (RETN) instruction. Since this instruction indicates that the non-maskable interrupt service routine is completed, the contents of IFF<sub>2</sub> are now copied back into IFF<sub>1</sub>, so that the status of IFF<sub>1</sub> just prior to the acceptance of the non-maskable interrupt will be automatically restored.

Figure 19 depicts the status of the flip flops during a sample series of interrupt instructions.

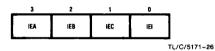

Interrupt Control Register. The interrupt control register (ICR) is a 4-bit, write only register that provides the programmer with a second level of maskable control over the four maskable interrupt inputs.

The ICR is internal to the NSC800 CPU, but is addressed through the I/O space at I/O address port X'BB. Each bit in the register controls a mask bit dedicated to each maskable interrupt, RSTA, RSTB, RSTC and INTR. For an interrupt request to be accepted on any of these inputs, the corresponding mask bit in the ICR must be set (= 1) and IFF<sub>1</sub> and IFF<sub>2</sub> must be set. This provides the programmer with control over individual interrupt inputs rather than just a system wide enable or disable.

|     |      | TL/C/5171-                |

|-----|------|---------------------------|

| Bit | Name | Function                  |

| 0   | 1EI  | Interrupt Enable for INTR |

| 1   | IEC  | Interrupt Enable for RSTC |

| 2   | IEB  | Interrupt Enable for RSTB |

| 3   | IEA  | Interrupt Enable for RSTA |

For example: In order to enable  $\overrightarrow{\text{RSTB}}$ , CPU interrupts must be enabled and IEB must be set.

At reset, IEI bit is set and other mask bits IEA, IEB, IEC are cleared. This maintains the software compatibility between NSC800 and Z80A.

Execution of an I/O block move instruction will not affect the state of the interrupt control bits. The only two instructions that will modify this write only register are OUT (C), r and OUT (N), A.

| Operation  | IFF <sub>1</sub> | IFF <sub>2</sub> | Comment                     |

|------------|------------------|------------------|-----------------------------|

| Initialize | 0                | 0                | Interrupt Disabled          |

| •          |                  |                  |                             |

| •          |                  |                  |                             |

| El         | 1                | 1                | Interrupt Enabled after     |

| ٠          |                  |                  | next instruction            |

| •          |                  |                  |                             |

| •          | _                |                  |                             |

| INTR       | 0                | 0                | Interrupt Disable and INTR  |

| •          |                  |                  | Being Serviced              |

| •          |                  |                  |                             |

| •          |                  |                  |                             |

| EI         | 1                | 1                | Interrupt Enabled after     |

|            |                  |                  | next instruction            |

| RET        | 1                | 1                | Interrupt Enabled           |

| •          |                  |                  |                             |

| •          |                  |                  |                             |

| •<br>NMI   | 0                | 1                | Interrupt Disabled          |

| •          | v                |                  | interrupt bisablog          |

| •          |                  |                  |                             |

| •          |                  |                  |                             |

| RETN       | 1                | 1                | Interrupt Enabled           |

| •          |                  |                  |                             |

| INTR       | 0                | 0                | Interrupt Disabled          |

| •          |                  |                  |                             |

|            |                  |                  |                             |

| NMI        | 0                | 0                | Interrupt Disabled and NMI  |

| •          | -                | -                | Being Serviced              |

| •          |                  |                  | -                           |

| •          |                  |                  |                             |

| RETN       | 0                | 0                | Interrupt Disabled and INTR |

| •          |                  |                  | Being Serviced              |

| •          |                  |                  |                             |

| EI         | 1                | 1                | Interrupt Enabled after     |

| <u> </u>   | •                | •                | next instruction            |

| RET        | 1                | 1                | Interrupt Enabled           |

| •          |                  |                  |                             |

| •          |                  |                  |                             |

| •          |                  |                  |                             |

FIGURE 19. IFF<sub>1</sub> and IFF<sub>2</sub> States Immediately after the Operation has been Completed

## **NSC800 SOFTWARE**

## **10.0 Introduction**

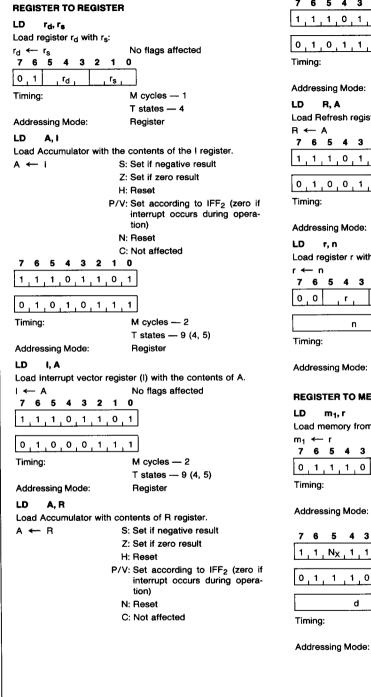

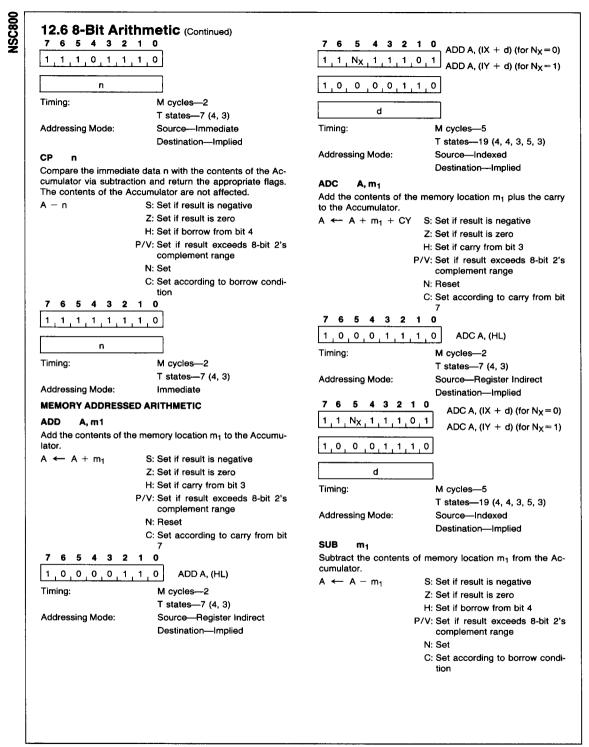

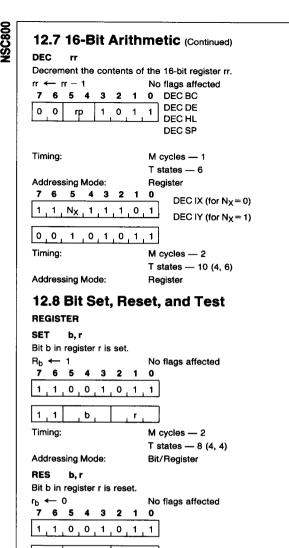

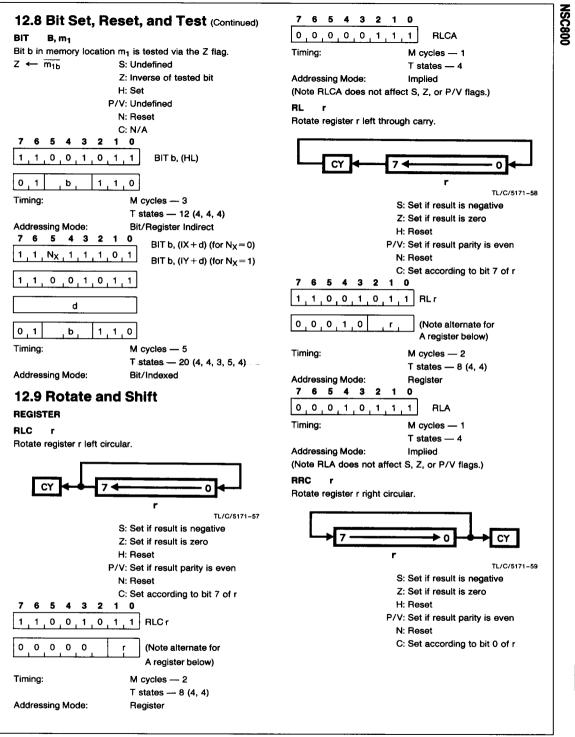

This chapter provides the reader with a detailed description of the NSC800 software. Each NSC800 instruction is described in terms of opcode, function, flags affected, timing, and addressing mode.

## **11.0 Addressing Modes**

The following sections describe the addressing modes supported by the NSC800. Note that particular addressing modes are often restricted to certain types of instructions. Examples of instructions used in the particular addressing modes follow each mode description.

The 10 addressing modes and 158 instructions provide a flexible and powerful instruction set.

#### 11.1 REGISTER

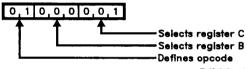

The most basic addressing mode is that which addresses data in the various CPU registers. In these cases, bits in the opcode select specific registers that are to be addressed by the instruction.

#### Example:

Instruction: Load register B from register C

Mnemonic: LD B,C

Opcode:

TL/C/5171-50

In this instruction, both the B and C registers are addressed by opcode bits.

#### 11.2 IMPLIED

The implied addressing mode is an extension to the register addressing mode. In this mode, a specific register, the accumulator, is used in the execution of the instruction. In particular, arithmetic operations employ implied addressing, since the A register is assumed to be the destination register for the result without being specifically referenced in the opcode.

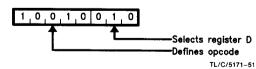

#### Example:

Instruction: Subtract the contents of register D from the Accumulator (A register)

Mnemonic: SUB D Opcode:

In this instruction, the D register is addressed with register addressing, while the use of the A register is implied by the opcode.

#### 11.3 IMMEDIATE

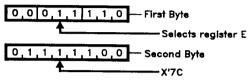

The most straightforward way of introducing data to the CPU registers is via immediate addressing, where the data is contained in an additional byte of multi-byte instructions. Example:

Instruction: Load the E register with the constant value X'7C.

Mnemonic: LD E,X'7C Opcode:

TL/C/5171-52

In this instruction, the E register is addressed with register addressing, while the constant X'7C is immediate data in the second byte of the instruction.

#### **11.4 IMMEDIATE EXTENDED**

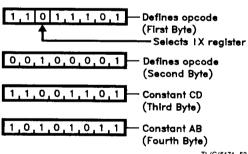

As immediate addressing allows 8 bits of data to be supplied by the operand, immediate extended addressing allows 16 bits of data to be supplied by the operand. These are in two additional bytes of the instruction.

#### Example:

Instruction: Load the 16-bit IX register with the constant value X'ABCD.

| Mnemonic: LD | IX,X'ABCD |

|--------------|-----------|

| Opcode:      |           |

TL/C/5171-53

In this instruction, register addressing selects the IX register, while the 16-bit quanity X'ABCD is immediate data supplied as immediate extended format.

# NSC800

### 11.0 Addressing Modes (Continued)

#### 11.5 DIRECT ADDRESSING

Direct addressing is the most straightforward way of addressing supplies a location in the memory space. Direct addressing, 16-bits of memory address information in two bytes of data as part of the instruction. The memory address could be either data, source of destination, or a location for program execution, as in program control instructions. Example:

Instruction: Jump to location X'0377

Mnemonic: JP X'0377

#### Opcode:

| —Defines jump opcode |

|----------------------|

| O                    |

| -Constant X'0377     |

|                      |

|                      |

This instruction loads the Program Counter (PC) is loaded with the constant in the second and third bytes of the instruction. The program counter contents are transferred via direct addressing.

#### **11.6 REGISTER INDIRECT**

Next to direct addressing, register indirect addressing provides the second most straightforward means of addressing memory. In register indirect addressing, a specified register pair contains the address of the desired memory location. The instruction references the register pair and the register contents define the memory location of the operand.

#### Example:

Instruction: Add the contents of memory location X'0254 to the A register. The HL register contains X'0254.

A,(HL)

Mnemonic: ADD

Opcode

This instruction uses implied addressing of the A and HL registers and register indirect addressing to access the data pointed to by the HL register.

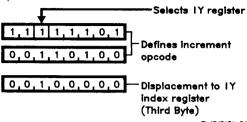

#### 11.7 INDEXED

The most flexible mode of memory addressing is the indexed mode. This is similar to the register indirect mode of addressing because one of the two index registers (IX or IY) contains the base memory address. In addition, a byte of data included in the instruction acts as a displacement to the address in the index register. Indexed addressing is particularly useful in dealing with lists of data.

Example:

Opcode:

Instruction: Increment the data in memory location X'1020. The IY register contains X'1000.

Mnemonic: INC

: INC (IY + X'20)

TL/C/5171-54

The indexed addressing mode uses the contents of index registers IX or IY along with the displacement to form a pointer to memory.

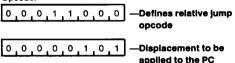

#### 11.8 RELATIVE

Certain instructions allow memory locations to be addressed as a position relative to the PC register. These instructions allow jumps to memory locations which are offsets around the program counter. The offset, together with the current program location, is determined through a displacement byte included in the instruction. The formation of this displacement byte is explained more fully in the "Instructions Set" section.

Example:

Instruction: Jump to a memory location 7 bytes beyond the current location.

Mnemonic: JR \$+7

Opcode: