## **Data Sheet**

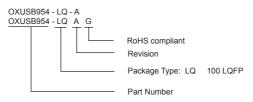

## OXUSB954 USB to Quad Serial Port Bridge

## **Features**

- USB 2.0 compatible at full speed; built-in 12-Mbps transceiver & SIE

- Backward-compatible with USB 1.1

- USB suspend/resume

- Serial port—high-speed transfers at up to 230 Kbps

- Additional UART for debug & code development

- Advanced 16-bit processor for USB transaction processing & control data processing

- 1.5 K×16 internal RAM buffer for fast communications

- 128-byte receive & transmit FIFO

- Configurable line control allows 8-bit words as well as 5, 6 & 7

- Optional odd, even or no parity & 1 or 2 stop bits

- Serial 2-wire interface to support EEPROM configuration

- Watchdog timer

- Utilizes low-cost external crystal circuitry

- Plug & play compatible

- USB host device drivers available (Windows<sup>®</sup> 98, Windows 2000, Windows XP)

- 3.3-V operation

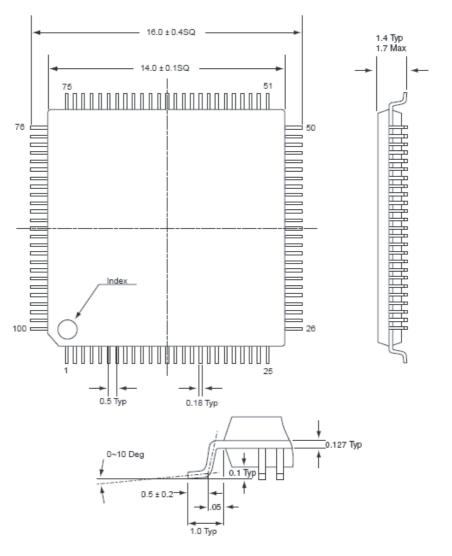

- 100-pin LQFP

## **Overview**

The Oxford Semiconductor OXUSB954 USB-to-quad serial port is the ideal bridge between USB port and up to four serial port peripherals. This intelligent device complies with USB2.0 at full speed, as well as standard serial port specifications. It delivers the advantages of USB, such as high-speed data transfers and plug-and-play capabilities, to peripherals with a serial port interface, making it ideal for connections to high-speed modems or ISDN terminal adapters. The combination of device and software renders the interface transparent to peripherals and requires no firmware changes, making it possible for serial peripherals to interface with USB with minimum modification. This feature is ideal for legacy applications.

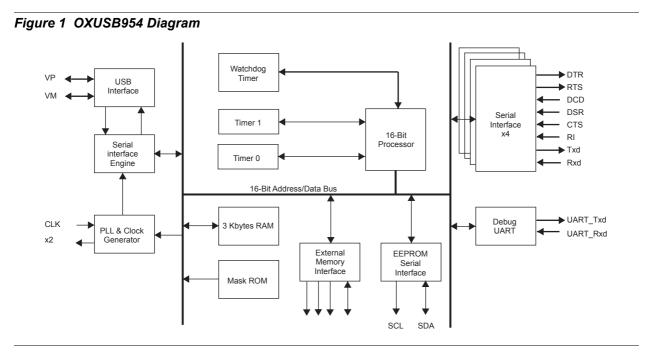

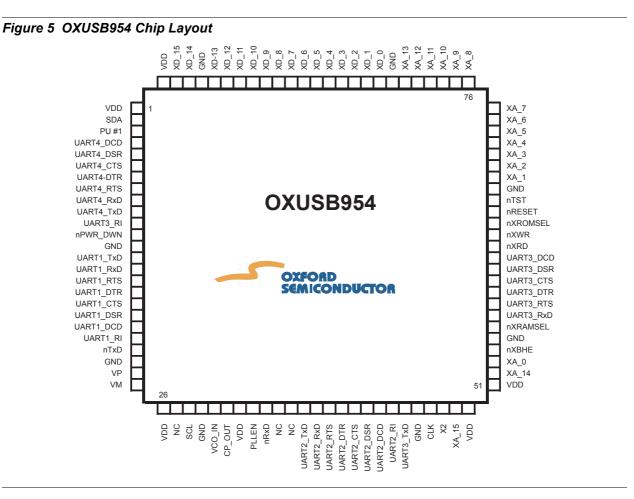

### Figure 1 shows the Oxford Semiconductor OXUSB954.

# Functionality

The OXUSB954 integrated 16-bit processor has direct access to the RAM buffer, external memory, I/O interfaces, and all control and status registers. It runs at up to 5 MIPs. It serves as a micro-controller for USB peripherals, offering additional processing power that allows the design of intelligent peripherals that can process data prior to passing it to the host PC. This type of task optimization enhances system efficiency and improves overall performance, while the masked ROM instruction set promotes efficient code for algorithm and USB transaction processing. The processor supports up to 240 software interrupt vectors.

The processor provides the following address modes:

- Memory-to-memory

- Memory-to register

- Register-to-register

- Immediate-to-register

- Immediate-to-memory

Register, direct, immediate, indirect and indirect-indexed addressing modes are supported, plus an additional auto-increment mode, in which a register used as an address pointer is automatically incremented after each use, making repetitive operations more efficient. The processor features program control, logical and integer arithmetic instructions. All instructions are sixteen bits wide, although some instructions require operands, which may occupy another one or two words. Several short immediate instructions are available, allowing operations with small constant operands to fit into a 16-bit instruction.

The processor divide/multiply function contains all the instructions of the base processor with additional integer divide and multiply instructions. A signed multiply instruction takes two 16-bit operands and returns a 32-bit result. A signed divide instruction divides a 32-bit operand by a 16-bit operand.

## **Programmable Timers**

There are two built-in programmable timers that generate interrupts. Both timers decrement on every micro-second clock tick and generate an interrupt when the timer reaches zero. Similarly, a separate watchdog timer, that can also generate an interrupt on the OXUSB954, is also provided.

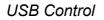

## USB

Internal buffer memory in the USB controller is used to buffer data and USB packets. The memory is accessed by the 16-bit processor and the serial interface engine (SIE).

USB transactions are automatically routed to the memory buffer, using pointers and block sizes set up by the processor, which reads data from the interface, processes and packetizes it. If there is no activity on the USB for 3 ms, the USB enters a suspend state.

The USB controller transceiver with its differential driver can transmit and receive serial data at full speed (12 Mbps). While the transceiver driver is differential, the receiver section comprises a differential receiver and two single-ended receivers. Internally, the transceiver interfaces to the SIE; externally it connects to the USB PHY. The USB controller serial interface provides access to external EEPROMs and can support a variety of serial EEPROM formats.

Communication and data flow on the USB is implemented using uniquely-identifiable endpoints, which are the terminals of communication flow between a USB host and USB devices. The OXUSB954 supports 10 endpoints, numbered 0 to 9.

## **Serial Ports**

The four UART serial ports can be individually configured for rates from 300 to 230.4 K baud, providing USB access to external serial devices.

An additional independent UART serial port is provided for code development and debugging, supporting transmit and receive data at rates from 7200 to 115.2 K baud. The UART timers are independent of the general-purpose timers.

When the receiver buffer transitions to full or the transmit buffer transitions to empty, a UART interrupt is generated.

## Clocks

In the OXUSB954, PLL circuitry generates the internal 48-MHz clock, which is connected to CLK and X2. The circuitry is designed to allow the use of a low-cost 12-MHz crystal oscillator, supplied internally or from an application source connected directly to the CLK input pin. If the PLL is disabled, a 48-MHz crystal or clock can be used.

## **EEPROM Support**

The OXUSB954 interfaces with a serial EEPROM device to program the OXUSB954.

An EEPROM is required for the correct functionality of the OXUSB954

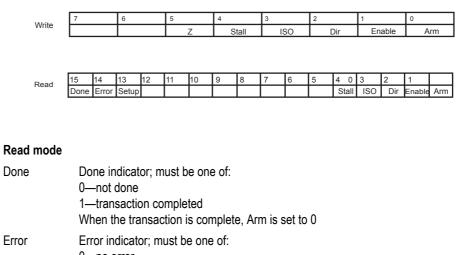

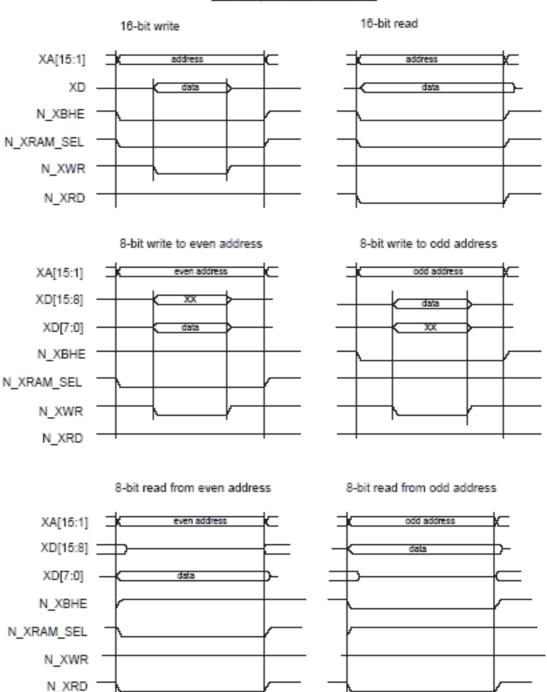

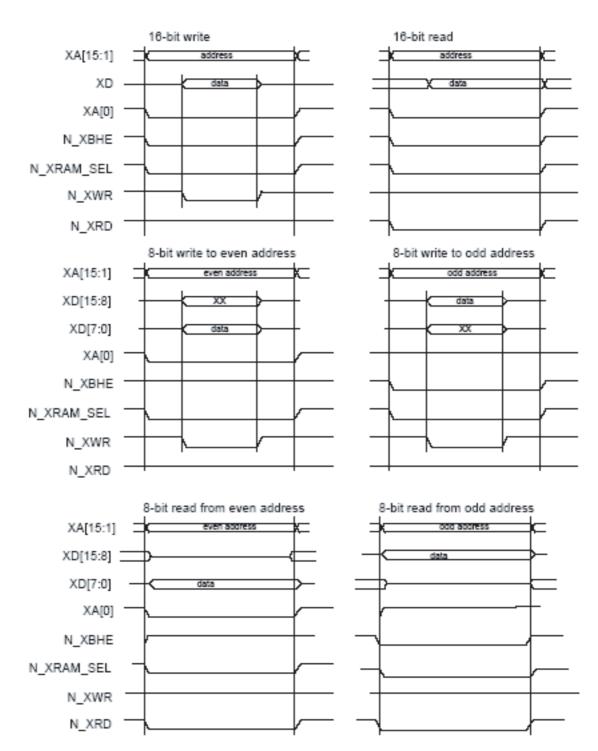

## **External Memory**

The 16-bit memory interface on the OXUSB954 can support a variety of external RAM and ROM. Each external memory space can be 8 or 16 bits wide, and can be programmed for up to seven wait states. The byte-addressable memory address range is divided into two banks that can each be assigned to internal or external ROM under register control.

External memory is required for the correct functionality of the OXUSB954.

## Registers

This section documents the registers used to configure, use, and obtain status information about, the OXUSB954. Register locations and reset values are given for each register. Other locations in the register address space are reserved.

## **Processor Control**

The processor control registers in the OXUSB954 configure the device to operate at different clock frequencies and select a power-saving mode that is used to suspend USB operation. In addition, the version control register located in the ROM BIOS can be read to discover the firmware version. Table 1 lists the processor control registers

| Table 1 Processor Control Registers |         |                  |  |  |  |  |

|-------------------------------------|---------|------------------|--|--|--|--|

| Register                            | Address | Register Details |  |  |  |  |

| Config                              | 0x0C006 | page 6           |  |  |  |  |

| Speed Control                       | 0x0C008 | page 6           |  |  |  |  |

| Power Down Control                  | 0x0C00A | page 5           |  |  |  |  |

| Breakpoint                          | 0x0C014 | page 7           |  |  |  |  |

| UART Control                        | 0x0C0E0 | page 7           |  |  |  |  |

| Status                              | 0x0C0E2 | page 8           |  |  |  |  |

| UART Transmit Data                  | 0x0C0E4 | page 8           |  |  |  |  |

| UART Receive Data                   | 0x0C0E4 | page 8           |  |  |  |  |

# PowerDownControl

Offset: 0x0C00A Reset: 0x00 Read/write

| 7 | 6 | 5   | 4    | 3      | 2      | 1       | 0    |  |

|---|---|-----|------|--------|--------|---------|------|--|

|   |   | USB | GPIO | PUD[1] | PUD[0] | Suspend | Halt |  |

In power-down mode, the peripherals are paused and the counters and timers stop incrementing. Specifying Suspend or Halt invokes powerdown mode, although associated features differ as explained below.

| USB                     | Enable restart on USB transition; results in device power up. Must be one of:<br>0—disable restart<br>1—enable restart                                                                                                                                                                                    |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PUD[1:0] <sup>(1)</sup> | Selects the power-up delay. Select one of the following:<br>00—0 ms<br>01—1 ms<br>10—8 ms<br>11—64 ms<br>The power-up delay is the time between the device powering-up and<br>executing the application. A delay in the power-up procedure allows the clock<br>to settle before the application commences |

| Suspend                        | Invoke suspend mode; stops all device clocks to save power. Must be one of:<br>0—no action<br>1—suspend the device<br>Suspend mode terminates with a transition on either USB or the GPIO<br>interrupt lines, if enabled. Device resumption is followed by the delay specified<br>in PUD[1:0] |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Halt                           | Invoke halt mode; stops solely the processor clock. Halt mode terminates with<br>any interrupt. Device resumption is followed by the delay specified in PUD[1:0]                                                                                                                              |

| Note:                          |                                                                                                                                                                                                                                                                                               |

| <ol> <li>Oxford Set</li> </ol> | niconductor advises you not to set this field to anything other than 1 ms.                                                                                                                                                                                                                    |

The processor can be configured to restart if there is activity on any of the four ring indicator pins.

SpeedControl Offset: 0x0C008 Reset: 0x00 **Read/write**

| 7 | 6 | 5 | 4 | 3      | 2      | 1      | 0      |

|---|---|---|---|--------|--------|--------|--------|

|   |   |   |   | SPD[3] | SPD[2] | SPD[1] | SPD[0] |

|   |   |   |   |        |        |        |        |

This register is used to select the operational speed of the OXUSB954. 48 MHz is selected after a power-up or reset.

SPD[3:0] Speed selector control; must be one of: 0000-48 MHz (default) 0001-24 MHz 0010-16 MHz 0011—12 MHz 0100-9.6 MHz 0101---8 MHz 0110-6.86 MHz 0111-6 MHz 1000-5.33 MHz 1001—4.80 MHz 1010-4.36 MHz 1011-4.00 MHz 1100—3.69 MHz 1101—3.42 MHz 1110-3.20 MHz 1111-3.00 MHz

| Config          |     |    |                |    |    |    |    |        |       |    |   |   |   |   |          |         |         |

|-----------------|-----|----|----------------|----|----|----|----|--------|-------|----|---|---|---|---|----------|---------|---------|

| Offset: 0x0C006 |     | 15 | 14             | 13 | 12 | 11 | 10 | 9      | 8     | 7  | 6 | 5 | 4 | 3 | 2<br>ILC | 1<br>C0 | 0<br>CD |

| Reset: 0x02     |     |    |                |    |    |    |    |        |       |    |   |   |   |   |          |         |         |

| Read only       |     |    |                |    |    |    |    |        |       |    |   |   |   |   |          |         |         |

|                 | ILC |    | uston<br>—exte |    |    |    |    | t be c | one o | f: |   |   |   |   |          |         |         |

1-internal custom logic

Div8 BI2

| C0 <sup>(1)</sup> | Clock source selector; must be one of:<br>0—PCLK=X1, RCLK=X1<br>1—PCLK=2/3 X1, RCLK=X1 (default)                                                                                                                                  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CD                | Configuration disable; must be one of:<br>0—configuration by software allowed<br>1—configuration by software disallowed<br>This is a sticky bit used to lock the configuration by writing to it from within the<br>boot PROM code |

Note:

1 X1 input pin must be 12 MHz when using the PLL.

#### Breakpoint

Offset: 0x0C014 Reset: 0x00 Read/write

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

A[15]

A[14]

A[13]

A[12]

A[11]

A[0]

A[9]

A[8]

A[7]

A[6]

A[4]

A[3]

A[2]

A[1]

A[0]

This register holds the breakpoint address. Accessing this register generates an interrupt.

A[15:0] Breakpoint address

#### UARTControl

Offset: 0x0C0E0 Reset: 0x00 Read/write

This register facilitates debugging over the UART serial debugging interface.

Div8

Pre-scaler trigger; used in conjunction with B[2:0]. Must be one of:

0—not used

1—used

If the pre-scaler is used, its effect is to divide the input clock by 8 to generate the UART clock

B[2:0] Baud rate selector; see Table 2 on page 7 for details

| Table 2 Debug UART Baud Rates |                   |                                           |  |  |  |  |

|-------------------------------|-------------------|-------------------------------------------|--|--|--|--|

| B[2:0] Bit Setting            | Baud Rate (Kbaud) | Baud Rate with Div8<br>Pre-Scaler (Kbaud) |  |  |  |  |

| 000                           | 115.2             | 14.4                                      |  |  |  |  |

| 001                           | 57.6              | 7.2                                       |  |  |  |  |

| 010                           | 38.4              | 4.8                                       |  |  |  |  |

| 011                           | 28.8              | 3.6                                       |  |  |  |  |

| 100                           | 19.2              | 2.4                                       |  |  |  |  |

| 101                           | 14.4              | 1.8                                       |  |  |  |  |

| 110                           | 9.6               | 1.2                                       |  |  |  |  |

|                                                          | B[2:0                    | )] Bit Settin             | g                    | Bauc         | l Rate (Kb | aud)       | Baud Rate with Div8<br>Pre-Scaler (Kbaud) |            |            |  |

|----------------------------------------------------------|--------------------------|---------------------------|----------------------|--------------|------------|------------|-------------------------------------------|------------|------------|--|

|                                                          |                          | 111                       |                      |              | 7.2        |            | 110                                       | 0.9        | .suuuj     |  |

|                                                          | <u> </u>                 |                           |                      |              |            |            |                                           |            |            |  |

| RTStatus                                                 |                          | 7                         | 6                    | 5            | 4          | 3          | 2                                         | 1          | 0          |  |

| Offset: 0x0C0E2                                          |                          |                           | 0                    | 5            | 4          | 3          | 2                                         | 1<br>RxF   | TxF        |  |

| Reset: 0x00                                              |                          |                           |                      |              |            |            |                                           |            |            |  |

| Read only                                                |                          |                           |                      |              |            |            |                                           |            |            |  |

|                                                          | This regis<br>interface. | ter facilit               | ates de              | bugging      | g over tł  | ne UAR     | T serial                                  | debugg     | ging       |  |

|                                                          | RxF                      | Receiv<br>0—not<br>1—full | full                 | ull flag; mu | ist be one | of:        |                                           |            |            |  |

|                                                          | TxF                      |                           | nit buffer f<br>full | lag; must    | be one of: |            |                                           |            |            |  |

|                                                          | Note:<br>1 The device    | ce does not su            | ipport error         | detection of | on receive |            |                                           |            |            |  |

| RTTransmit                                               |                          |                           |                      |              |            |            |                                           |            |            |  |

| Offset: 0x0C0E4                                          |                          | 7<br>TR[7]                | 6<br>TR[6]           | 5<br>TR[5]   | 4<br>TR[4] | 3<br>TR[3] | 2<br>TR[2]                                | 1<br>TR[1] | 0<br>TR[0] |  |

| Reset: 0x00<br>Write only                                |                          |                           |                      |              | <u> </u>   | <u> </u>   |                                           |            |            |  |

|                                                          | TR[7:0]                  | UART                      | data for tr          | ansmitting   | )          |            |                                           |            |            |  |

|                                                          |                          |                           |                      |              |            | 1.         | 1                                         | 1          | 0          |  |

| RTReceive                                                |                          | 7                         |                      | 6            |            |            |                                           |            |            |  |

| RTReceive<br>Offset: 0x0C0E4<br>Reset: 0x00<br>Read only |                          | 7<br>RD[7]                | 6<br>RD[6]           | 5<br>RD[5]   | 4<br>RD[4] | 3<br>RD[3] | 2<br>RD[2]                                | RD[1]      | RD[0]      |  |

## **UART Interface**

On the OXUSB954 UART serial ports, individual baud rate selection is made in the appropriate line control register, which includes an optional pre-scaler. For each UART, buffer and control status are monitored in the Status register, while transmit and receive data is written or read from the UART transmit/receive data register. The UART timers are independent of the general-purpose timers. When the receiver buffer transitions to full or the transmit buffer transitions to empty, a UART interrupt is generated on the rising edge. The interrupts are prioritized, with UART 1 having the highest priority. The QuadUARTInterrupt Status register identifies the highest-priority interrupt requiring service, adjusting this information as each interrupt is serviced until no interrupts are outstanding.

Table 3 lists the UART interface registers.

| Table 3 UART Interface Registers |         |                  |  |  |  |  |

|----------------------------------|---------|------------------|--|--|--|--|

| Register                         | Address | Register Details |  |  |  |  |

| UART 1 LineControl               | 0x0BF00 | page 10          |  |  |  |  |

| UART 1 Modem Control             | 0x0BF02 | page 11          |  |  |  |  |

| UART 1 Status                    | 0x0BF04 | page 12          |  |  |  |  |

| UART 1 Transmit Data             | 0x0BF06 | page 13          |  |  |  |  |

| UART 1 Receive Data              | 0x0BF06 | page 13          |  |  |  |  |

| UART 2 LineControl               | 0x0BF10 |                  |  |  |  |  |

| UART 2 Modem Control             | 0x0BF12 |                  |  |  |  |  |

| UART 2 Status                    | 0x0BF14 |                  |  |  |  |  |

| UART 2 Transmit Data             | 0x0BF16 |                  |  |  |  |  |

| UART 2 Receive Data              | 0x0BF16 |                  |  |  |  |  |

| UART 3 LineControl               | 0x0BF20 |                  |  |  |  |  |

| UART 3 Modem Control             | 0x0BF22 |                  |  |  |  |  |

| UART 3 Status                    | 0x0BF24 |                  |  |  |  |  |

| UART 3 Transmit Data             | 0x0BF26 |                  |  |  |  |  |

| UART 3 Receive Data              | 0x0BF26 |                  |  |  |  |  |

| UART 4 LineControl               | 0x0BF30 |                  |  |  |  |  |

| UART 4 Modem Control             | 0x0BF32 |                  |  |  |  |  |

| UART 4 Status                    | 0x0BF34 |                  |  |  |  |  |

| UART 4 Transmit Data             | 0x0BF36 |                  |  |  |  |  |

| UART 4 Receive Data              | 0x0BF36 |                  |  |  |  |  |

| Quad UART Interrupt Status       | 0x0BF40 | page 13          |  |  |  |  |

| Quad UART Enable                 | 0x0BF42 | page 14          |  |  |  |  |

| UART 1 LineControl<br>Offset: 0x0BF00<br>UART 2 LineControl<br>Offset: 0x0BF10<br>UART 3 LineControl<br>Offset: 0x0BF20<br>UART 4LineControl<br>Offset: 0x0BF30<br>Reset: 0x00<br>Read/write |        | 15       14       13       12       11       10       9       8       7       6       5       4       3       2       1       0         Image: Strain Str |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                              | W[1:0] | Word length; must be one of:<br>00—5 bits<br>01—6 bits<br>10—7 bits<br>11—8 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                              | ВК     | Break trigger; must be one of:<br>0—resumes serial output<br>1—stops serial output<br>When a break is in force, serial output becomes inactive and remains so,<br>regardless of transmitter activity, until BK is cleared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                              | SP     | Stick parity; must be one of:<br>0—no action<br>1—send parity as 0 if even, or 1 if odd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                              | OE     | Parity indicator; must be one of:<br>0—even<br>1—odd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                              | PE     | Parity enable; must be one of:<br>0—turn parity off<br>1—turn parity off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                              | S      | Number of stop bits; must be one of:<br>0—1 stop bit<br>1—2 stop bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                              | Div32  | Pre-scaler trigger; used in conjunction with B[2:0]. Must be one of:<br>0—not used<br>1—used<br>If the pre-scaler is used, its effect is to divide the input clock by 32 to generate<br>the UART clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                              | Div8   | Pre-scaler trigger; used in conjunction with B[2:0]. Must be one of:<br>0—not used<br>1—used<br>If the pre-scaler is used, its effect is to divide the input clock by 8 to generate<br>the UART clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                              | B[2:0] | Baud rate selector; see Table 4 on page 11 for details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| B[2:0] Bit Setting | Baud Rate<br>(Kbaud) | Baud Rate with<br>Div32 Pre-Scaler<br>(Kbaud) | Baud Rate with<br>Div8 Pre-Scaler<br>(Kbaud) |  |  |

|--------------------|----------------------|-----------------------------------------------|----------------------------------------------|--|--|

| 000                | 230.4                | 28.8                                          | 4.8                                          |  |  |

| 001                | 115.2                | 14.4                                          | 3.6                                          |  |  |

| 010                | 76.8                 | 9.6                                           | 2.4                                          |  |  |

| 011                | 57.6                 | 7.2                                           | 1.8                                          |  |  |

| 100                | 38.4                 | 4.8                                           | 1.2                                          |  |  |

| 101                | 28.8                 | 3.6                                           | 900 baud                                     |  |  |

| 110                | 19.2                 | 2.4                                           | 600 baud                                     |  |  |

| 111                | 14.4                 | 1.8                                           | 450 baud                                     |  |  |

| UART 1 ModemControl | _ |   |   |   |   |   |          |          |

|---------------------|---|---|---|---|---|---|----------|----------|

| Offset: 0x0BF02     | 7 | 6 | 5 | 4 | 3 | 2 | 1<br>DTR | 0<br>RTS |

| UART 2 ModemControl |   |   |   |   |   |   |          |          |

| Offset: 0x0BF12     |   |   |   |   |   |   |          |          |

| UART 3 ModemControl |   |   |   |   |   |   |          |          |

| Offset: 0x0BF22     |   |   |   |   |   |   |          |          |

| UART 4 ModemControl |   |   |   |   |   |   |          |          |

| Offset: 0x0BF32     |   |   |   |   |   |   |          |          |

| Reset: 0x00         |   |   |   |   |   |   |          |          |

| Read/write          |   |   |   |   |   |   |          |          |

|                     |   |   |   |   |   |   |          |          |

DTR RTS Data terminal ready output Request to send output

| UART 1 StatusRegister<br>Offset: 0x0BF04<br>UART 2 StatusRegister    |      | 15       14       13       12       11       10       9       8       7       6       5       4       3       2       1       0         Image: Constraint of the state of the sta |

|----------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Offset: 0x0BF14<br>UART 3 StatusRegister<br>Offset: 0x0BF24          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| UART 4 StatusRegister<br>Offset: 0x0BF34<br>Reset: 0x00<br>Read only |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                      | FE   | Frame error indicator; must be one of:<br>0—no problems<br>1—frame error detected <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                      | BD   | Break detected indicator; must be one of:<br>0—no problems<br>1—break detected <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                      | OV   | Receiver overrun indicator; must be one of:<br>0—no problems<br>1—receiver overrun error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                      | E    | Data parity error indicator; must be one of:<br>0—no problems<br>1—data parity error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                      | RI   | Ring indicator; must be one of:<br>0—no ring<br>1—ring input detected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                      | DCD  | Data carrier detected indicator; must be one of:<br>0—no data carrier<br>1—data carrier input detected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                      | DSR  | Data set ready indicator; must be one of:<br>0—no data set ready<br>1—data set ready input detected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                      | CTS  | Clear to send indicator; must be one of:<br>0—clear to send<br>1—clear to send input detected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                      | RxF  | Receive buffer full flag; must be one of:<br>0—no problems<br>1—Rx buffer is full <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                      | TxE  | Transmit buffer full flag; must be one of:<br>0—no problems<br>1—Tx buffer is empty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                      | Note |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Note 1 RxF, BD and FE are cleared when the Rx data buffer is read.

| Offset: 0x0BF06       TR(7)       TR(8)       TR(9)       TR(9)       TR(2)       TR(1)       TR(0)         UART 2 TransmitRegister       Offset: 0x0BF16       UART 3 TransmitRegister       Offset: 0x0BF26       UART 4 TransmitRegister       Offset: 0x0BF36       Reset: 0x00       Virite only       TR[7:0]       UART data for transmitting         TR[7:0]       UART data for transmitting         UART 1 ReceiveData         Offset: 0x0BF06       TR[7:0]       UART data for transmitting         TR[7:0]       UART data for transmitting         UART 1 ReceiveData         Offset: 0x0BF06       TR[7:0]       RD[6]       RD[5]       RD[4]       RD[2]       RD[1]       RD[0]         UART 2 ReceiveRegister       Offset: 0x0BF16       UART 3 ReceiveRegister       Offset: 0x0BF26       RD[5]       RD[4]       RD[3]       RD[2]       RD[1]       RD[0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | UART 1 TransmitData     |         |                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------|----------------------------------------------------------------|