## Gas gauge IC with alarm output for handheld applications

Datasheet - production data

#### **Features**

- OptimGauge<sup>TM</sup> algorithm

- 0.25% accuracy battery voltage monitoring

- Coulomb counter and voltage-mode gas gauge operations

- Robust initial open-circuit-voltage (OCV) measurement at power up with debounce delay

- Low battery level alarm output with programmable thresholds

- · Internal temperature sensor

- Battery swap detection

- Low power: 45 μA in power-saving mode, 2 μA max in standby mode

- 1.4 x 2.0 mm 10-bump CSP package

### **Applications**

- Mobile phones, multimedia players, digital cameras

- Portable medical equipment

### **Description**

The STC3115 includes the hardware functions required to implement a low-cost gas gauge for battery monitoring. The STC3115 uses current sensing, Coulomb counting and accurate measurements of the battery voltage to estimate the state-of-charge (SOC) of the battery. An internal temperature sensor simplifies implementation of temperature compensation.

An alarm output signals a low SOC condition and can also indicate low battery voltage. The alarm threshold levels are programmable.

The STC3115 offers advanced features to ensure high performance gas gauging in all application conditions.

Contents STC3115

# **Contents**

| 1 | Block diagram 3    |           |                                                                                                  |      |  |  |  |  |

|---|--------------------|-----------|--------------------------------------------------------------------------------------------------|------|--|--|--|--|

| 2 | Pin a              | assignm   | nent                                                                                             | 4    |  |  |  |  |

| 3 | Abso               | olute ma  | aximum ratings and operating conditions                                                          | 4    |  |  |  |  |

| 4 | Elec               | trical ch | naracteristics                                                                                   | 5    |  |  |  |  |

| 5 | Appl               | ication   | information                                                                                      | 8    |  |  |  |  |

| 6 | Fund               | ctional c | lescription                                                                                      | . 10 |  |  |  |  |

|   | 6.1                | Battery   | monitoring functions                                                                             | . 10 |  |  |  |  |

|   |                    | 6.1.1     | Operating modes                                                                                  | . 10 |  |  |  |  |

|   |                    | 6.1.2     | Battery voltage monitoring                                                                       | . 10 |  |  |  |  |

|   |                    | 6.1.3     | Internal temperature monitoring                                                                  | . 11 |  |  |  |  |

|   |                    | 6.1.4     | Current sensing                                                                                  | . 11 |  |  |  |  |

|   | 6.2                | STC31     | 15 gas gauge architecture                                                                        |      |  |  |  |  |

|   |                    | 6.2.1     | Coulomb counter                                                                                  |      |  |  |  |  |

|   |                    | 6.2.2     | Voltage gas gauge algorithm                                                                      |      |  |  |  |  |

|   |                    | 6.2.3     | Mixed mode gas gauge system                                                                      | . 14 |  |  |  |  |

|   | 6.3                | Low ba    | attery alarm                                                                                     | . 15 |  |  |  |  |

|   | 6.4                |           | -up and battery swap detection                                                                   |      |  |  |  |  |

|   | 6.5                | Improv    | ring accuracy of the initial OCV measurement with the advanced ns of BATD/CD and RSTIO/BATD pins |      |  |  |  |  |

|   |                    | 6.5.1     | BATD and RSTIO pins                                                                              |      |  |  |  |  |

| 7 | l <sup>2</sup> C i | nterface  | <b>)</b>                                                                                         | . 19 |  |  |  |  |

|   | 7.1                | Read a    | and write operations                                                                             | . 19 |  |  |  |  |

|   | 7.2                | Registe   | er map                                                                                           | . 21 |  |  |  |  |

|   |                    | 7.2.1     | Register map                                                                                     |      |  |  |  |  |

|   |                    | 7.2.2     | Register description                                                                             |      |  |  |  |  |

| 8 | Pack               | age info  | ormation                                                                                         | . 25 |  |  |  |  |

|   | 8.1                | Flip Ch   | nip CSP 1.40 x 2.04 mm package information                                                       | . 26 |  |  |  |  |

|   |                    |           |                                                                                                  |      |  |  |  |  |

| STC3115 |                      | Con | tents |

|---------|----------------------|-----|-------|

| 9       | Ordering information | 1   | . 28  |

| 10      | Revision history     |     | . 29  |

Block diagram STC3115

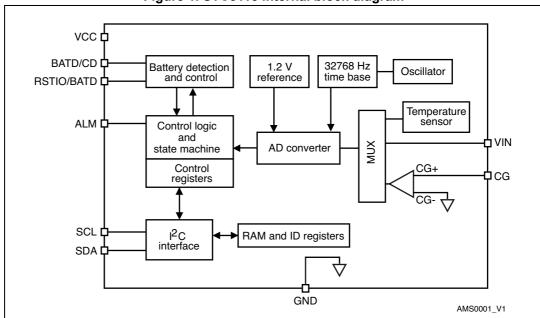

# 1 Block diagram

Figure 1. STC3115 internal block diagram

STC3115 Pin assignment

# 2 Pin assignment

Table 1. STC3115 pin description

| Pin<br>no. | CSP<br>bump | Pin<br>name | Type <sup>(1)</sup> | Function                                                                         |  |  |

|------------|-------------|-------------|---------------------|----------------------------------------------------------------------------------|--|--|

| 1          | A1          | ALM         | I/OD                | Alarm signal output, open drain, external pull-up with resistor                  |  |  |

| 2          | B1          | SDA         | I/OD                | I <sup>2</sup> C serial data                                                     |  |  |

| 3          | C1          | SCL         | I_D                 | I <sup>2</sup> C serial clock                                                    |  |  |

| 4          | D1          | GND         | Ground              | Analog and digital ground                                                        |  |  |

| 5          | D2          | NC          | -                   | NC                                                                               |  |  |

| 6          | D3          | CG          | I_A                 | Current sensing input                                                            |  |  |

| 7          | C3          | RSTIO/BATD  | I/OD                | Reset sense input & reset control output (open drain) or Battery detection input |  |  |

| 8          | B2          | BATD/CD     | I/OA                | Battery charge inhibit (active high output) Battery detection (input)            |  |  |

| 9          | В3          | VCC         | Supply              | Power supply                                                                     |  |  |

| 10         | A3          | VIN         | I_A                 | Battery voltage sensing input                                                    |  |  |

<sup>1.</sup> I = input, 0 = output, OD = open drain, A = analog, D = digital, NC = not connected

# 3 Absolute maximum ratings and operating conditions

Table 2. Absolute maximum ratings

| Symbol             | Parameter                                       | Value      | Unit |

|--------------------|-------------------------------------------------|------------|------|

| V <sub>CCMAX</sub> | Maximum voltage on VCC pin                      | 6          | V    |

| V <sub>IO</sub>    | Voltage on I/O pins                             | -0.3 to 6  | V    |

| T <sub>STG</sub>   | Storage temperature                             | -55 to 150 | °C   |

| T <sub>J</sub>     | Maximum junction temperature                    | 150        | C    |

| ESD                | Electrostatic discharge (HBM: human body model) | 2          | kV   |

Table 3. Operating conditions

| Symbol            | Parameter                                                    | Value      | Unit |

|-------------------|--------------------------------------------------------------|------------|------|

| $V_{CC}$          | Operating supply voltage on V <sub>CC</sub>                  | 2.7 to 4.5 | V    |

| $V_{MIN}$         | Minimum voltage on V <sub>CC</sub> for RAM content retention | 2.0        | V    |

| T <sub>OPER</sub> | Operating free air temperature range                         | -40 to 85  | °C   |

| T <sub>PERF</sub> | Operating free all temperature range                         | -20 to 70  |      |

Electrical characteristics STC3115

# 4 Electrical characteristics

Table 4. Electrical characteristics (2.7 V < V<sub>CC</sub> < 4.5 V, -20  $^{\circ}$ C to 70  $^{\circ}$ C)

| Symbol               | Parameter                             | Conditions                                             | Min | Тур   | Max | Units |

|----------------------|---------------------------------------|--------------------------------------------------------|-----|-------|-----|-------|

| Supply               |                                       |                                                        |     |       |     |       |

| Icc                  | Operating current consumption         | Average value over 4 s in power-saving voltage mode    |     | 45    | 60  |       |

|                      |                                       | Average value over 4 s in mixed mode                   |     |       | 100 | μA    |

| I <sub>STBY</sub>    | Current consumption in standby        | Standby mode, inputs = 0 V                             |     |       | 2   |       |

| I <sub>PDN</sub>     | Current consumption in power-down     | V <sub>CC</sub> < UVLO <sub>TH</sub> ,<br>inputs = 0 V |     |       | 1   |       |

| UVLO <sub>TH</sub>   | Undervoltage threshold                | (V <sub>CC</sub> decreasing)                           | 2.5 | 2.6   | 2.7 | V     |

| UVLO <sub>HYST</sub> | Undervoltage threshold hysteresis     |                                                        |     | 100   |     | mV    |

| POR                  | Power-on reset threshold              | (V <sub>CC</sub> decreasing)                           |     | 2.0   |     | V     |

| Current sensi        | ng                                    |                                                        | •   |       |     |       |

| Vin_gg               | Input voltage range                   |                                                        | -40 |       | +40 | mV    |

| I <sub>IN</sub>      | Input current for CG pin              |                                                        |     |       | 500 | nA    |

| ADC_res              | AD converter granularity              |                                                        |     | 5.88  |     | μV    |

| ADC_offset           | AD converter offset                   | CG = 0 V                                               | -3  |       | 3   | LSB   |

| ADC_time             | AD conversion time                    |                                                        |     | 500   |     | ms    |

| ADC ass              | AD converter gain accuracy at full    | 25 °C                                                  |     | 0.5   |     | %     |

| ADC_acc              | scale (using external sense resistor) | Over temperature range                                 |     |       | 1   | 70    |

| Fosc                 | Internal time base frequency          |                                                        |     | 32768 |     | Hz    |

|                      |                                       | 25 °C, V <sub>CC</sub> = 3.6 V                         |     | 2     |     |       |

| Osc_acc              | Internal time base accuracy           | Over temperature and voltage ranges                    |     |       | 2.5 | %     |

| Cur_res              | Current register LSB value            |                                                        |     | 5.88  |     | μV    |

Table 4. Electrical characteristics (2.7 V <  $V_{CC}$  < 4.5 V, -20 °C to 70 °C) (continued)

| Symbol           | Parameter                                      | Conditions                                          | Min   | Тур  | Max          | Units |

|------------------|------------------------------------------------|-----------------------------------------------------|-------|------|--------------|-------|

| Battery voltage  | e and temperature measurement                  |                                                     |       |      | •            |       |

| Vin_adc          | Input voltage range                            | V <sub>CC</sub> = 4.5 V                             | 0     |      | 4.5          | V     |

| LCD              | LSB value                                      | Voltage measurement                                 |       | 2.20 |              | mV    |

| LSB              | LSB value                                      | Temperature measurement                             |       | 1    |              | °C    |

| ADC_time         | AD conversion time                             |                                                     |       | 250  |              | ms    |

| Volt_acc         | Battery voltage measurement accuracy           | 2.7 V < Vin < 4.5 V,<br>V <sub>CC</sub> = Vin 25 °C | -0.25 |      | +0.25        | %     |

|                  |                                                | Over temperature range                              | -0.5  |      | +0.5         |       |

| Temp_acc         | Internal temperature sensor accuracy           |                                                     | -3    |      | 3            | °C    |

| Digital I/O pins | (SCL, SDA, ALM, RSTIO/BATD)                    |                                                     |       |      |              |       |

| Vih              | Input logic high                               |                                                     | 1.2   |      |              |       |

| Vil              | Input logic low                                |                                                     |       |      | 0.35         | V     |

| Vol              | Output logic low (SDA, ALM, RSTIO)             | IoI = 4 mA                                          |       |      | 0.4          |       |

| BATD/CD pin      |                                                |                                                     |       |      |              |       |

| Vith             | Input threshold voltage                        |                                                     | 1.46  | 1.61 | 1.76         |       |

| Vihyst           | Input voltage hysteresis                       |                                                     |       | 0.1  |              | V     |

| Voh              | Output logic high (charge inhibit mode enable) | loh = 3 mA                                          |       |      | Vbat-<br>0.4 |       |

Electrical characteristics STC3115

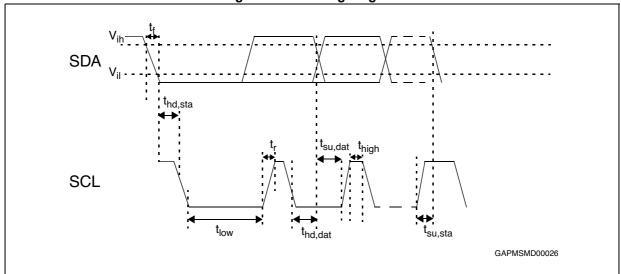

Table 5.  $I^2C$  timing -  $V_{IO}$ = 2.8 V,  $T_{amb}$  = -20 °C to 70 °C (unless otherwise specified)

| Symbol              | Parameter                                        | Min                      | Тур | Max | Unit |

|---------------------|--------------------------------------------------|--------------------------|-----|-----|------|

| F <sub>scl</sub>    | SCL clock frequency                              | 0                        |     | 400 | kHz  |

| t <sub>hd,sta</sub> | Hold time (repeated) START condition             | 0.6                      |     |     |      |

| t <sub>low</sub>    | LOW period of the SCL clock                      | 1.3                      |     |     |      |

| t <sub>high</sub>   | HIGH period of the SCL clock                     | 0.6                      |     |     | μs   |

| t <sub>su,dat</sub> | Setup time for repeated START condition          | 0.6                      |     |     |      |

| t <sub>hd,dat</sub> | Data hold time                                   | 0                        |     | 0.9 |      |

| t <sub>su,dat</sub> | Data setup time                                  | 100                      |     |     | ns   |

| t <sub>r</sub>      | Rise time of both SDA and SCL signals            | 20+<br>0.1C <sub>b</sub> |     | 300 | ns   |

| t <sub>f</sub>      | Fall time of both SDA and SCL signals            | 20+<br>0.1C <sub>b</sub> |     | 300 | ns   |

| t <sub>su,sto</sub> | Setup time for STOP condition                    | 0.6                      |     |     | μs   |

| t <sub>buf</sub>    | Bus free time between a STOP and START condition | 1.3                      |     |     | μs   |

| C <sub>b</sub>      | Capacitive load for each bus line                |                          |     | 400 | pF   |

Figure 2. I<sup>2</sup>C timing diagram

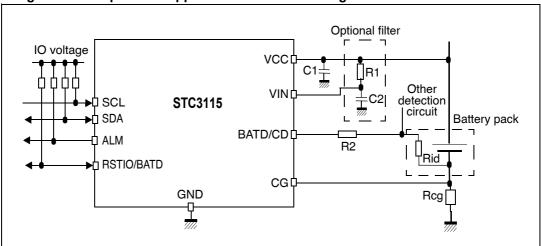

# 5 Application information

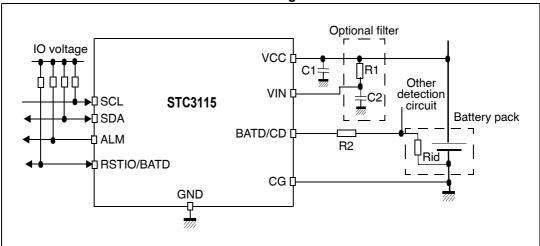

Figure 3. Example of an application schematic using the STC3115 in mixed mode

Table 6. External component list

| Name | Value      | Tolerance | Comments                                          |  |  |

|------|------------|-----------|---------------------------------------------------|--|--|

| Rcg  | 5 to 50 mΩ | 1% to 5%  | Current sense resistor (2% or better recommended) |  |  |

| C1   | 1 μF       |           | Supply decoupling capacitor                       |  |  |

| C2   | 220 nF     |           | Battery voltage input filter (optional)           |  |  |

| R1   | 1 kΩ       |           | Battery voltage input filter (optional)           |  |  |

| R2   | 1 kΩ       |           | Battery detection function                        |  |  |

Figure 4. Example of an application schematic using the STC3115 without current sensing

10/31

Table 7. External component list

| Name | Value  | Comments                                |  |  |  |

|------|--------|-----------------------------------------|--|--|--|

| C1   | 1 μF   | 1 μF Supply decoupling capacitor        |  |  |  |

| C2   | 220 nF | Battery voltage input filter (optional) |  |  |  |

| R1   | 1 kΩ   | Battery voltage input litter (optional) |  |  |  |

| R2   | 1 kΩ   | Battery detection function              |  |  |  |

### 6 Functional description

#### 6.1 Battery monitoring functions

#### 6.1.1 Operating modes

The monitoring functions include the measurement of battery voltage, current, and temperature. A Coulomb counter is available to track the SOC when the battery is charging or discharging at a high rate. A sigma-delta A/D converter is used to measure the voltage, current, and temperature.

The STC3115 can operate in two different modes with different power consumption (see *Table 8*. Mode selection is made by the VMODE bit in register 0 (refer to *Table 13* for register 0 definition).

Table 8. STC3115 operating modes

| VMODE | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| 0     | Mixed mode, Coulomb counter is active, voltage gas gauge runs in parallel            |

| 1     | Voltage gas gauge with power saving Coulomb counter is not used. No current sensing. |

In mixed mode, current is measured continuously (except for a conversion cycle every 4 s and every 16 s seconds for measuring voltage and temperature respectively). This provides the highest accuracy from the gas gauge.

In voltage mode with no current sensing, a voltage conversion is made every 4 s and a temperature conversion every 16 s. This mode provides the lowest power consumption.

It is possible to switch between the two operating modes to get the best accuracy during active periods, and to save power during standby periods while still keeping track of the SOC information.

#### 6.1.2 Battery voltage monitoring

Battery voltage is measured by using one conversion cycle of the A/D converter every 4 s.

The conversion cycle takes  $2^{13}$  = 8192 clock cycles. Using the 32768 Hz internal clock, the conversion cycle time is 250 ms.

The voltage range is 0 to 4.5 V and resolution is 2.20 mV. Accuracy of the voltage measurement is  $\pm 0.5\%$  over the temperature range. This allows accurate SOC information from the battery open-circuit voltage.

The result is stored in the REG\_VOLTAGE register (see Table 12).

#### 6.1.3 Internal temperature monitoring

The chip temperature (close to the battery temperature) is measured using one conversion cycle of the A/D converter every 16 s.

The conversion cycle takes  $2^{13}$  = 8192 clock cycles. Using the 32768 Hz internal clock, the conversion cycle time is 250 ms. Resolution is 1° C and range is -40 to +125 °C.

The result is stored in the REG\_TEMPERATURE register (see *Table 12*).

#### 6.1.4 Current sensing

Voltage drop across the sense resistor is integrated during a conversion period and input to the 14-bit sigma-delta A/D converter.

Using the 32768 Hz internal clock, the conversion cycle time is 500 ms for a 14-bit resolution. The LSB value is 5.88  $\mu$ V. The A/D converter output is in two's complement format.

When a conversion cycle is completed, the result is added to the Coulomb counter accumulator and the number of conversions is incremented in a 16-bit counter.

The current register is updated only after the conversion closest to the voltage conversion (that is: once per 4-s measurement cycle). The result is stored in the REG\_CURRENT register (see *Table 12*).

#### 6.2 STC3115 gas gauge architecture

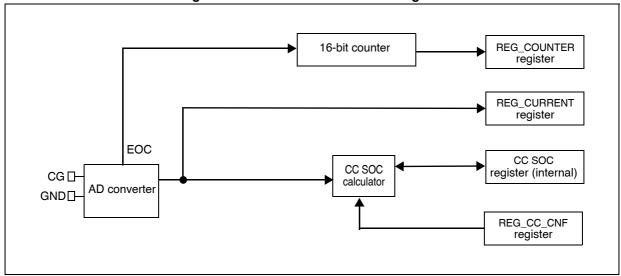

#### 6.2.1 Coulomb counter

The Coulomb counter is used to track the SOC of the battery when the battery is charging or discharging at a high rate. Each current conversion result is accumulated (Coulomb counting) for the calculation of the relative SOC value based on the configuration register.

The system controller can control the Coulomb counter and set and read the SOC register through the I<sup>2</sup>C control registers.

Figure 5. Coulomb counter block diagram

The REG\_CC\_CNF value depends on battery capacity and the current sense resistor. It scales the charge integrated by the sigma delta converter into a percentage value of the battery capacity. The default value is 395 (corresponding to a  $10\text{-m}\Omega$  sense resistor and 1957-mAh battery capacity).

The Coulomb counter is inactive if the VMODE bit is set, this is the default state at power-on-reset (POR) or reset (VMODE bit = 1).

Writing a value to the register REG\_SOC (mixed mode SOC) forces the Coulomb counter gas gauge algorithm to restart from this new SOC value.

REG\_CC\_CNF register is a 16-bit integer value and is calculated as shown in *Equation 1*:

#### **Equation 1**

$REG\_CC\_CNF = Rsense \times Cnom/49.556$

Rsense is in  $m\Omega$  and Cnom is in mAh.

Example: Rsense =  $10 \text{ m}\Omega$ , Cnom = 1650 mAh, REG\_CC\_CNF = 333 mAh

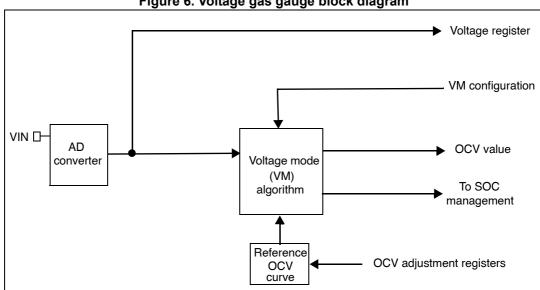

#### 6.2.2 Voltage gas gauge algorithm

No current sensing is needed for the voltage gas gauge. An internal algorithm precisely simulates the dynamic behavior of the battery and provides an estimation of the OCV. The battery SOC is related to the OCV by means of a high-precision reference OCV curve built into the STC3115.

Any change in battery voltage causes the algorithm to track both the OCV and SOC values, taking into account the non-linear characteristics and time constants related to the chemical nature of the Li-Ion and Li-Po batteries.

A single parameter fits the algorithm to a specific battery. The default value provides good results for most battery chemistries used in hand-held applications.

#### Figure 6. Voltage gas gauge block diagram

#### Voltage gas gauge algorithm registers

The REG\_VM\_CNF configuration register is used to configure the parameter used by the algorithm based on battery characteristic. The default value is 321.

The REG\_OCV register holds the estimated OCV value corresponding to the present battery state.

The REG OCVTAB registers are used to adjust the internal OCV table to a given battery type.

The REG VM CNF register is a 12-bit integer value and is calculated from the averaged internal resistance and nominal capacity of the battery as shown in Equation 2:

#### **Equation 2**

$REG_VM_CNF = Ri \times Cnom/977.78$

Ri is in  $m\Omega$  and Cnom is in mAh.

Example: Ri = 190 m $\Omega$ , Cnom =1650 mAh, REG VM CNF = 321

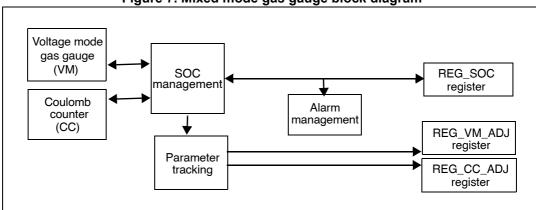

#### 6.2.3 Mixed mode gas gauge system

The STC3115 provides a mixed mode gas gauge using both a Coulomb counter (CC) and a voltage-mode (VM) algorithm to track the SOC of the battery in all conditions with optimum accuracy. The STC3115 directly provides the SOC information.

The Coulomb counter is mainly used when the battery is charging or discharging at a high rate. Each current conversion result is accumulated (Coulomb counting) for the calculation of the relative SOC value based on a configuration register.

The voltage-mode algorithm is used when the application is in low power consumption state.

The STC3115 automatically uses the best method in any given application condition.

However, when the application enters standby mode, the STC3115 can be put in power-saving mode: only the voltage-mode gas gauge stays active, the Coulomb counter is stopped and power consumption is reduced.

Figure 7. Mixed mode gas gauge block diagram

The combination of the CC and VM algorithms provides optimum accuracy under all application conditions. The voltage gas gauge cancels any long-term errors and prevents the SOC drift problem that is commonly found in Coulomb counter only solutions.

Furthermore, the results of the two algorithms are continuously compared and adjustment factors are calculated. This enables the application to track the CC and VM algorithm parameters for long-term accuracy, automatically compensating for battery aging, application condition changes, and temperature effects. Five registers are dedicated to this monitoring:

- REG\_CC\_ADJ and REG\_VM\_ADJ are continuously updated. They are signed, 16-bit, user-adjusted registers with LSB = 1/512 %.

- ACC\_CC\_ADJ and ACC\_VM\_ADJ are updated only when a method switch occurs. They are signed, 16-bit user adjusted accumulators with LSB = 1/512%

- RST\_ACC\_CC\_ADJ and RST\_ACC\_VM\_ADJ bits in the REG\_MODE register are used to clear the associated counter.

#### 6.3 Low battery alarm

The ALM pin provides an alarm signal in case of a low battery condition. The output is an open drain and an external pull-up resistor is needed in the application. Writing the IO0DATA bit to 0 forces the ALM output low; writing the IO0DATA bit to 1 lets the ALM output reflect the battery condition. Reading the IO0DATA bit gives the state of the ALM pin.

When the IO0DATA bit is 1, the ALM pin is driven low if either of the following two conditions is met:

- The battery SOC estimation from the mixed algorithm is less than the programmed threshold (if the alarm function is enabled by the ALM\_ENA bit).

- The battery voltage is less than the programmed low voltage level (if the ALM\_ENA bit is set).

When a low-voltage or low-SOC condition is triggered, the STC3115 drives the ALM pin low and sets the ALM\_VOLT or ALM\_SOC bit in REG\_CTRL.

The ALM pin remains low (even if the conditions disappear) until the software writes the ALM\_VOLT and ALM\_SOC bits to 0 to clear the interrupt.

Clearing the ALM\_VOLT or ALM\_SOC while the corresponding low-voltage or low-SOC condition is still in progress does not generate another interrupt; this condition must disappear first and must be detected again before another interrupt (ALM pin driven low) is generated for this alarm. Another alarm condition, if not yet triggered, can still generate an interrupt.

Usually, the low-SOC alarm occurs first to warn the application of a low battery condition, then if no action is taken and the battery discharges further, the low-voltage alarm signals a nearly-empty battery condition.

At power-up, or when the STC3115 is reset, the SOC and voltage alarms are enabled (ALM\_ENA bit = 1). The ALM pin is high-impedance directly after POR and is driven low if the SOC and/or the voltage is below the default thresholds (1% SOC, 3.00 V voltage), after the first OCV measurement and SOC estimation.

The REG\_SOC\_ALM register holds the relative SOC alarm level in 0.5 % units (0 to 100 %). Default value is 2 (i.e. 1% SOC).

The REG\_ALARM\_VOLTAGE holds the low voltage threshold and can be programmed over the full scale voltage range with 17.60 (2.20 \* 8) mV steps. The default value is 170 (3.00 V).

### 6.4 Power-up and battery swap detection

When the STC3115 is powered up at first battery insertion, an automatic battery voltage measurement cycle is made immediately after startup and debounce delay.

This feature enables the system controller to get the SOC of a newly inserted battery based on the OCV measured just before the system actually starts.

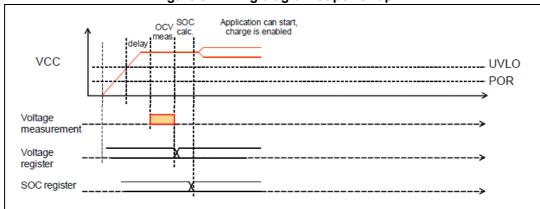

Figure 8. Timing diagram at power-up

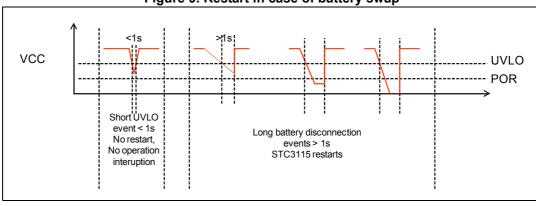

A battery swap is detected when the battery voltage drops below the undervoltage lockout (UVLO) for more than 1 s. The STC3115 restarts when the voltage goes back above UVLO, in the same way as for a power-up sequence.

Such filtering provides robust battery swap detection and prevents restarting in case of short voltage drops. This feature protects the application against high surge currents at low temperatures.

Figure 9. Restart in case of battery swap

Example: When BATD/CD is high (voltage above the 1.61 V threshold) for more than 1 s, a battery swap is detected. The STC3115 restarts when the BATD/CD level returns below the threshold, in the same way as for a power-up sequence.

Using the 1-s filter prevents false battery swap detection if short contact bouncing occurs at the battery terminals due to mechanical vibrations or shocks.

# 6.5 Improving accuracy of the initial OCV measurement with the advanced functions of BATD/CD and RSTIO/BATD pins

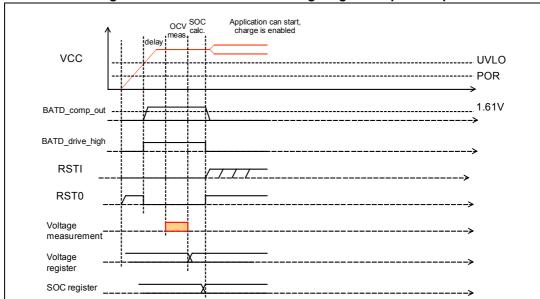

The advanced functions of the BATD/CD and RSTIO/BATD pins provide a way to ensure that the OCV measurement at power-up is not affected by the application startup or by the charger operation. This occurs as follows:

- The BATD/CD pin is driven high to V<sub>CC</sub> voltage which inhibits the charge function (assuming that the BATD/CD signal is connected to disable input of the charger circuit).

- The RSTIO/BATD pin senses the system reset state and if the system reset is active (that is RSTIO/BATD is low), the RSTIO/BATD is kept low until the end of the OCV measurement.

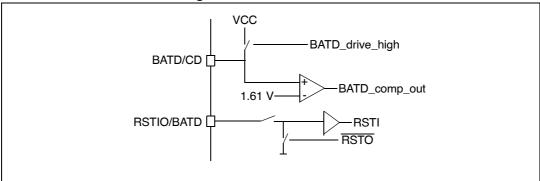

*Figure 10* describes the BATD/CD and RSTIO/BATD operation at power-up. Please refer to the block diagram of *Figure 11* for the RSTI, RSTO, BATD\_comp\_out, and BATD drive high signals.

At the end of the OCV measurement, the BATD/CD and RSTIO/BATD pin are released (high impedance), the application can start and the charger is enabled.

Figure 10. BATD and RSTIO timing diagram at power-up

### 6.5.1 BATD and RSTIO pins

The STC3115 provides platform synchronization signals to provide reliable SOC information in different cases.

The BATD/CD pin senses the presence of the battery independently of the battery voltage and it controls the battery charger to inhibit the charge during the initial OCV measurement.

The RSTIO/BATD pin can be used to delay the platform startup during the first OCV measurement at battery insertion.

**577**

18/31 DocID023755 Rev 4

Figure 11. BATD and RSTIO

The BATD/CD pin used as a battery detector is an analog I/O. The input detection threshold is typically 1.61V.

BATD/CD is also an output connected to  $V_{CC}$  level when active. Otherwise, it is high impedance.

The RSTIO/BATD signal is used to control the application system reset during the initial OCV measurement. The RSTIO/BATD pin is a standard I/O pin with open drain output.

BATD/CD can be connected to the NTC sensor or to the identification resistor of the battery pack. The STC3115 does not provide any biasing voltage or current for the battery detection. An external pull-up resistor or another device has to pull the BATD/CD pin high when the battery is removed.

STC3115

STC3115

Other biasing and/or detection circuit

Battery pack

BATD/CD

TK

BATD/CD

BATD resistor biasing

BATD biasing by external circuitry

Figure 12. BATD/CD pin connection when used as battery detector

I<sup>2</sup>C interface STC3115

### 7 I<sup>2</sup>C interface

### 7.1 Read and write operations

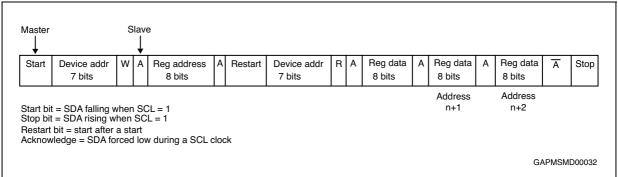

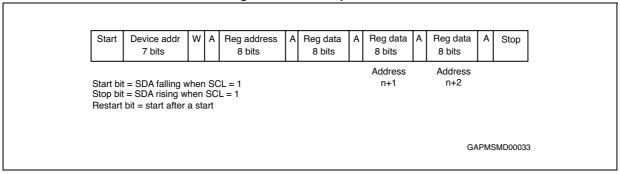

The  $I^2C$  interface is used to control and read the current accumulator and registers. It is compatible with the Philips  $I^2C$  Bus® (version 2.1). It is a slave serial interface with a serial data line (SDA) and a serial clock line (SCL).

- SCL: input clock used to shift data

- SDA: input/output bidirectional data transfers

A filter rejects the potential spikes on the bus data line to preserve data integrity.

The bidirectional data line supports transfers up to 400 Kbit/s (fast mode). The data are shifted to and from the chip on the SDA line, MSB first.

The first bit must be high (START) followed by the 7-bit device address and the read/write control bit. Bits DevADDR0 to DevADDR2 are factory-programmable, the default device address value being 1110 000 (AddrlD0 = AddrlD1 = AddrlD2 = 0). The STC3115 then sends an acknowledge at the end of an 8-bit long sequence. The next eight bits correspond to the register address followed by another acknowledge.

The data field is the last 8-bit long sequence sent, followed by a last acknowledge.

Table 9. Device address format

| bit7 | bit6 | bit5 | bit4 | bit3     | bit2     | bit1     | bit0 |

|------|------|------|------|----------|----------|----------|------|

| 1    | 1    | 1    | 0    | DevADDR2 | DevADDR1 | DevADDR0 | R/W  |

#### Table 10. Register address format

| bit7     | bit6     | bit5     | bit4     | bit3     | bit2     | bit1     | bit0     |

|----------|----------|----------|----------|----------|----------|----------|----------|

| RegADDR7 | RegADDR6 | RegADDR5 | RegADDR4 | RegADDR3 | RegADDR2 | RegADDR1 | RegADDR0 |

#### Table 11. Register data format

| bit7  | bit6  | bit5  | bit4  | bit3  | bit2  | bit1  | bit0  |

|-------|-------|-------|-------|-------|-------|-------|-------|

| DATA7 | DATA6 | DATA5 | DATA4 | DATA3 | DATA2 | DATA1 | DATA0 |

STC3115 I<sup>2</sup>C interface

#### Figure 13. Read operation

#### Figure 14. Write operation

I<sup>2</sup>C interface STC3115

### 7.2 Register map

#### 7.2.1 Register map

The register space provides 28 control registers, 1 read-only register for device ID, 16 read/write RAM working registers reserved for the gas gauge algorithm, and 16 OCV adjustment registers. Mapping of all registers is shown in *Table 12*. Detailed descriptions of registers 0 (REG\_MODE) and 1 (REG\_CTRL) are shown in *Table 13* and *Table 14*. All registers are reset to default values at power-on or reset, and the PORDET bit in register REG\_CTRL is used to indicate the occurrence of a power-on reset.

Table 12. Register map

| Table 12. Register map |                      |      |      |             |                                                  |          |

|------------------------|----------------------|------|------|-------------|--------------------------------------------------|----------|

| Name                   | Address<br>(decimal) | Type | POR  | Soft<br>POR | Description                                      | LSB      |

| Control registers      | 0 to 23              |      |      |             |                                                  |          |

| REG_MODE               | 0                    | R/W  |      |             | Mode register                                    |          |

| REG_CTRL               | 1                    | R/W  |      |             | Control and status register                      |          |

| REG_SOC                | 2-3                  | R/W  |      |             | Gas gauge relative SOC                           | 1/512%   |

| REG_COUNTER            | 4-5                  | R    | 0x00 | 0x00        | Number of conversions (2 bytes)                  |          |

| REG_CURRENT            | 6-7                  | R    | 0x00 | 0x00        | Battery current value (2 bytes)                  | 5.88 μV  |

| REG_VOLTAGE            | 8-9                  | R    | 0x00 | 0x00        | Battery voltage value (2 bytes)                  | 2.2 mV   |

| REG_TEMPERATURE        | 10                   | R    | 0x00 | 0x00        | Temperature data                                 | 1 °C     |

| REG_CC_ADJ_HIGH        | 11                   | R/W  | 0x00 | 0x00        | Coulomb counter adjustment factor                | 1/2%     |

| REG_VM_ADJ_HIGH        | 12                   | R/W  | 0x00 | 0x00        | Voltage mode adjustment factor                   | 1/270    |

| REG_OCV                | 13-14                | R/W  | 0x00 | 0x00        | OCV register (2 bytes)                           | 0.55 mV  |

| REG_CC_CNF             | 15-16                | R/W  | 395  | 395         | Coulomb counter gas gauge configuration          |          |

| REG_VM_CNF             | 17-18                | R/W  | 321  | 321         | Voltage gas gauge algorithm parameter            |          |

| REG_ALARM_SOC          | 19                   | R/W  | 0x02 | 0x02        | SOC alarm level (default = 1%)                   | 1/2%     |

| REG_ALARM_VOLTAGE      | 20                   | R/W  | 0xAA | 0xAA        | Battery low voltage alarm level (default is 3 V) | 17.6 mV  |

| REG_CURRENT_THRES      | 21                   | R/W  | 0x0A | 0x0A        | Current threshold for the relaxation counter     | 47.04 μV |

| REG_RELAX_COUNT        | 22                   | R    | 0x78 | 0x78        | Relaxation counter                               |          |

| REG_RELAX_MAX          | 23                   | R/W  | 0x78 | 0x78        | Relaxation counter max value                     |          |

| REG_ID                 | 24                   | R    | 0x14 | 0x14        | Part type ID = 14h                               |          |

STC3115 I<sup>2</sup>C interface

Table 12. Register map (continued)

| Name                     | Address<br>(decimal) | Туре | POR    | Soft<br>POR | Description                            | LSB     |

|--------------------------|----------------------|------|--------|-------------|----------------------------------------|---------|

| REG_CC_ADJ_LOW           | 25                   | R/W  | 0x00   | 0x00        | Coulomb counter adjustment factor      |         |

| REG_VM_ADJ_LOW           | 26                   | R/W  | 0x00   | 0x00        | Voltage mode adjustment factor         | 1/512%  |

| ACC_CC_ADJ               | 27-28                | R/W  | 0x00   | 0x00        | Coulomb Counter correction accumulator | 1/312/0 |

| ACC_VM_ADJ               | 29-30                | R/W  | 0x00   | 0x00        | Voltage mode correction accumulator    |         |

| RAM registers            | 32 to 47             |      |        |             |                                        |         |

| REG_RAM0                 | 32                   | R/W  | Random | Unchanged   | Working register 0 for gas gauge       |         |

|                          |                      |      |        |             |                                        |         |

| REG_RAM15                | 47                   | R/W  | Random | Unchanged   | Working register 15 for gas gauge      |         |

| OCV adjustment registers |                      |      |        |             |                                        |         |

| REG_OCVTAB               | 48 to 63             | R/W  | 0x00   | 0x00        | OCV adjustment table (16 registers)    | 0.55 mV |

I<sup>2</sup>C interface STC3115

#### 7.2.2 Register description

Values held in consecutive registers (such as the charge value in the REG\_SOC register pair) are stored with high bits in the first register and low bits in the second register. The registers must be read with a single I<sup>2</sup>C access to ensure data integrity. It is possible to read multiple values in one I<sup>2</sup>C access. All values must be consistent.

The SOC data are coded in binary format and the LSB of the low byte is 1/512 %. The battery current is coded in 2's complement format and the LSB value is 5.88 uV. The battery voltage is coded in 2's complement format and the LSB value is 2.20 mV. The temperature is coded in 2's complement format and the LSB value is 1°C.

Table 13. REG\_MODE - address 0

| Name       | Position | Type | Def. | Description                                                                                                                                |

|------------|----------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------|

| VMODE      | 0        | R/W  | 1    | Mixed mode (Coulomb counter active)     Power saving voltage mode                                                                          |

| CLR_VM_ADJ | 1        | R/W  | 0    | Write 1 to clear ACC_VM_ADJ and REG_VM_ADJ. Auto clear bit if GG_RUN = 1                                                                   |

| CLR_CC_ADJ | 2        | R/W  | 0    | Write 1 to clear ACC_CC_ADJ and REG_CC_ADJ<br>Auto clear bit if GG_RUN = 1                                                                 |

| ALM_ENA    | 3        | R/W  | 1    | Alarm function 0: Disabled 1: Enabled                                                                                                      |

| GG_RUN     | 4        | R/W  | 0    | O: Standby mode. Accumulator and counter registers are frozen, gas gauge and battery monitor functions are in standby.  1: Operating mode. |

| FORCE_CC   | 5        | R/W  | 0    | Forces the mixed mode relaxation timer to switch to the Coulomb counter mode. Write 1, self clear to 0 Relaxation counter = 0              |

| FORCE_VM   | 6        | R/W  | 0    | Forces the mixed mode relaxation timer to switch to voltage gas gauge mode. Write 1, self clear to 0 Relaxation counter = Relax_max        |

|            | 7        |      |      | Unused                                                                                                                                     |

STC3115 I<sup>2</sup>C interface

Table 14. REG\_CTRL - address 1

| Name     | Position | Туре | Def. | Description                                                                                                                                                |

|----------|----------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IOODATA  | 0        | R    | Х    | ALM pin status 0 = ALM input is low 1 = ALM input is high                                                                                                  |

| IOUDATA  | 0        | W    | 1    | ALM pin output drive 0 = ALM is forced low 1 = ALM is driven by the alarm conditions                                                                       |

| GG_RST   | 1        | W    | 0    | 0: no effect 1: resets the conversion counter GG_RST is a self-clearing bit.                                                                               |

| GG_VM    | 2        | R    | 0    | Voltage mode active 0 = REG_SOC from Coulomb counter mode 1 = REG_SOC from Voltage mode                                                                    |

| BATFAIL  | 3        | R/W  | 0    | Battery removal or UVLO detection bit. Write 0 to clear (Write 1 is ignored)                                                                               |

|          |          | R    | 1    | Power on reset (POR) detection bit<br>0 = no POR event occurred<br>1 = POR event occurred                                                                  |

| PORDET   | 4        | W    | 0    | Soft reset 0 = release the soft-reset and clear the POR detection bit, 1 = assert the soft-reset and set the POR detection bit. This bit is self clearing. |

| ALM_SOC  | 5        | R/W  | 0    | Set with a low-SOC condition.<br>Cleared by writing 0.                                                                                                     |

| ALM_VOLT | 6        | R/W  | 0    | Set with a low-voltage condition. Cleared by writing 0.                                                                                                    |

|          | 7        |      |      | Unused                                                                                                                                                     |

Package information STC3115

# 8 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

STC3115 Package information

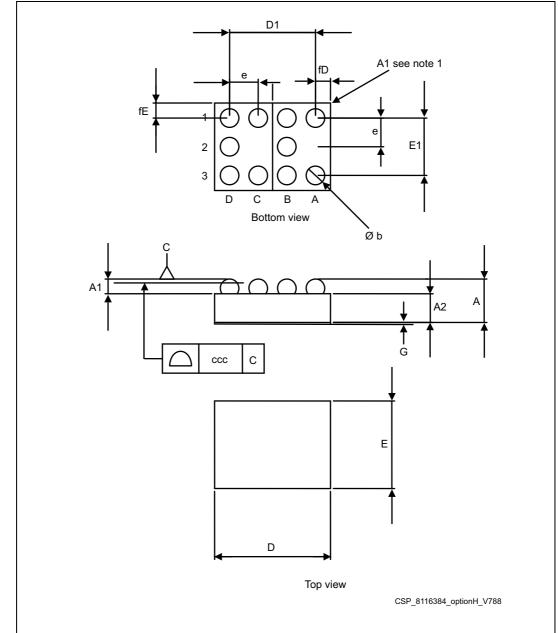

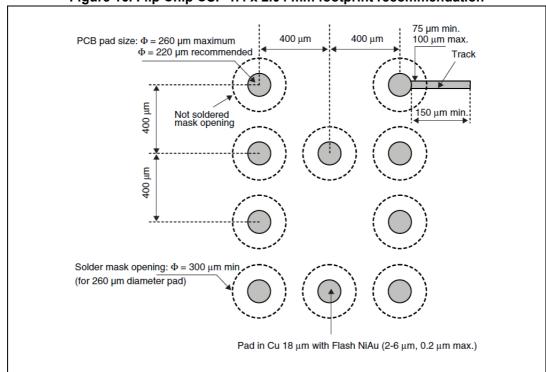

### 8.1 Flip Chip CSP 1.40 x 2.04 mm package information

Figure 15. Flip Chip CSP 1.40 x 2.04 mm package mechanical drawing

<sup>1.</sup> The terminal A1 on the bump side is identified by a distinguishing feature - for instance, by a circular "clear area" typically 0.1 mm in diameter and/or a missing bump.

The terminal A1, on the back side, is identified by a distinguishing feature - for instance, by a circular "clear area" typically 0.2 mm in diameter depending on the die size.

Package information STC3115

Table 15. Flip Chip CSP 1.4 x 2.04 mm package mechanical data

|      | Dimensions |             |       |       |        |       |  |

|------|------------|-------------|-------|-------|--------|-------|--|

| Ref. |            | Millimeters |       |       | Inches |       |  |

|      | Min.       | Тур.        | Max.  | Min.  | Тур.   | Max.  |  |

| Α    | 0.545      | 0.600       | 0.655 | 0.021 | 0.024  | 0.026 |  |

| A1   | 0.165      | 0.200       | 0.235 | 0.006 | 0.008  | 0.009 |  |

| A2   | 0.330      | 0.350       | 0.370 | 0.013 | 0.014  | 0.015 |  |

| b    | 0.220      | 0.260       | 0.300 | 0.009 | 0.010  | 0.012 |  |

| D    | 1.98       | 2.01        | 2.04  | 0.078 | 0.079  | 0.080 |  |

| D1   |            | 1.20        |       |       | 0.047  |       |  |

| E    | 1.34       | 1.37        | 1.40  | 0.053 | 0.054  | 0.055 |  |

| E1   |            | 0.800       |       |       | 0.031  |       |  |

| е    | 0.360      | 0.400       | 0.440 | 0.014 | 0.016  | 0.017 |  |

| fD   | 0.395      | 0.405       | 0.415 | 0.016 | 0.016  | 0.016 |  |

| fE   | 0.275      | 0.285       | 0.295 | 0.011 | 0.011  | 0.012 |  |

| G    |            | 0.050       |       |       | 0.002  |       |  |

| ccc  |            |             | 0.050 |       |        | 0.002 |  |

Figure 16. Flip Chip CSP 1.4 x 2.04 mm footprint recommendation

# 9 Ordering information

Table 16. Order code

| Order code                 | Temperature range | Package | Packing       | Marking |

|----------------------------|-------------------|---------|---------------|---------|

| STC3115IJT <sup>(1)</sup>  | -40 °C to +85 °C  | CSP-12  | Tape and reel | O22     |

| STC3115AIJT <sup>(2)</sup> | -40 C to +65 C    | USF-12  | Tape and Teel | O23     |

<sup>1. 4.35</sup> V battery option

<sup>2. 4.20</sup> V battery option

Revision history STC3115

# 10 Revision history

Table 17. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22-Nov-2012 | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 07-Feb-2013 | 2        | Table 4: added "BATD" and "CD"  Section 6.4: removed option "RSTIO/BATD"  Section 6.5: added "BATD" and "CD"  Section 6.5.1: removed option 2 (BATD/CD is disabled) and 3 (BATD and RSTIO); removed Figure: BATD and RSTIO - option 2, Figure: BATD and RSTIO - option 3, and Figure: RSTIO/BATD pin connection when used as battery detector - option 1 and 2; updated text with respect to BATD/CD.  Removed Section: Register map (Device 0x13) - engineering samples.  Updated Table 12  Removed Table: REG_MODE - address 0 (Device 0x13)  Removed Table: Internal default OCV table and OCV offset registers.  Removed Equation 3.  Replaced Figure 15: Flip Chip CSP 1.40 x 2.04 mm package mechanical drawing.  Updated Table 15: Flip Chip CSP 1.4 x 2.04 mm package mechanical data.  Updated Table 16: Order code |

| 30-Oct-2013 | 3        | Replaced silhouette Updated Features Updated Equation 1 Updated example of Equation 2 Updated disclaimer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 28-Jan-2014 | 4        | Corrected typographical error in document title.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2014 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com