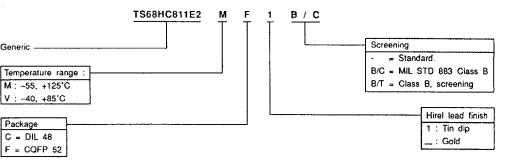

# TS 68HC811E2

# 8-BIT MICROCONTROLLER

#### DESCRIPTION

The TS 68HC811E2 high-density CMOS (HCMOS) microcontroller unit (MCU) contains highly sophisticated on-chip peripheral capabilities. This high-speed and low-power MCU has a multiplexed bus, a nominal bus speed of two megahertz, and the fully static design allows operations at frequencies down to dc. This publication contains condensed information on the MCU.

#### MAIN FEATURES

- 16-bit timer system with four-stage programmable prescaler:

- 4 output compare channels.

- 3 input compare channels,

- 1 input capture or output capture (software selectable).

- Power saving STOP and WAIT modes.

- Synchronous Serial Peripheral Interface (SPI).

- Asynchronous NRZ serial communications interface (SCI).

- B-bit pulse accumulator circuit.

- Bit test and branch instructions.

- Real time interrupt circuit.

- Computer Operating System (COP) watchdog system.

- TS 68HC11 CPU.

- 2K bytes of on-chip EEPROM with block protect for extra security.

- 256 bytes of on-chip static RAM, all saved during standby.

- Eight-channel 8-bit A/D converter (for CQFP only).

- 38 general purpose I/O pins:

- 16 bidirectional input/output (I/O) pins,

- 11 input only pins,

- 11 output only pins.

- Power supply: 5.0 V<sub>DC</sub> ± 10 %.

- Military temperature range: -55 to + 125°C (T<sub>c</sub>).

#### SCREENING / QUALITY

This product is manufactured in full compliance with either:

- MIL-STD-883 (class B).

- DESC 5962-89527.

- or according to TCS standards.

C Suffix **DIL 48** Ceramic side brazed dual in line

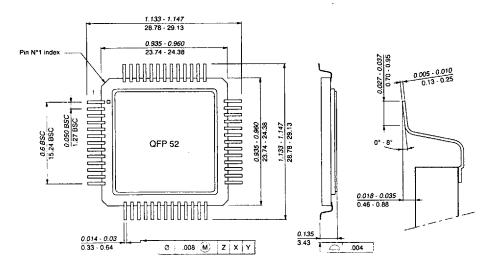

F Suffix CQFP 52 Ceramic quad flat pack

See the ordering information page 54.

Pin connection: see pages 3 and 32.

July 1996

9026872 0004332

### SUMMARY

### A - GENERAL DESCRIPTION

- 1 INTRODUCTION

- 2 SIGNAL DESCRIPTION

# **B - DETAILED SPECIFICATIONS**

- 1 SCOPE

- 2 APPLICABLE DOCUMENTS

- 2.1 MIL-STD 883

#### 3 - REQUIREMENTS

- 3.1 General

- 3.2 Design and construction

- 3.3 Electrical characteristics

- 3.4 Thermal characteristics

- 3.5 Mechanical and environment

- 3.6 Marking

### 4 - QUALITY CONFORMANCE INSPECTION

4.1 DESC / MIL-STD-883

### 5 - ELECTRICAL CHARACTERISTICS

- 5.1 General requirements

- 5.2 Static characteristics

- 5.3 Dynamic (switching) characteristics

- 5.4 Test conditions specific to the device

### 6 - FUNCTIONAL DESCRIPTION

- 6.1 Operating modes

- 6.2 Signal description

- 6.3 Input / output ports

- 6.4 Memory

- 6.5 Registers

- 6.6 Reset

- 6.7 Interrupts 6.8 - Low-power modes

- 6.9 · Programmable timer

- 6.10 Pulse accumulator

- 6.11 EEPROM programming

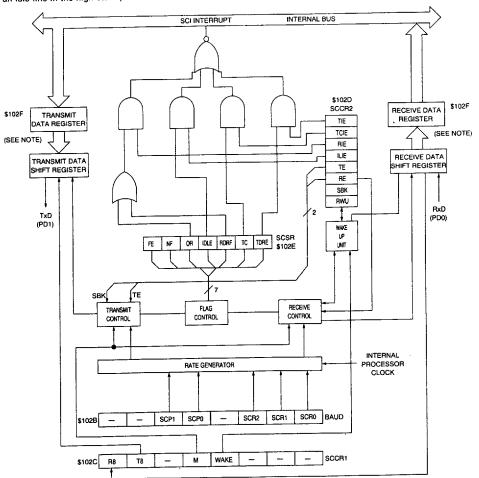

- 6.12 Serial communications interface

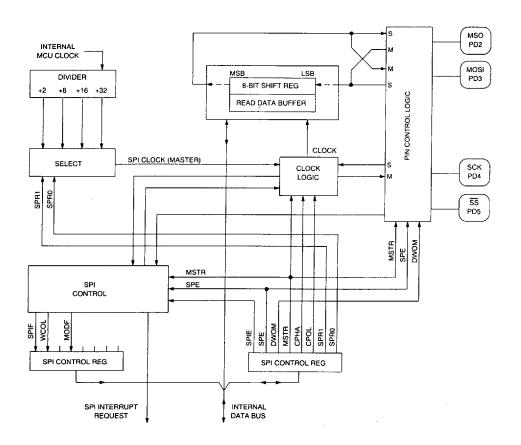

- 6.13 Serial peripheral interface

- 6.14 Analog-to-digital converter

- 6.15 · Instruction set

- 6.16 Addressing modes

#### 7 - PREPARATION FOR DELIVERY

- 7.1 Packaging

- 7.2 · Certificate of compliance

### 8 - HANDLING

### 9 - PACKAGE MECHANICAL DATA

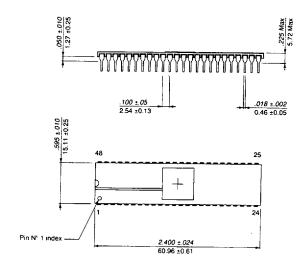

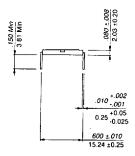

- 9.1 48 Pins Ceramic Dual in Line

- 9.2 52 Pins Ceramic Quad Flat Pack

### 10 - TERMINAL CONNECTIONS

- 10.1 48 Pins Ceramic Dual in Line

- 10.2 52 Pins Ceramic Quad Flat Pack

### 11 - ORDERING INFORMATION

- 11.1 Hi-REL product

- 11.2 Standard product

**--** 9026872 0004333 812 **--**

### **GENERAL DESCRIPTION**

#### 1 - INTRODUCTION

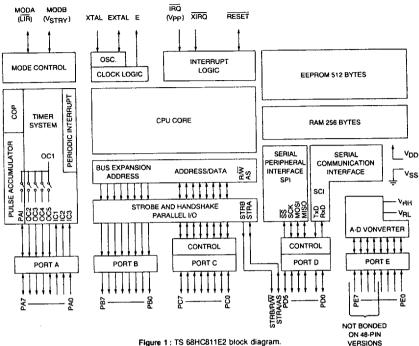

Figure 1 is a block diagram of the TS 68HC811E2.

Figure 1: TS 68HC811E2 block diagram.

### 2 · SIGNAL DESCRIPTION

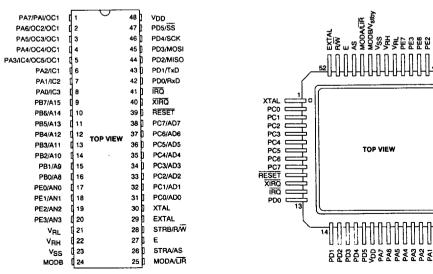

Figure 2.1: Dil 48 terminal designation.

Figure 2.2: CQFP terminal designation.

PE5

D PE1

D PE4

PE0

⊃ PB0

PB1

PB2

PB3

⊃ PB4

PB5

2 P86

2 P87

PAG

### **B - DETAILED SPECIFICATIONS**

#### 1 - SCOPE

This drawing describes the specific requirements for the microcontroller TS 68HC811E2, in compliance with MIL-STD-883 class B or TCS standards.

#### 2 · APPLICABLE DOCUMENTS

#### 2.1 · MIL-STD-883

- 1) MIL-STD-883: test methods and procedures for electronics.

- 2) MIL-PRF-38535 : general specifications for microcircuits.

- 3) DESC Drawing 5962-89527.

#### 3 - REQUIREMENTS

#### 3.1 · General

The microcircuits are in accordance with the applicable document and as specified herein.

#### 3.2 - Design and construction

#### 3.2.1 · Terminal connections

Depending on the package, the terminal connections shall be is shown in Figures 2.1 and 2.2.

### 3.2.2 · Lead material and finish

Lead material and finish shall be any option of MIL-STD-1835.

### 3.2.3 · Package

The macrocircuits are packaged in hermetically sealed ceramic package which is conform to case outlines of MIL-STD-1835 (when defined):

- DIL 48.

- 52 ceramic quad flat pack CQFP.

The precise case outlines are described in § 9.1 and 9.2.

### 3.3 - Electrical characteristics

#### 3.3.1 · Absolute maximum ratings (see Table 1)

#### Table 1

| Symbol            | Parameter             | Test conditions      | Min  | Max   | Unit |

|-------------------|-----------------------|----------------------|------|-------|------|

| Vcc               | Supply voltage        |                      | -0.3 | + 7.0 | ٧    |

| P <sub>dmax</sub> | Max power dissipation |                      |      | 150   | mW   |

|                   | Operating temperature | TS 68HC811E2 CM      | -55  | + 125 | °C   |

| Tcase             |                       | TS 68HC811E2 CV      | - 40 | + 85  | °C   |

| T <sub>stg</sub>  | Storage temperature   |                      | - 55 | + 150 | °C   |

| Тj                | Junction temperature  |                      |      | + 160 | °C   |

| Tleads            | Lead temperature      | Max 5 sec. soldering |      | + 270 | °C   |

#### 3.3.2 - Recommended condition of use

Unless otherwise stated, all voltages are referenced to the reference terminal.

#### Table 2

| Symbol            | Parameter                                           | Min                   | Max                   | Unit |

|-------------------|-----------------------------------------------------|-----------------------|-----------------------|------|

| V <sub>DD</sub>   | Supply voltage                                      | 4.50                  | 5.50                  | ٧    |

| VIL               | Low level input voltage                             | VSS                   | 0.2 × V <sub>DD</sub> | ٧    |

| ViH               | High level input voltage                            | 0.8×V <sub>DD</sub>   | V <sub>DD</sub>       | ٧    |

| T <sub>case</sub> | Operating temperature TS 68HC811E2CM TS 68HC811E2CV | 55<br>40              | + 125<br>+ 85         | °C   |

| Voн               | Maximum high level output voltage                   | V <sub>DD</sub> - 0.1 | VDD                   | ٧    |

| VOL               | Maximum low level output voltage                    | VSS                   | 0.4                   | ٧    |

| fc                | Clock frequency (crystal frequency)                 |                       | 8.4                   | MHz  |

This device contains protective circuitry to protect the input against damage due to high static voltages or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum-rated voltage to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either GND or VCC).

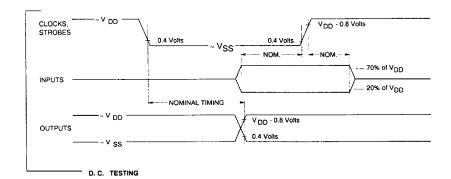

Load network specified in § 5.4.1.

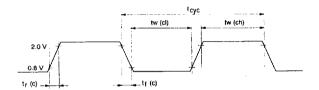

Note: Tirming measurements are referenced to and from a low voltage of 0.8 volt and a high voltage of 20 volts, unless otherwise noted. The voltage swing through this range should start outside, and pass through, the range such that the rise of fall will be linear between 0.8 volt and 20 volts.

Figure 3: Clock input timing diagram.

### 3.4 · Thermal characteristics (at 25°C)

#### Table 3

| Package | Symbol       | Parameter                                                                                      | Value   | Unit       |

|---------|--------------|------------------------------------------------------------------------------------------------|---------|------------|

| DIL 48  | θ JA<br>θ JC | Thermal resistance - Ceramic junction to Ambient Thermal resistance - Ceramic junction to Case | 38<br>5 | °CW<br>°CW |

| CQFP 52 | θ JA<br>θ JC | Thermal resistance - Ceramic junction to Ambient Thermal resistance - Ceramic junction to Case | 31<br>5 | °C/W       |

#### Power considerations.

The average chip-junction temperature, T.J. in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \cdot \theta_{JA}) \tag{1}$$

TA = Ambient Temperature, °C

= Package Thermal Resistance, Junction-to-Ambient, °C/W

= PINT + PI/O PΩ

PINT = ICC x VCC, Watts — Chip Internal Power

PUO = Power Dissipation on Input and Output Pins - User Determined

For most applications PI/O < PINT and can be neglected.

An approximate reliationship between PD and TJ (if PI/O is neglected) is:

$$P_D = K : (T_J + 273)$$

(2)

Solving equations (1) and (2) for K gives:

$$K = P_D \bullet (T_A + 273) + \theta_{JA} \bullet P_D^2$$

(3)

where K is a constant pertaining to the particular part K can be determined from equation (3) by measuring Pp (at equilibrium) for a known TA. Using this value of K, the values of PD and TJ can be obtained by solving equations (1) and (2) iteratively for any value of TA.

The total thermal resistance of a package ( $\theta$ JA) can be separated into two components,  $\theta$ JC and  $\theta$ CA, representing the barrier to heat flow from the semiconductor junction to the package (case), surface (AJC) and from the case to the outside ambient  $(\theta_{CA})$ . These terms are related by the equation:

$$\theta_{JA} = \theta_{JC} + \theta_{CA}$$

(4)

$\theta_{JC}$  is device related and cannot be influenced by the user. However,  $\theta_{CA}$  is user dependent and can be minimized by such thermal management techniques as heat sinks, ambient air cooling and thermal convection. Thus, good thermal management on the part of the user can significantly reduce θCA so that θJA approximately equals θJC. Substitution of θJC for θJA in equation (1) will result in a lower semiconductor junction temperature.

#### 3.5 - Mechanical and environment

The microcircuits shall meet all mechanical environmental requirements of either MIL-STD-883 for class B devices or TCS standards.

#### 3.6 · Marking

The document where are defined the marking are identified in the related reference documents. Each microcircuit are legible and permanently marked with the following information as minimum.

- 3.6.1 · Thomson logo

- 3.6.2 · Manufacturer's part number

- 3.6.3 Class B identification

- 3.6.4 · Date-code of Inspection lot

- 3.6.5 ESD identifier if available

- 3.6.6 · Country of manufacturing

#### 4 - QUALITY CONFORMANCE INSPECTION

### 4.1 - DESC / MIL-STD-883

Is in accordance with MIL-PRF-38535 and method 5005 of MIL-STD-883. Group A and B inspections are performed on each production lot. Group C and D inspection are performed on a periodical basis.

#### 5 - ELECTRICAL CHARACTERISTICS

#### 5.1 · General requirements

All static and dynamic electrical characteristics specified. For inspection purpose, refer to relevant specification:

DESC see § 4.1.

Table 4: Static electrical characteristics for all electrical variants. See § 5.2.

For static characteristics, test methods refer to clause 5.4 hereafter of this specification (Table 5)

For static characteristics, test methods refer to clause 5.4 hereafter of this specification (Table 4).

For dynamic characteristics (Tables 5 to 10), test methods refer to IEC 748-2 method number, where existing.

#### 5.2 - Static characteristics

$V_{CC} = 5.0 \text{ V}_{dc} \pm 10 \text{ %}$ ; GND =  $0 \text{ V}_{dc}$ ;  $T_{c} = -55 \text{ /} + 125 \text{ °C or } -40 \text{ /} + 85 \text{ °C}$ .

## Table 4 - DC electrical characteristics

$V_{DD} = 5.0 \text{ Vdc } \pm 10 \%$ ;  $V_{SS} = 0 \text{ Vdc}$ ;  $A = T_L \text{ to } T_H \text{ (unless otherwise noted)}$

| Symbol           | Parameter                                                                                                    |                                                                | Min                                            | Max                 | Unit             |

|------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------|---------------------|------------------|

| VOH              | Output high voltage<br>ILoad = -0.8 mA, VDD = 4.5 V (Note 1)                                                 | All outputs except RESET XTAL, and MODA                        | V <sub>DD</sub> - 0.8                          |                     | ٧                |

| VOL              | Output low voltage ILoad = 1.6 mA                                                                            | All outputs except XTAL.                                       |                                                | 0.4                 | V                |

| VIH              | Input high voltage                                                                                           |                                                                | 0.7 × V <sub>DD</sub><br>0.8 × V <sub>DD</sub> |                     | V<br>V           |

| VIL              | Input low voltage                                                                                            | All inputs                                                     | Vss                                            | $0.2 \times V_{DD}$ | ٧                |

| loz              | I/O ports, three-state leakage Vin = VIH or VIL                                                              | PA3/PA7, PC0-PC7, PD0-PD5,<br>AS/STRA, MODA/LIR, RESET         |                                                | ±10                 | μΑ               |

| lin              | Input current (Note 2)  Vin = VDD or VSS  Vin = VDD or VSS                                                   | PAO-PA2, IRQ, XIRQ<br>MODB/VSTBY                               |                                                | ±1<br>±10           | μ <b>Α</b><br>μΑ |

| VSB              | RAM standby voltage powerdown                                                                                |                                                                | 4.0                                            | VDD                 | ٧                |

| ISB              | RAM standby current powerdown                                                                                |                                                                |                                                | 20                  | μA               |

| I <sub>DO</sub>  | Total supply current (Note 3) RUN: Single chip Expanded multiplexed WAIT: All peripheral functions shut down |                                                                |                                                | 20<br>30            | mA<br>mA         |

| S <sub>IDD</sub> | Single-chip mode Expanded multiplexed mode STOP: No clocks, single-chip mode                                 |                                                                |                                                | 300                 | mA<br>μA         |

| Cin              | Input capacitance PA0-P PA3, PA7, PC0-PC7, PD0-PC                                                            | PA2, PE0-PE7, ĪRQ, XĪRQ, EXTAL<br>D5, AS/STRA, MODA/LĪR, RESET |                                                | 8<br>14             | pF<br>pF         |

| PD               | Power dissipation                                                                                            | Single-chip mode<br>Expanded-multiplexed mode                  |                                                | 110<br>165          | mW<br>mW         |

Note 1: VOH specification for RESET and MODA is not applicable because they are open-drain pins. VOH specification not applicable to ports C and D in wire-OR mode.

Note 2: See A/D specification for leakage current for port E.

Note 3: All ports configured as inputs, V<sub>IL</sub> ≤ 0.2 V, V<sub>IH</sub> ≥ V<sub>DD</sub> - 0.2 V, no dc loads, EXTAL is driven with a square wave, and t<sub>CVC</sub> = 476.5 ns.

#### 5.3 · Dynamic (switching) characteristics

The limits and values given in this section apply over the full case temperature range  $-55^{\circ}$ C to  $+125^{\circ}$ C and V<sub>CC</sub> in the range 4.5 V to 5.5 V V<sub>IL</sub> = 0.5 V and V<sub>IH</sub> = 2.4 V (See also notes 1 and 2).

Table 5 - Control timing

$V_{DD} = 5.0 \text{ Vdc } \pm 10 \text{ }\%$  ;  $V_{SS} = 0 \text{ Vdc}$  ;  $-40 \leqslant T_{C} \leqslant +85 ^{\circ}\text{C}$  or  $-55 \leqslant T_{C} \leqslant +125 ^{\circ}\text{C}$

| Course at        | Observation.                                                                                                   | 1.0 MHz |     | 2.0 | 2.0 MHz |     | 2.1 MHz |                  |

|------------------|----------------------------------------------------------------------------------------------------------------|---------|-----|-----|---------|-----|---------|------------------|

| Symbol           | Characteristic                                                                                                 | Min     | Max | Min | Max     | Min | Max     | Unit             |

| fo               | Frequency of operation                                                                                         | dc      | 1.0 | dc  | 2.0     | dc  | 2.1     | MHz              |

| t <sub>cyc</sub> | E clock period                                                                                                 | 1000    |     | 500 |         | 476 |         | ns               |

| fXTAL            | Crystal frequency                                                                                              |         | 4.0 |     | 8.0     |     | 8.4     | MHz              |

| 4 fo             | External oscillator frequency                                                                                  |         | 4.0 | dc  | 8.0     | dc  | 8.4     | MHz              |

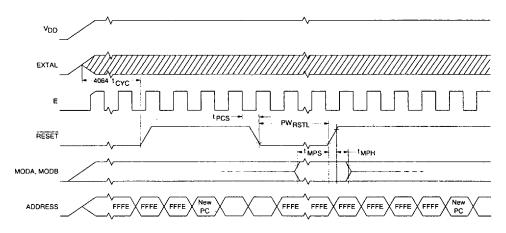

| tpcs             | Processor control setup<br>tpcs = 1/4 t <sub>cyc</sub> - 50 ns<br>Time (see Figures 5, 7 and 8)                | 200     |     | 75  |         | 69  |         | ns               |

| PWRSTL           | Reset input pulse width (Note 1 (To guarantee external and Figure 5) reset vector) (Minimum input time; may be | 8       |     | 8   |         | 8   |         | t <sub>cyc</sub> |

|                  | preempted by internal reset)                                                                                   | 1       |     | 1   |         | 1   |         |                  |

| tMPS             | Mode programming setup time<br>(see Figure 5)                                                                  | 2       |     | 2   |         | 2   |         | t <sub>cyc</sub> |

| <sup>†</sup> MPH | Mode programming hold time<br>(see Figure 5)                                                                   | 0       |     | 0   |         | 0   |         | ns               |

| PWIRQ            | Interrupt pulse width  PWIRQ = t <sub>Cyc</sub> 20 ns  IRQ edge sentive mode (see Figures 6 and 8)             | 2       |     | 2   |         | 2   |         | ns               |

| twrs             | Wait recovery startup time (see Figure 7)                                                                      |         | 4   |     | 4       |     | 4       | t <sub>CyC</sub> |

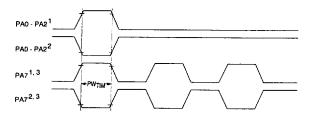

| PWTIM            | Timer pulse width  PWTIM = t <sub>CVC</sub> + 20 ns Input capture, pulse accumulator input (see Figure 4)      | 1020    |     | 520 |         | 496 |         | ns               |

Note: RESET will be recognized during the first clock it is held low. Internal circuitry then drives the pin low for four clock cycles, releases the pin, and samples the pin level two cycles later to determine the source of the interrupt. See RESET, INTERRUPT, AND LOW-POWER MODES for details.

Note 1: Rising sensitive input.

Note 2: Falling edge sensitive input.

Note 3: Maximum pulse accumulator clocking rate is E frequency divided by 2.

Figure 4: Timer inputs timing diagram.

Note: Refer to table 5 for pin states during RESET

Figure 5: POR external reset timing diagram.

Note 1 : Edge sensitive  $\overline{IRQ}$  pin (IRQE bit = 1) Note 2 : Level sensitive  $\overline{IRQ}$  pin (IRQ bit = 0).

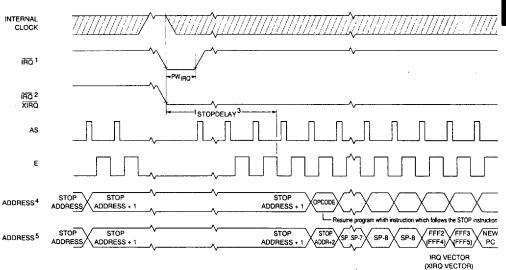

Note 3: tSTOPDELAY = 4064 t<sub>CyC</sub> if DLY bit = 1 or 4 t<sub>CyC</sub> if DLY = 0.

Note 4: XIRQ with X bit in CCR = 1. Note 5: IRQ or (XIRQ with X bit in CCR = 0)

Figure 6: Stop recovery timing diagram.

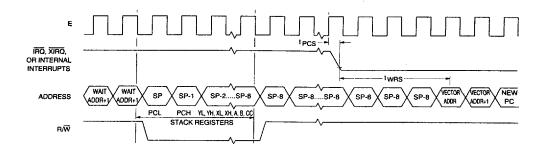

Note 1: Refer to table 5 for pin states during WAIT.

Note 2: RESET will also cause recovery from WAIT.

Figure 7: WAIT recovery from interrupt timing diagram.

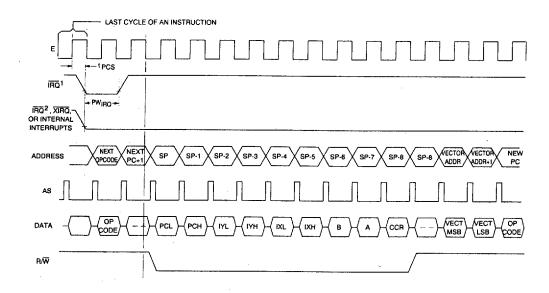

Note 1: Edge sensitive  $\overline{IRQ}$  pin (IRQ bit = 1). Note 2: Level sensitive  $\overline{IRQ}$  pin (IRQE bit = 0).

Figure 8: Interrupt timing diagram.

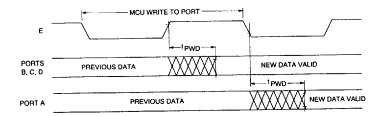

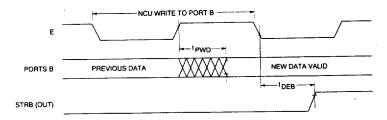

Figure 9: Port write timing diagram.

Note: For non-latched operation of Port C.

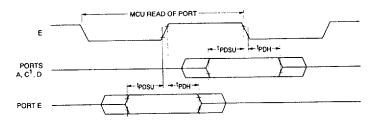

Figure 10: Port read timing diagram.

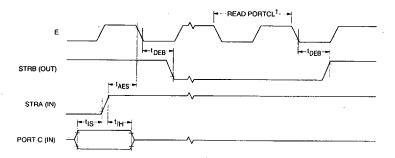

Figure 11: Simple output strobe timing diagram.

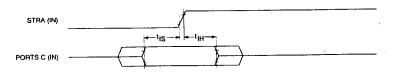

Figure 12: Simple intput strobe timing diagram.

Note 1: After reading PIOC with STAF set. Note 2: Figure shows rising edge STRA (EGA  $\,=\,$  1) and high true STRB (INVB  $\,=\,$  1).

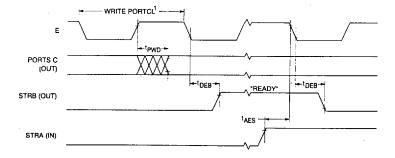

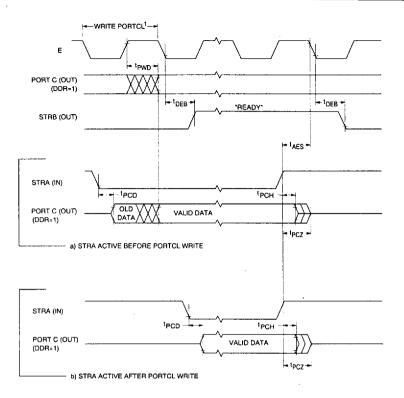

Figure 13: Port C input handshake timing diagram.

Note 1: After reading PIOC with STAF set. Note 2: Figure shows rising edge STRA (EGA = 1) and high true STRB (INVB = 1).

Figure 14: Port C output handshake timing diagram.

Note 1: After reading PIOC with STAF set.

Note 2: Figure shows rising edge STRA (EGA = 1) and high true STRB (INVB = 1).

Figure 15: Three-state variation of output handshake timing diagram (STRA enables output buffer).

Table 6 - Peripheral port timing

$V_{DD} = 5.0 \text{ Vdc } \pm 10 \text{ }\%$  ;  $V_{SS} = 0 \text{ Vdc}$  ;  $-40 \leqslant T_C + 85^{\circ}\text{C}$  or  $-55 \leqslant T_C \leqslant +125^{\circ}\text{C}$

|                   |                                                                                                                                                          | 1.0  | MHz        | 2.0 | 2.0 MHz    |     | 2.1 MHz    |          |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|-----|------------|-----|------------|----------|

| Symbol            | Characteristic                                                                                                                                           | Min  | Max        | Min | Max        | Min | Max        | Unit     |

| fo                | Frequency of operation<br>(E clock frequency)                                                                                                            | 1.0  | 1.0        | 2.0 | 2.0        | 2.1 | 2.1        | MHz      |

| tcyc              | E clock period                                                                                                                                           | 1000 |            | 500 |            | 476 |            | ns       |

| <sup>†</sup> PDSU | Peripheral data setup time<br>(MCU read of ports A, C, D and E)<br>(see Figure 10)                                                                       | 100  |            | 100 |            | 100 |            | ns       |

| tpDH              | Peripheral data hold time<br>(MCU read of ports A, C, D and E)<br>(see Figure 10)                                                                        | 50   |            | 50  |            | 50  |            | ns       |

| tPWD              | Delay time, peripheral data write (See Figures 9, 11, 13 and 14) MCU write to port A MCU writes to ports, B, C and D tpwp = 1/4 t <sub>QVC</sub> + 90 ns |      | 175<br>340 |     | 175<br>215 |     | 175<br>209 | ns<br>ns |

| tis               | Input data setup time (port C)<br>(see Figures 12 and 13)                                                                                                | 60   |            | 60  |            | 60  |            | ns       |

| чн                | Input data hold time (port C)<br>(see Figures 12 and 13)                                                                                                 | 100  |            | 100 |            | 100 |            | ns       |

| <sup>†</sup> DEB  | Delay time, E fall to STRB<br>†DEB = 1/4 t <sub>CVC</sub> + 130 ns<br>(see Figures 11, 13, 14 and 15)                                                    |      | 380        |     | 255        |     | 249        | ns       |

| tAES              | Setup time, STRA asserted to E fall (see Note) (see Figures 13, 14 and 15)                                                                               | 0    |            | 0   |            | 0   |            | ns       |

| tPCD              | Delay time, STRA asserted to port C data output valid (see Figure 15)                                                                                    |      | 100        |     | 100        |     | 100        | ns       |

| <sup>†</sup> PCH  | Hold time, STRA negated to port C data (see Figure 15)                                                                                                   | 10   |            | 10  |            | 10  |            | ns       |

| tPCZ              | Three-state hold time<br>(see Figure 15)                                                                                                                 |      | 150        |     | 150        |     | 150        | ns       |

Note: If this setup time is met, STRB will acknowledge in the next cycle. If it is not met, the respons may be delayed one more cycle.

#### Table 7 - A/D converter characteristics

$V_{DD}$  = 5.0 Vdc ± 10 % ; Vss = 0 Vdc ; -40  $\leq$  Tc +85°C or ~55  $\leq$  Tc  $\leq$  +125°C ; 750 kHz  $\leq$  E  $\leq$  2.1 MHz (unless otherwise noted)

| Characteristic          | Parameter                                                                                                                               | Min       | Max                         | Unit                     |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------------|--------------------------|

| Resolution              | Number of Bits Resolved by the A/D                                                                                                      | 8         |                             | Bits                     |

| Non-linearity           | Maximum deviation from the ideal A/D transfer characteristics                                                                           |           | ± 1/2                       | LSB                      |

| Zero error              | Difference between the output of an ideal and an actual A/D for zero input voltage                                                      |           | ± 1/2                       | LSB                      |

| Full-scale error        | Difference between the output of an ideal and an actual A/D for full-scale input voltage                                                |           | ± 1/2                       | LSB                      |

| Total unadjusted error  | Maximum sum of non-linearity, zero, error, and full-state error (Note 1)                                                                |           | ± 1/2                       | LSB                      |

| Quantization error      | Uncertainty due to converter resolution                                                                                                 |           | ± 1/2                       | LSB                      |

| Absolute accuracy       | Difference between the actual input voltage and the full-scale weighted equivalent of the binary output code, all error source included |           | ± 1                         | LSB                      |

| Conversion range        | Analog input voltage range                                                                                                              | VRL       | VRH                         | ٧                        |

| VRH                     | Maximum analog reference voltage (Note 2)                                                                                               | VRL       | V <sub>DD</sub> + 0.1       | ٧                        |

| V <sub>RL</sub>         | Minimum analog reference voltage (Note 2)                                                                                               | VSS - 0.1 | VRH                         | ٧                        |

| ΔVR                     | Minimum difference between V <sub>RH</sub> and V <sub>RL</sub> (Note 2)                                                                 | 3         |                             | ٧                        |

| Conversion time         | Total time to perform a single analog-to-digital conversion :  a. E clock b. Internal RC oscillator                                     |           | 32<br>t <sub>cyc</sub> + 40 | t <sub>cyc</sub><br>μs   |

| Monotonicity            | Conversion result never decreases with an increase in input voltage and has no missing codes                                            | Guar      | anteed                      |                          |

| Zero-input reading      | Conversion result when Vin = VRL                                                                                                        | 00        |                             | Hex                      |

| Full-scale reading      | Conversion result when V <sub>in</sub> = V <sub>RH</sub>                                                                                |           | FF                          | Hex                      |

| Sample acquisition time | Analog Input acquisition sampling time :  a. E clock b. Internal RC oscillator                                                          | 12        | 12                          | tcyc<br>µs               |

| Input leakage           | Input leakage on A/D pins PE0-PE7 VRL. VRH                                                                                              | ·         | 400<br>1.0                  | Π <b>Α</b><br>μ <b>Α</b> |

Note 1: Source impedances greater than 10 kΩ will adversaly affect accuracy due mainly to input leakage.

Note 2: Performance verified down to 2.5 V  $\Delta V_R$ , but accuracy is tested and guaranteed at  $\Delta V_R = 5 \text{ V} \pm 10 \text{ %}$ .

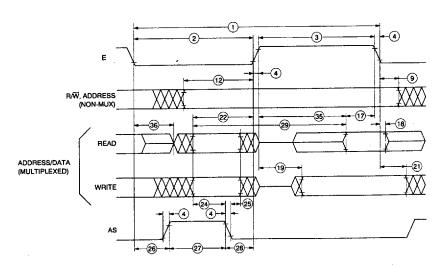

Table 8 - Expansion bus timing

$V_{DD} = 5.0 \; \text{Vdc} \; \pm 10 \; \% \quad ; \quad V_{SS} = 0 \; \text{Vdc} \quad ; \quad -40 \leqslant T_{C} \leqslant \\ +85^{\circ}\text{C or} \; -55 \leqslant T_{C} \leqslant \\ +125^{\circ}\text{C} \cdot \text{See Figure 16} \quad \text{Figure 16} \quad \text{Figu$

|      |                                 |                                                                                                                   | 1.0 MHz 2.0 |       | 0 MHz 2. |     | MHz      | ]   |      |

|------|---------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------|-------|----------|-----|----------|-----|------|

| Num. | Symbol                          | Characteristic                                                                                                    | Min         | Max   | Min      | Max | Min      | Max | Unit |

| •    | fo                              | Frequency of operation (E clock frequency)                                                                        | 1.0         | 1.0   | 2.0      | 2.0 | 2.1      | 2.1 | MHz  |

| 1    | t <sub>cyc</sub>                | Cycle time                                                                                                        | 1000        |       | 500      |     | 476      |     | ns   |

| 2    | PWEL                            | Pulse width, E low<br>PWEL = 1/2 t <sub>cyc</sub> 23 ns                                                           | 477         |       | 227      |     | 215      |     | ns   |

| 3    | PWEH                            | Pulse width, E high<br>PWEH = 1/2 t <sub>cyc</sub> - 28 ns                                                        | 472         |       | 222      |     | 210      |     | ns   |

| 4    | t <sub>r</sub> , t <sub>f</sub> | E and AS rise and fall time                                                                                       |             | 20    | ·        | 20  | <u> </u> | 20  | ns   |

| 9    | <sup>†</sup> AH                 | Address hold time $t_{AH} = 1/8 t_{yc} - 29.5 ns$ (Note 1a)                                                       | 95.5        |       | 33       |     | 30       |     | ns   |

| 12   | †AV                             | Non-muxed address valid time to E rise  t <sub>AV</sub> = PW <sub>EL</sub> - (t <sub>ASD</sub> + 80 ns) (Note 1b) | 281.5       |       | 94       |     | 85       |     | ns   |

| 17   | tDSR                            | Read data setup time                                                                                              | 30          |       | 30       |     | 30       |     | ns   |

| 18   | <sup>†</sup> DHR                | Read data hold time<br>(maxe = t <sub>MAD</sub> )                                                                 | 10          | 145.5 | 10       | 83  | 10       | 80  | ns   |

| 19   | tDDW                            | Write data delay time<br>tDDW = 1/8 t <sub>CyC</sub> + 65.5 ns<br>(Note 1a)                                       |             | 190.5 |          | 128 |          | 125 | ns   |

| 21   | tDHW                            | Write data hold time<br>tDHW = 1/8 t <sub>cyc</sub> - 29.5 ns<br>(Note 1a)                                        | 95.5        |       | 33       |     | 30       |     | ns   |

| 22   | <sup>t</sup> AVM                | Muxed address valid time to E rise tAVM = PWEL - (tASD + 90 ns) (Note 1b)                                         | 271.5       |       | 84       |     | 75       |     | ns   |

| 24   | tASL                            | Muxed address valid time to<br>AS fall<br>tASL = PWASH - 90 ns                                                    | 151         |       | 26       |     | 20       |     | пѕ   |

| 25   | <sup>†</sup> AHL                | Muxed address hold time<br>tAHL = 1/8 t <sub>cyc</sub> - 29.5 ns<br>(Note 1b)                                     | 95.5        |       | 33       |     | 30       |     | ns   |

| 26   | <sup>1</sup> ASD                | Delay time, E to AS rise<br>tASD = 1/8 t <sub>Cyc</sub> - 9.5 ns<br>(Note 1a)                                     | 115.5       |       | 53       |     | 50       |     | ns   |

| 27   | PWASH                           | Pulse width, AS high<br>PWASH = 1/4 t <sub>Cyc</sub> - 29 ns                                                      | 221         |       | 96       |     | 90       |     | ns   |

| 28   | tASED                           | Delay time, AS to E rise<br>tASED = 1/8 t <sub>Cyc</sub> - 9.5 ns<br>(Note 1b)                                    | 115.5       |       | 53       |     | 50       |     | ns   |

| 29   | †ACCA                           | MPU address access time  tacca = tavm + t <sub>r</sub> + PWEH - tDSR (Note 1b)                                    | 733.5       |       | 296      |     | 275      |     | ns   |

| 35   | TACCE                           | MPU access time<br>tACCE = PWEH - tDSR                                                                            |             | 442   |          | 192 |          | 180 | ns   |

### Table 8 - Expansion bus timing (Continued)

$V_{DD} = 5.0 \text{ Vdc } \pm 10 \text{ }\%$  ;  $V_{SS} = 0 \text{ Vdc}$  ;  $-40 \leqslant T_{C} \leqslant +85^{\circ}\text{C}$  or  $-55 \leqslant T_{C} \leqslant +125^{\circ}\text{C} \cdot \text{See}$  Figure 16

|      | Num. Symbol Characteristic |                                                                                      | 1.0 MHz |     | 2.0 MHz |     | 2.1 MHz |     |      |

|------|----------------------------|--------------------------------------------------------------------------------------|---------|-----|---------|-----|---------|-----|------|

| Num. |                            |                                                                                      | Min     | Max | Min     | Max | Min     | Max | Unit |

| 36   | <sup>t</sup> MAD           | Muxed address delay<br>(previous cycle MPU read)<br>tMAD = tASD + 30 ns<br>(Note 1a) | 145.5   |     | 83      |     | 80      |     | ns   |

Note 1: Input clocks with duty cycles other than 50 % will affect bus performance. Timing parameters affected by input clock duty cycle are identified by a and b. To recalculate the approximate bus timing values, substitute the followhole could be seen that by a land b. To recalculate the approximate busing expression in place of 1/8 t<sub>CyC</sub> in the above formulas where applicable; a. (1 - DC) × 1/4 t<sub>CyC</sub> for: (t<sub>DDW</sub>, t<sub>DHW</sub>, t<sub>MAD</sub>) b. DC × 1/4 t<sub>CyC</sub> for: (t<sub>AVM</sub>, t<sub>AHL</sub>, t<sub>ASED</sub>, t<sub>ACCA</sub>) where: DC is the decimal value of duty cycle percentage (high time).

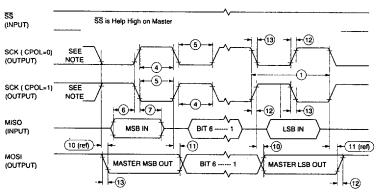

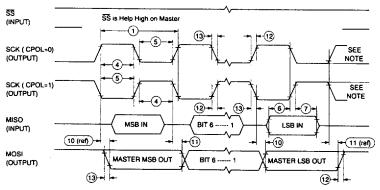

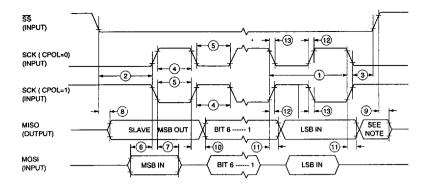

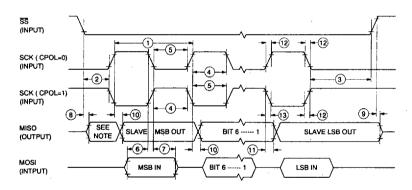

## Table 9 - Serial peripheral interface (SPI) timing

$V_{DD}$  = 5.0 Vdc ± 10 % ;  $V_{SS}$  = 0 Vdc ;  $\sim$  40  $\leqslant$   $T_{C}$  + 85°C or -55  $\leqslant$   $T_{C}$   $\leqslant$  + 125°C · See Figure 17

| Num. | Symbol                                           | Characteristic                                                                                                                                                  | Min        | Max        | Unit                   |

|------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|------------------------|

|      | f <sub>op</sub> (m)<br>f <sub>op</sub> (s)       | Operating frequency<br>Master<br>Slave                                                                                                                          | dc<br>dc   | 0.5<br>2.1 | f <sub>op</sub><br>MHz |

| 1    | t <sub>cyc</sub> (m)<br>t <sub>cyc</sub> (s)     | Cycle time<br>Master<br>Slave                                                                                                                                   | 2.0<br>480 |            | t <sub>cyc</sub>       |

| 2    | t <sub>lead</sub> (m)<br>t <sub>lead</sub> (s)   | Enable lead time<br>Master<br>Slave                                                                                                                             | Note 1 240 | ~          | ns<br>ns               |

| 3    | t <sub>lag</sub> (m)<br>t <sub>lag</sub> (s)     | Enable lag time<br>Master<br>Slave                                                                                                                              | Note 1 240 |            | ns<br>ns               |

| 4    | t <sub>W</sub> (SCKH)m<br>t <sub>W</sub> (SCKH)s | Clock (SCK) high time<br>Master<br>Slave                                                                                                                        | 340<br>190 | -          | ns<br>ns               |

| 5    | tw(SCKL)m                                        | Clock (SCK) low time<br>Master<br>Slave                                                                                                                         | 340<br>190 |            | ns<br>ns               |

| 6    | t <sub>su</sub> (m)<br>t <sub>su</sub> (s)       | Data setup time (inputs) Master Slave                                                                                                                           | 100<br>100 |            | ns<br>ns               |

| 7    | t <sub>h</sub> (m)<br>t <sub>h</sub> (s)         | Data hold time (inputs) Master Slave                                                                                                                            | 100<br>100 |            | ns<br>ns               |

| 8    | ta                                               | Access time (time to data active from high-impedance state) Slave                                                                                               | 0          | - 120      | ns                     |

| 9    | t <sub>dis</sub>                                 | Disable time (hold time to high-impedance state) Stave                                                                                                          |            | 240        | ns                     |

| 10   | tv(s)                                            | Data valid (after enable edge) Note 2                                                                                                                           |            | 240        | ns                     |

| 11   | tho                                              | Data hold time (outputs) (after enable edge)                                                                                                                    | 0          |            | ns                     |

| 12   | t <sub>rm</sub><br>trs                           | Rise time (20 % V <sub>DD</sub> to 70 % V <sub>DD</sub> , C <sub>L</sub> = 200 pF)<br>SPI outputs (SCK, MOSI, and MISO)<br>SPI inputs (SCK, MISO, MOSI, and SS) |            | 100<br>2.0 | ΠS<br>μS               |

9026872 0004348 243

Table 9 - Serial peripheral interface (SPI) timing (Continued)

$V_{DD} = 5.0 \text{ Vdc } \pm 10 \text{ }\%$  ;  $V_{SS} = 0 \text{ Vdc}$  ;  $-40 \leqslant T_{C} \leqslant +85^{\circ}\text{C}$  or  $-55 \leqslant T_{C} \leqslant +125^{\circ}\text{C}$  · See Figure 17

| Num. | Symbol                 | Characteristic                                                                                                       | Min | Max        | Unit     |

|------|------------------------|----------------------------------------------------------------------------------------------------------------------|-----|------------|----------|

| 13   | t <sub>fm</sub><br>tfs | Fall time (70 % Vpp to 20 % Vpp, Ct = 200 pF) SPI outputs (SCK, MOSI, and MISO) SPI inputs (SCK, MISO, MOSI, and SS) |     | 100<br>2.0 | ns<br>μs |

Note 1: Signal production depends on software.

Note 2: Assumes 200 pF load on all SPI pins.

Table 10 - EEPROM characteristics

$V_{DD} = 5.0 \text{ Vdc } \pm 10 \%$  ;  $V_{SS} = 0 \text{ Vdc}$  ;  $T_{C} = 25^{\circ}\text{C}$

|                                | Min                                                                                                                            | Max | Unit                    |                |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------|----------------|

| Programming time (Note 1)      | Under 1.0 MHz with RC oscillator enabled 1.0 to 2.0 MHz with RC oscillator disabled 2.0 MHz (or anytime RC oscillator enabled) |     | 25<br>must use RC<br>25 | ms<br>ms<br>ms |

| Erase time (Note 1)            | Byte, row, and bulk                                                                                                            |     | 10                      | ms             |

| Write/erase endurance (Note 2) |                                                                                                                                |     | 5.000                   | cycles         |

| Data retention (Note 2)        |                                                                                                                                |     | 10                      | years          |

Note 1: The RC oscillator must be enabled (by setting the CSEL bit in the OPTION register) for EEPROM programming and erasure when the E-clock frequency is below 1.0 MHz.

Note 2: See current quarterly reliability monitor report for current failure rate information.

Note: Measurement points shown are 20 % and 70 % VDD-

Figure 16: Expansion bus timing diagram.

■ 9026872 0004349 18T ■

Note: This last clock edge is generated internnally but is not seen at the SCK pin. All timing is shown with respect to 20 %  $V_{DD}$  and 70 %  $V_{DD}$  unless otherwise noted.

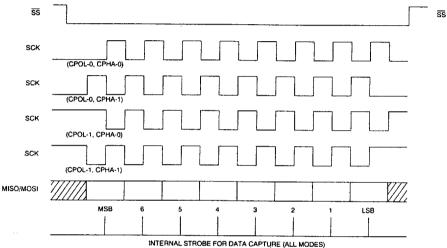

Figure 17a: SPI timing diagrams SPI master timing (CPHA = 0).

Note: This last clock edge is generated internnally but is not seen at the SCK pin.

All timing is shown with respect to 20 % V<sub>DD</sub> and 70 % V<sub>DD</sub> unless otherwise noted.

Figure 17b: SPI timing diagrams SPI master timing (CPHA = 1).

Note: Not defined but normally LSB of character previously transmitted.

All timing is shown with respect to 20 % V<sub>DD</sub> and 70 % V<sub>DD</sub> unless otherwise noted.

Figure 17c: SPI timing diagrams SPI slave timing (CPHA = 0).

Note: Not defined but normally LSB of character previously transmitted.

All timing is shown with respect to 20 % V<sub>DD</sub> and 70 % V<sub>DD</sub> unless otherwise noted.

Figure 17d: SPI timing diagrams SPI slave timing (CPHA = 1).

### 5.4 - Test conditions specific to the device

#### 5.4.1 · Loading network

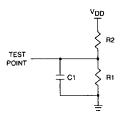

The applicable loading network of Tables 5, 6, 8, 9, refer to the loading network number as shown in Figure 18 below.

Equivalent test load (Note 1)

| Pins                                     | R1     | R2     | C1     |

|------------------------------------------|--------|--------|--------|

| PA3-PA7<br>PB0-PB7<br>PC0-PC7<br>PD0-PD5 | 3.26 K | 2.38 K | 30 pF  |

| E, AS, R/W                               |        |        |        |

| PD1-PD4                                  | 3.26 K | 2.38 K | 200 pF |

Note 1: Full test loads are applied during all ac electrical test and ac timing measurements.

Note 2: During ac timing measurements, inputs are driven to 0.4 volts and  $V_{DD}=0.8$  volts while timing measurements are taken at the 20 % and 70 % of  $V_{DD}$  points.

Figure 18: Test methods.

#### 5.4.2 - Time definitions

The times specified in Tables 5, 6, 8, 9 as dynamic characteristics are defined in Figure 18 above.

#### 6 - FUNCTIONAL DESCRIPTION

#### 6.1 - Operating modes

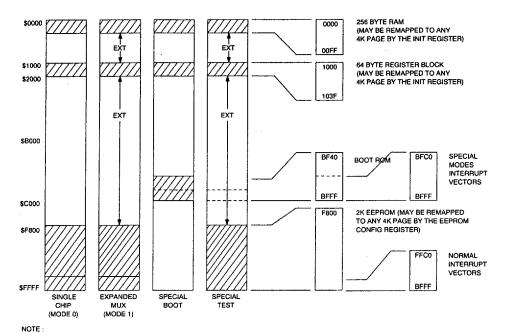

The MCU uses two dedicated pins (MODA and MODB) to select one of two basic operating modes or one of two special operating modes. The basic operating modes are single-chip and expanded-multiplexed; the special operating modes are bootstrap and special test. The following paragraphs describe the different modes.

#### SINGLE-CHIP MODE (MODE0)

In this mode, the MCU functions as a self-contained microcontroller and has no external address or data bus. This mode provides maximum use of the pins for on-chip peripheral functions, and all address and data activity occur within the MCU.

#### **EXPANDED MULTIPLEXED MODE (MODE 1)**

In this mode, the MCU can address up to 64 K bytes of address space. Higher-order address bits are output on the port B pins, and lower-order address bits and the data bus are multipliexed on the port C pins. The AS pin provides the control output used in demultiplexing the loworder address at port C. The R/W pin is used to control the direction of data transfer on port C bus

#### **BOOTSTRAP MODE**

In this mode, all vectors are fetched from the 192-byte on-chip bootloader ROM. This mode is very versatile and can be used for such functions as test and diagnostics on completed modules and for programming the EEPROM. The serial receive logic is initialized by software in the bootloader ROM, which provides program control for the serial communications interface (SCI) baud and word format. In this mode, a special control bit is configured that allows for self-testing of the MCU. This mode can be changed to other modes under program control.

#### TEST MODE

This modes is primarily intended for main production at time of manufacture; however, it may be used to program calibration or personality data into the internal EEPROM. In this mode, a special control bit is configured to permit access to a number of special test control bits. This mode can be changed to other modes under program control.

#### 6.2 · Signal description

#### VDD AND VSS

Power is supplied to the microcontroller using these two pins. VDD is +5 volts (± 0.5 V) power, and VSS is ground.

#### RESET

This active low bidirectional control pin is used as an input to initialize the MCU to a known startup state and as an open-drain output to indicate that an internal failure has been detected in either the clock monitor or the computer operating properly (COP) circuit.

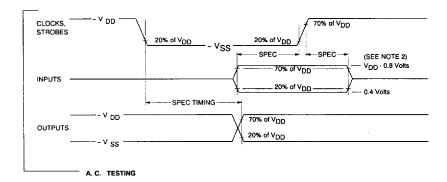

#### XTAL, EXTAL

These pins provide the interface for either a crystal or a CMOS-compatible clock to control the internal clock generator circuitry. The frequency applied shall be four times higher than the desired clock rate. Refer to Figure 19 for crystal and clock connections.

#### Е

This pin provides an output for the internally generated E clock, which can be used for timing reference. The frequency of the E output is one-fourth that of the input frequency at the XTAL and EXTAL pins.

#### IRQ

This pin provides the capability for asynchronously applying interrupts to the MCU. Either negative edge-sensitive or level-sensitive triggering is program selectable. This pin is configured to level-sensitive during reset. An external resistor connected to V<sub>DD</sub> is required on IRQ.

#### XIRO

This pin provides the capability for asynchronously applying non-maskable interrupts to the MCU after a power on reset (POR). During reset, the X bit in the condition code register is set, and analy interrupt is masked until enabled by software. This input is level-sensitive and requires an external pullup resistor to VDD.

### MODA/LIR AND MODB/V<sub>stby</sub>

During reset, these pins are used to control the two basic operating modes and the two special operating modes. The LIR output can be used as an aid in debugging once reset is completed. The open-drain LIR pin goes to an active low during the first E-clock cycle of each instruction and remains low for the duration of that cycle. The mode selections are shown below.

| MODB | MODA | Mode selected        |  |

|------|------|----------------------|--|

| 1    | 0    | Single chip          |  |

| 1    | 1    | Expanded multiplexed |  |

| 0    | 0    | Special bootstrap    |  |

| 0    | 1    | Special test         |  |

### VRL AND VRH

These pins provide the reference voltage for the A/D converter.

### R/W/STRB

This pin provides two different functions, depending on the operating mode. In single-chip mode, the pin provides STRB (output strobe) function; in the expanded multiplexed mode, it provides RW (read-write) function. The RW is used to control the direction of transfers on the external data bus.

One Crystal Driving Two MCUs

Figure 19: Oscillator connections.

#### AS/STRA

This pin provides two different functions depending on the operating mode. In single-chip mode, the pin provides STRA (input strobe) function, and in the expanded-multiplexed mode, it provides AS (address strobe) function. The AS may be used to demultiplex the address and data signals at port C.

# INPUT/OUTPUT LINES (PA0-PA7, PB0-PB7, PC0-PC7, PD0-PD5, PE0-PE7)

These I/O lines are arranged into four 8-bit ports (A, B, C, and E) and one 6-bit port (D). All ports serve more than one purpose depending on the operating mode. Table 11 lists a summary of the pin functions to operating modes. Refer to INPUT/OUTPUT PORTS for additionnal information.

#### 6.3 - Input/output ports

Port functions are controlled by the particular mode selected. In the single-chip mode and bootstrap mode, four ports are configured as parallel I/O data ports and port E can be used for general-purpose static inputs and/or analog-to-digital converter channel inputs. In the expanded-multiplexed mode and test mode, ports B, C, AS, and RW are configured as a memory expansion bus. Table 11 lists the different port signals available. The following paragraphs describe each port.

#### PORT A

In all operating modes, port A may be configured for three input capture funcitons; four output compare functions; and pulse accumulator input (PAI) or a fifth output compare function. Each input capture pin provides for a transitional input, which is used to latch a timer value into the 16-bit input capture register. External devices provide the transitional input, and internal decoders determine which input transition edge is sensed. The output compare pins provide an output whenever a match is made between the value in the free-running counter (in the timer system) and a value loaded into the particular 16-bit output compare register. When port A bit 7 is configured as a PAI, the external input pulses are applied to the pulse accumulator system. The remaining port A lines may be used as general-purpose input or output lines.

■ 9026872 0004354 547 ■

THOMSON-CSF SEMICONDUCTEURS SPECIFIQUES

#### PORT B

In the single-chip mode, all port B pins are general purpose output pins. Port B may also be used in a simple strobed output mode where the STRB pulses each time port B is written. In the expanded-multiplexed mode, all of the port B pins act as high-order (bits 8-15) address output pins.

Table 11 - Port signal functions

| Port-bit                                             | Single-chip and bootstrap mode                                                                                                                  | Expanded multiplexed and special test mode                                                                                  |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| A-0<br>A-1<br>A-2<br>A-3<br>A-4<br>A-5<br>A-6<br>A-7 | PA0/IC3 PA1/IC2 PA2/IC1 PA3/OC5/ and-or OC1 PA4/OC4/ and-or OC1 PA5/OC3/ and-or OC1 PA6/OC2/ and-or OC1 PA7/PAI/ and-or OC1 PA7/PAI/ and-or OC1 | PA0/IC3 PA0/IC2 PA0/IC1 PA3/OC5/ and-or OC1 PA4/OC4/ and-or OC1 PA5/OC3/ and-or OC1 PA6/OC2/ and-or OC1 PA7/PAI/ and-or OC1 |

| B-0<br>B-1<br>B-2<br>B-3<br>B-4<br>B-5<br>B-6<br>B-7 | PB0<br>PB1<br>PB2<br>PB3<br>PB4<br>PB5<br>PB6<br>PB7                                                                                            | A8<br>A9<br>A10<br>A11<br>A12<br>A13<br>A14<br>A15                                                                          |

| C-0<br>C-1<br>C-2<br>C-3<br>C-4<br>C-5<br>C-6<br>C-7 | PC0<br>PC1<br>PC2<br>PC3<br>PC4<br>PC5<br>PC6<br>PC7                                                                                            | A0/D0<br>A1/D1<br>A2/D2<br>A3/D3<br>A4/D4<br>A5/D5<br>A6/D6<br>A7/D7                                                        |

| D-0<br>D-1<br>D-2<br>D-3<br>D-4<br>D-5               | PD0/R × D<br>PD1/T × D<br>PD2/MISO<br>PD3/MOSI<br>PD4/SCK<br>PD5/SS<br>STRA<br>STRB                                                             | PDO/R × D<br>PD1/T × D<br>PD2/MISO<br>PD3/MOSI<br>PD4/SCK<br>PD5/SS<br>AS<br>R/W                                            |

| E-0<br>E-1<br>E-2<br>E-3<br>E-4<br>E-5<br>E-6<br>E-7 | PE0/AN0 PE1/AN1 PE2/AN2 PE3/AN3 PE4/AN4 (see Note) PE5/AN5 (see Note) PE6/AN6 (see Note) PE7/AN7 (see Note)                                     | PE0/AN0 PE1/AN1 PE2/AN2 PE3/AN3 PE4/AN4 (see Note) PE5/AN5 (see Note) PE6/AN6 (see Note) PE7/AN7 (see Note)                 |

#### PORT C

In the single-chip mode, port C pins are general-purpose input/output pins. Port C inputs can be latched by the STRA or may be used in full handshake modes of parallel I/O where the STRA input and STRB output acts as handshake control lines. In the expanded-multiplexed mode, port C pins are configured as multiplexed address/data pins. During the address cycle, bits 0 through 7 of the address are output on PCO-PC7; during the data cycle, bits 0 through 7 (PCO-PC7) are bidirectionnal data pins controlled by the RW signal.

#### PORT D

In all modes, port D bits 0-5 may be used for general purpose I/O or with the serial communications interface (SCI) and serial peripheral interface (SPI) subsystems. Bit 0 is the receive data input, and bit 1 is the transmit data output for the SCI. Bits 2 through 5 are used by the SPI subsystem.

### PORT E

Port E is used for general-purpose static inputs and/or analog-to-digital channel inputs in all operating modes. Port E should not be read as static inputs while an A/D conversion is actually taking place.

### 6.4 · Memory

The memory maps for each mode of operation, a single-chip, expanded-multiplexed, special boot, and special test is shown in Figure 20. In the single-chip mode, the MCU does not generate external addresses. The internal memory locations are shown in the shaded areas, and the contents of the shaded areas are shown on the right side of the diagram. In the expanded-multiplexed mode, the memory locations are basically the same as the single-chip, except the memory locations between s shown in Figure 20. In the single-chip mode, the MCU does not (EXT) are for externally addressed memory and I/O. The special bootstrap mode is similar to the single-chip mode, except the bootstrap program ROM is located at memory locations \$BF40 through \$BFFF. The special test mode is similar to the expanded-multiplexed mode, except the interrupt vectors are at external memory locations.

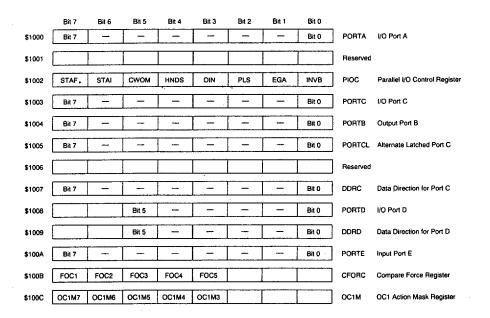

#### 6.5 · Registers

The MCU contains the registers described in the following paragraphs.

#### ACCUMULATOR A AND B

These accumulators are general-purpose 8-bit registers used to hold operands and results of arithmetic calculations or data manipulations. These two accumulators are treated as a single, double-byte accumulator called the D accumulator to some instructions.

| 7  | Α | 0 | 7 | В | 0 |

|----|---|---|---|---|---|

| 15 |   |   | ) |   | 0 |

#### INDEX REGISTER X (IX)

This index register is a 16-bit register used for the indexed addressing mode. It provides a 16-bit value that may be added to an 8-bit offset provided in an instruction to create an effective address. The index register may also be used either as a counter or a temporary storage area.

Note: Either or both the internal RAM and registers can be remapped to any 4K boundary by software.

Figure 20: Memory map.

|        | Bit 7  | Bit 6 | Bit 5    | Bit 4    | Bit 3    | Bit 2      | Bit 1   | Bit 0   |             |                             |

|--------|--------|-------|----------|----------|----------|------------|---------|---------|-------------|-----------------------------|

| \$100D | OC1D7  | OC1D6 | OC1D5    | OC1D4    | OC1D3    |            |         |         | OC1D        | OC1 Action Data Register    |

| \$100E | Bit 15 |       | -        | -        | _        | -          | _       | Bit 8   | TCNT        | Timer Counter Register      |

| \$100F | Bit 7  |       |          |          |          | -          | _       | Bit 0   |             |                             |

| \$1010 | Bit 15 | -     | -        |          |          | I          |         | Bit 8   | TIC1        | Input Capture 1 Register    |

| \$1011 | Bit 7  | _     | _        |          |          |            |         | Bit 0   |             |                             |

| *      |        |       |          |          |          |            |         |         |             |                             |

| \$1012 | Bit 15 |       |          |          |          |            |         | Bit 8   | TIC2        | Input Capture 2 Register    |

| \$1013 | Bit 7  | _     |          |          |          |            |         | Bit 0   |             |                             |

| \$1014 | Bit 15 |       | _        | _        | _        | _          | -       | Bit 8   | TIC3        | Input Capture 3 Register    |

| \$1015 | Bit 7  |       | _        | _        | _        |            | _       | Bit 0   |             |                             |

| \$1016 | Bit 15 |       | <u> </u> |          |          |            | Γ-      | Bit 8   | TOC1        | Output Capture 1 Register   |

| \$1017 | Bit 7  |       |          |          |          |            | _       | Bit 0   | .00.        | Compar Captaro 1 1 Tograto  |

| #1011  |        | t     |          |          |          |            | L       |         |             |                             |

| \$1018 | Bit 15 |       |          |          |          | -          | _       | Bit 8   | TOC2        | Output Capture 2 Register   |

| \$1019 | Bit 7  |       | <i></i>  |          |          | L <u> </u> | L       | Bit 0   |             |                             |

| \$101A | Bit 15 |       | T -      | _        | _        | _          | _       | Bit 8   | тосз        | Output Capture 3 Register   |

| \$101B | Bit 7  |       | -        | -        | -        | _          | _       | Bit 0   |             |                             |

|        |        | 1     | 1        |          | 1        |            |         |         | <b>TOO.</b> | 0.4.10                      |

| \$101C | Bit 15 |       |          |          |          |            |         | Bit 8   | TOC4        | Output Capture 4 Register   |

| \$101D | Bit 7  |       | L        | I        |          | L          | 1       | Dit 0   |             |                             |

| \$101E | Bit 15 | _     | -        |          |          |            | _       | Bit 8   | TOC5        | Output Capture 5 Register/  |

| \$101F | Bit 7  | -     | _        | _        |          | _          | _       | Bit 0   |             | Input Capture 4 Register    |

| \$1020 | OM2    | 0L2   | ОМЗ      | OL3      | OM4      | OL4        | OM5     | 01.5    | TCTL1       | Timer Control Register 1    |

| \$1021 | EDG4B  | EDG4A | EDG1B    | EDG1A    | EDG2B    | EDG2A      | EDG3B   | EDG3A   | TCTL2       | Timer Control Register 2    |

| \$1022 | OC1I   | OC2I  | OC3I     | OC4I     | 14051    | IC1I       | IC2I    | IC3I    | TMSK1       | Timer Interrupt Mask Reg. 1 |

| \$1023 | OC1F   | OC2F  | OC3F     | OC4F     | 1405F    | IC1F       | IC2F    | IC3F    | TFLG1       | Timer Interrupt Flag Reg. 1 |

| \$1024 | TOI    | RTII  | PAOVI    | PAII     |          |            | PR1     | PR0     | TMSK2       | Timer Interrupt Mask Reg. 2 |

| \$1025 | TOF    | RTIF  | PAOVF    | PAIF     |          |            | l       | <u></u> | TFLG2       | Timer Interrupt Flag Reg. 1 |

| \$1026 | DDRA7  | PAEN  | PAMOD    | PEDGE    | DDRA3    | 14/05      | RTR1    | RTR0    | PACTL       | Pulse Accum. Control Reg    |

| \$1027 | Bit 7  | _     | <u> </u> | <u> </u> | <u> </u> | <u> </u>   |         | Bit 0   | PACNT       | Pulse Accum. Count Reg.     |

| \$1028 | SPIE   | SPE   | DWOM     | MSTR     | CPOL     | СРНА       | SPR1    | SPR0    | SPCR        | SPI Control Register        |

| \$1029 | SPIF   | WCOL  |          | MODE     | I        | <u> </u>   | <u></u> |         | SPSR        | SPI Status Register         |

| \$102A | Bit 7  |       | ] -      | <u> </u> | I. –     | -          | -       | Bit 0   | SPDR        | SPI Data Register           |

| \$1028 | TCLR   |       | SCP1     | SCP0     | RCKB     | SCR2       | SCR1    | SCR0    | BAUD        | SCI Baud Rate Control       |

| \$102C | R8     | T8    | T        | М        | WAKE     |            |         |         | SCCR1       | SCI Control Register 1      |

|        |        |       |          |          |          |            |         |         |             |                             |

|                          | Bit 7 | Bit 6    | Bit 5 | Bit 4    | Bit 3    | Bit 2 | Bit 1    | Bit 0 |          |                                     |

|--------------------------|-------|----------|-------|----------|----------|-------|----------|-------|----------|-------------------------------------|

| \$102D                   | TIE   | TCIE     | RIE   | ILIE     | TE       | RE    | RWU      | SBK   | SCCR2    | SCI Control Register                |

| \$102E                   | TORE  | TC       | RDRF  | IDLE     | ОЯ       | NF    | FE       | l     | SCCR     | SCI Status Register                 |

| \$102F                   | Bit 7 | _        | _     | _        | _        | _     | _        | Bit 0 | SCDR     | SCI Data (Read RDR,<br>Write TDR)   |

| \$1030                   | CCF   | L        | SCAN  | MULT     | CD       | CC    | СВ       | CA    | ADCTL    | A/D Control Register                |

| \$1031                   | Bit 7 |          |       | <u> </u> | <u> </u> |       |          | Bit 0 | ADR1     | A/D Result Register 1               |

| \$1032                   | Bit 7 | _        |       | -        | _        | _     | <u> </u> | Bit 0 | ADR2     | A/D Result Register 2               |

| \$1033                   | Bit 7 | <u> </u> |       | _        | <u> </u> |       | _        | Bit 0 | ADR3     | A/D Result Register 3               |

| \$1034                   | Bit 7 |          |       |          | _        |       | <u> </u> | Bit 0 | ADR4     | A/D Result Register 4               |

| \$1035                   |       |          |       | PTCON    | BPRT3    | BPRT2 | BPRT1    | врято | ADR1     | EEPROM Block Protect Reg.           |

| \$1036<br>Thru<br>\$1038 |       |          |       |          |          |       |          |       | Reserved |                                     |

| \$1039                   | ADPU  | CSEL     | IRGE  | DLY      | CME      |       | CR1      | CR0   | OPTION   | System Configuration Options        |

| \$103A                   | Bit 7 | _        | _     | _        | _        | _     |          | Bit 0 | COPRST   | Arm/Reset COP Timer<br>Circuitry    |

| \$103B                   | ODD   | EVEN     | _     | BYTE     | ROW      | ERASE | EELAT    | EEPGM | PPROG    | EEPROM Prog. Control Reg.           |

| \$103C                   | RBOOT | SMOD     | MDA   | IRV      | PSEL3    | PSEL2 | PSEL1    | PSEL0 | HPRIO    | Highest Priority I-Bit Int and Misc |

| \$103D                   | RAM3  | RAM2     | RAM1  | RAMO     | REG3     | REG2  | REG1     | REG0  | INIT     | RAM and I/O Mapping Reg.            |

| \$103E                   | TILOP |          | OCCR  | CBYP     | DISR     | FCM   | FCOP     | TCON  | TEST1    | Factory TEST Control Register       |

|                          |       |          |       |          |          |       |          |       |          |                                     |

| \$103F                   | EE3   | EE2      | EE1   | EE0      | 1        | NOCOP | 1        | EEON  | CONFIG   | COP, ROM, and EEPROM<br>Enables.    |

### INDEX REGISTER Y (IY)

This index register is an 16-bit register used for the indexed addressing mode similar to the IX register; however, most instructions using the IY register are two-byte opcodes and require an extra byte of machine code and an extra cycle of execution time. The index register may also be used as a counter or a temporary storage area.

### PROGRAM COUNTER (PC)

The program counter is a 16-bit register that contains the address of the next byte to be fetched.

| 15 | PC | 0 |

|----|----|---|

|    |    |   |

#### STACK POINTER (SP)

The stack pointer is a 16-bit register that contains the address of the next free location on the stack. The stack is configured as a sequence of last in first out read/write registers, which allow important data to be stored during interrupts and subroutine calls. Each time a new byte is added to the stack, the SP is incremented; each time a byte is removed, the SP is incremented. The address contained in the SP also indicates the location at which the accumulators A and B registers IX and IY can be stored during certain instructions.

| 15 | SP | 0 |

|----|----|---|

|    |    |   |

#### CONDITION CODE REGISTER (CCR)

The condition code register is an 8-bit register in which each bit is used to indicate the results of the instruction just executed. These bits can be individually tested by a program, and specific actions can be taken as a result of their state. Each bit is explained in the following paragraphs.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| s | х | н | _ | N | Z | > | С |

Carry/Borrow (C)

When set, this bit indicates that a carry of borrow out of the arithmetic logical unit (ALU) occurred during the last arithmetic operation. This bit is also affected during shift and rotate instructions.

### Overflow (V)

The overflow bit is set if an arithmetic overflow occured as a result of the operation; otherwise the V bit is cleared.

Zero (Z) When set, this bit indicates that the result of the last arithmetic, logical, or data manipulation was zero.

### Negative (N)

When set, this bit indicates that the result of the last arithmetic, logical, or data manipulation was negative (the MSB of the result is a logic one).

Interrupt (I) This bit is set either by hardware or program instruction to disable (mask) all maskable interrupt sources (both external and internal).

Half carry (H) This bit is set during ADD, ABA, and ADC operations to indicate that a carry occured between bits 3 and 4. This bit is mainly useful in BCD calculations.

#### X interrupt mask (X)

This mask bit is set only by hardware (reset or XIRQ) and is cleared only by program instruction (TAP or RTI).

### Stop disable (S)

This bit, under program control, is set to disable the STOP instruction, and is cleared to enable the STOP instruction. The STOP instructions is treated as no operation (NOP) if the S bit is set.

#### 6.6 · Resets

The MCU can be reset four ways:

- an active low input to the RESET pin,

- a power-on reset function.

- a computer operating properly (COP) watchdog-timer timeout and,

- a clock monitor failure.

The RESET input consists mainly of a Schmitt trigger that senses the RESET line logic level.

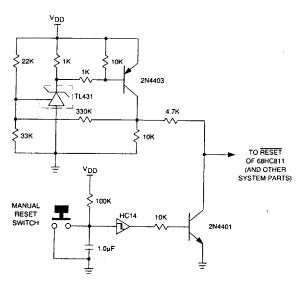

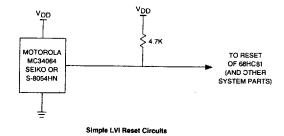

### RESET PIN

To request an external reset, the RESET pin must be held low for eight E<sub>CVC</sub> (two E<sub>CVC</sub> if no distinction is needed between internal and external resets). To prevent the EEPROM contents from being corrupted during power transitions, the reset line should be held low while VDD is below its minimum operating level. A low voltage inhibit (LVI) circuit is required to protect EEPROM from corruption as shown in Figure 21.

### POWER-ON RESET (POR)

Power-on reset occurs when a positive transition is detected on VDD. The power-on reset is used strictly for power turn-on conditions and should not be used to detect any drop in the power supply voltage. If the external RESET pin is low at the end of the power-on delay time, the processor remains in the reset condition until RESET goes high.

#### COMPUTER OPERATING PROPERLY (COP) RESET

The MCU contains a watchdog timer that automatically times out if not reset within a specific time by a program reset sequence. If the COP watchdog timer is allowed to timeout, a reset is generated, which drives the RESET pin low to reset the MCU and the external system.

The COP reset function can be enabled or disabled by setting the control bit in an EEPROM cell of the system configuration register. Once programmed, this control bit remains set (or cleared) even when no power is applied, and the COP function is enabled or disabled independent of resident software. Protected control bits (CR1 and CR0), in the configuration options register, allow the user to select one of four COP timeout rates. Table 12 shows the relationship between CR1 and CR0 and the COP timeout period for various system clock frequencies.

#### CLOCK MONITOR RESET

The MCU contains a clock monitor circuit which measures the E clock input frequency. If the E clock input rate is above 200 kHz, then the clock monitor does not generate a MCU reset. If the E clock signal is lost or its frequency falls below 10 kHz, then a MCU reset is generated, and the RESET pin is driven low to reset the external system.

The clock monitor reset can be enabled or disabled by a read-write control bit (CME) in the system configuration options re-

Reset Circuit with LVI and RC Delay

Figure 21: Typical LVI reset circuits.

Table 12 · COP timeout periods

| CR1 | CR0 | E/2 <sup>15</sup><br>divided<br>by | XTAL = 2 <sup>23</sup><br>timeout<br>- 1/ + 15.6 ms | XTAL = 8.0 MHz<br>timeout<br>- 0/ + 16.4 ms | XTAL = 4.9152 MHz<br>timeout<br>- 0/ + 26.7 ms | XTAL = 4.0 MHz<br>timeout<br>0/ + 32.8 ms | XTAL = 3.6864 MHz<br>timeout<br>0/ + 35.6 ms |

|-----|-----|------------------------------------|-----------------------------------------------------|---------------------------------------------|------------------------------------------------|-------------------------------------------|----------------------------------------------|

| 0   | 0   | 1                                  | 15.625 ms                                           | 16.384 ms                                   | 26.667 ms                                      | 32.768 ms                                 | 35.556 ms                                    |

| 0   | 1   | 4                                  | 62.5 ms                                             | 65.536 ms                                   | 106.67 ms                                      | 131.07 ms                                 | 142.22 ms                                    |

| 1   | 0   | 16                                 | 250 ms                                              | 262.14 ms                                   | 426.67 ms                                      | 524.29 ms                                 | 568.89 ms                                    |

| 1   | 1   | 64                                 | 1 s                                                 | 1.049 s                                     | 1.707 s                                        | 2.1 s                                     | 2.276 s                                      |

|     |     | -                                  | 0.4.141.1-                                          | 0.0 MH                                      | 4 0000 1411                                    | 4.0.141.1-                                | 004.0.1.1-                                   |

E = 2.1 MHz 2.0 MHz 1.2288 MHz 1.0 MHz 921.6 kHz

#### 6.7 · Interrupts

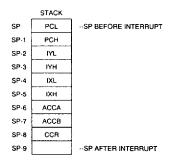

There are seventeen hardware and one software interrupts (excluding reset type interrupts) that can be generated from all the possible sources. These interrupts can be divided into two categories, maskable and non-maskable. Fifteen of the interrupts can be masked with the condition code register I bit. All the on-chip interrupts are individually maskable by local control bits. The software interrupt is non-maskable. The external input to the XIRO pin is considered a non-maskable interrupt because, once enabled, it cannot be masked by software; however, it is masked during reset and upon receipt of an interrupt at the XIRO pin. The last interrupt, illegal opcode, is also a non-maskable interrupt. Table 13 provides a list of each interrupt, its vector location in ROM, and the actual condition code and control bits that mask it. Figure 22 shows the interrupt stacking order.

#### SOFTWARE INTERRUPT (SWI)

The SWI is executed the same as any other instruction and will take precedence over interrupts only if the other interrupts are masked (I and X bits in the CCR set). The SWI execution is similar to the maskable interrupts such as setting the I bit, CPU registers are stacked, etc.

Figure 22: Stacking order.

Note: The SWI instruction cannot be fetched as long as another interrupt is pending execution. However, once fetched, no other interrupt can be honored until the first instruction in the SWI service routine is completed.

Table 13 - Interrupt vector assignments

| Vector<br>address                 | Interrupt source                                                                                                                               | CC<br>register mask | Local mask                        |